不同氮化镓蚀刻技术的比较

电子说

描述

引言

GaN作为宽禁带III-V族化合物半导体最近被深入研究。为了实现GaN基器件的良好性能,GaN的处理技术至关重要。目前英思特已经尝试了许多GaN蚀刻方法,大部分GaN刻蚀是通过等离子体刻蚀来完成的,等离子体刻蚀的缺点是容易产生离子诱导损伤,难以获得光滑的刻蚀侧壁。为了更好地控制表面粗糙度,英思特采用了一种称为数字蚀刻的技术来进行研究。

实验与讨论

我们通过选择PEC二元GaN刻蚀方法来进行实验。利用二元蚀刻不需要复杂的设备,可实现更好的控制和精度。同时利用二元蚀刻不需要外部刺激以及任何的电极,可以在室温或更高的温度下进行实验。

所有的GaN膜通过LED掩模图案化,然后使用电子束沉积在GaN膜上沉积200 nm的Ni层,在Ni剥离之后,图案化的GaN膜留下Ni和GaN膜。

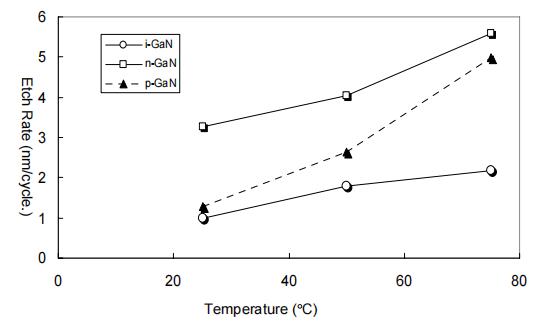

图1显示了本征GaN、n-GaN和p- GaN膜的蚀刻速率(单位为nm/周期)与从室温25℃到75℃的温度的关系。循环总共需要大约2分钟(30秒的5% K2S2O8,30秒的KOH和60秒的去离子水)。我们通过数字化的方式完成了实验,并且没有使用可以明显提高化学反应速率的紫外线光源,因此,基本上我们有意降低GaN蚀刻速率,以实现更好的表面粗糙度控制。

图1:氮化镓K2S2O8/KOH二元蚀刻速率与温度的关系

图1:氮化镓K2S2O8/KOH二元蚀刻速率与温度的关系

在75℃下,由于更高的掺杂浓度和更多的缺陷,这使得初始蚀刻更容易开始,因此n-GaN具有最高的蚀刻速。

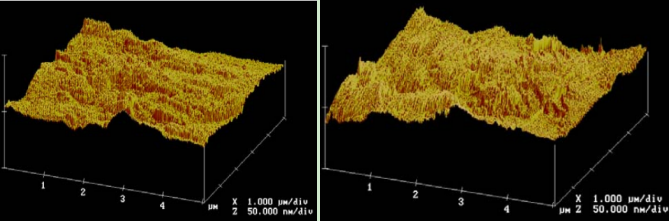

我们还使用AFM进行表面拓扑和粗糙度测量。GaN二元蚀刻前后的GaN表面的AFM图像如图2所示。

图2

图2

上面的AFM图像是通过接触式AFM扫描拍摄的,X和Y方向是扫描区域,Z方向显示表面粗糙度。AFM图像显示在GaN蚀刻之前GaN表面是光滑的,这证明了我们的MOCVD生长技术。

结论

英思特分别在室温和高温下,通过蓝宝石上的本征GaN、n掺杂GaN和p掺杂GaN膜上成功地进行了K2S2O8/KOH二元蚀刻。我们通过实验发现蚀刻速率相对较低,但是可以高精度地控制表面粗糙度。

审核编辑:汤梓红

-

氮化镓发展评估2017-08-15 0

-

MACOM:硅基氮化镓器件成本优势2017-09-04 0

-

什么是氮化镓(GaN)?2019-07-31 0

-

氮化镓GaN 来到我们身边竟如此的快2020-03-18 0

-

什么是氮化镓技术2020-10-27 0

-

氮化镓功率半导体技术解析2021-03-09 0

-

氮化镓充电器2021-09-14 0

-

什么是氮化镓功率芯片?2023-06-15 0

-

谁发明了氮化镓功率芯片?2023-06-15 0

-

氮化镓功率芯片的优势2023-06-15 0

-

为什么氮化镓(GaN)很重要?2023-06-15 0

-

氮化镓: 历史与未来2023-06-15 0

-

为什么氮化镓比硅更好?2023-06-15 0

-

有关氮化镓半导体的常见错误观念2023-06-25 0

全部0条评论

快来发表一下你的评论吧 !