高速信号知识科普

描述

网络搜索“什么是高速信号”或“低速信号与高速信号的区别”,出现一堆解释,例如:

(a)信号是否为高速信号,取决于两个因素:信号频率和信号传输路径长度(信号线长度)。

(b)通常认为如果数字逻辑电路的频率达到或者超过45MHz~50MHz,而且工作在这个频率之上的电路已经占到了整个电子系统一定的份量(比如说1/3),就称为高速电路。

(c)如果是站在传输延时的角度考虑的话,上升时间<1/6的传输延时,就是高频信号!

甚至,这条都是错误的结论...人云亦云,并未抓住为何要区分高速信号或高速电路的问题根源,即系统能够接受多大的反射噪声。

其实,如果以常见的“信号上升时间的1/6”将信号衡量为高速信号的话,总结下来有以下三种不同的表达形式,如下:

1)当传输线延时大于信号上升时间的1/6时,

2)当传输线长度大于传输有效长度的1/6时,

3)当传输线长度大于信号有效波长的1/6时,认为是高速信号,需要进行信号完整性设计;否则认为是低速信号。

直觉来看,这三种衡量标准之间应存在某种联系,下文是推导过程。

1. 信号在空气中的传播速度

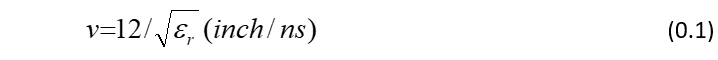

电信号(电磁波,电磁场)在空气中的传播速度等于光速,即3*10^8 m/s = 186 280 mile/s = 12 inch/ns;电磁波在其他物质中的传播速度等于光速除以该物质相对介电常数(dielectric constant)的平方根,即

2. 信号传输延迟时间 / 信号延时 / 传输延时

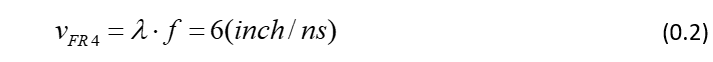

常用的PCB板材FR4的相对介电常数约为4,因而电信号在FR4基材中的传输速度为常量,如下:

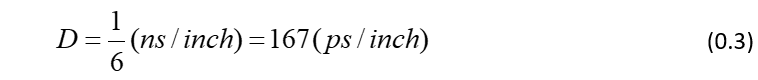

那么,每单位长度的传输延时为

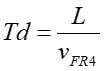

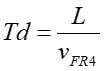

所以,电信号传输延迟时间就是传输线长度除以传输速度,即

上式表明,传输延时 Td 由传输线长度 L 决定,二者成正比关系(因为电信号在PCB中的传输速度为常量)。

说明:上述 公式 (0.2) 描述的电信号的传输速度,指PCB内层走线(即带状线stripline)的传输速度,内层走线周围的相对介电常数是均匀的;而PCB外层走线(即微带线microstrip)周围的介质,一半是空气,一半是PCB板材,微带线所处的介质的有效介电常数比PCB板材的相对介电常数小,因而传输速度更快,同时传输延时更小。所以,在做PCB走线等长时,最终目标是延时相等;若分别使PCB外层和内层做走线等长,则需更近一步地将微带线和带状线的传输延时不同考虑进去。

3. 时钟频率与上升时间的关系

由于时钟频率越高(信号周期越小),留给信号切换的时间(即信号的上升时间)必然变小,通常定义上升时间为从低电平上升到高电平的10%-90%这段时间。

多数高速数字系统中,分配的上升时间约为时钟周期的1/10,二者关系如下:

所以,对于固定的器件来说,信号上升时间是器件的固有参数 ,比如MOS管的上升时间和下降时间等都会在Datasheet中给出。

4. 临界长度 / 关键长度

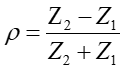

信号反射量的大小用反射系数来衡量,定义为  ,信号传输方向是从

,信号传输方向是从  阻抗到

阻抗到  阻抗。

阻抗。

从反射系数的定义可以得出以下三个结论:

①阻抗变化越大,反射系数的绝对值越大;

②信号从小阻抗传输到大阻抗时,反射系数为正;

③从大阻抗传输到小阻抗时,反射系数为负。

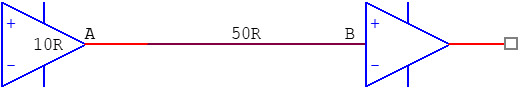

通常情况下,驱动端输出阻抗较小(10Ω左右),普通信号的标准传输线阻抗是50Ω,接收端的输入阻抗较大。所以,如下图所示,A点的反射系数为( 10 - 50 ) / ( 10 + 50 ) = (-2/3),B点的反射系数接近于1。

以驱动端1.2V高电平为例,驱动端输出阻抗为10Ω(输出点定义为A点),传输线阻抗为50Ω,接收端(定义为B点)开路(即  无穷大),则反射系数为1,这意味着驱动端的信号将被100%反射;驱动端由低到高的信号跳变,A点的发射电平为1.2 * 50 / ( 10 + 50 ) = 1V,到达接收端B点后将全部返回。那么,B点的振铃幅度会在2V左右;但是,何时小于2V,何时大于2V呢?

无穷大),则反射系数为1,这意味着驱动端的信号将被100%反射;驱动端由低到高的信号跳变,A点的发射电平为1.2 * 50 / ( 10 + 50 ) = 1V,到达接收端B点后将全部返回。那么,B点的振铃幅度会在2V左右;但是,何时小于2V,何时大于2V呢?

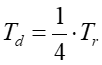

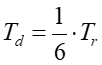

当信号在走线上的传输时间和返回时间之和2Td,小于信号的上升时间Tr,即  。将公式(0.4)(

。将公式(0.4)(  )代入到

)代入到  中,可以解得:

中,可以解得:

这时,B点振铃幅度最大值小于2V(可如此理解,当 时,驱动端电压由低到高的信号跳变,高电平并未达到1.2V,A点发射电平将小于1V,所以B点发射幅度最大值将小于2V)。

当  (即

(即  (0.7))时,B点振铃幅度最大值可达2V,但不能保持。

(0.7))时,B点振铃幅度最大值可达2V,但不能保持。

当  (即

(即  (0.8) )时,B点振铃幅度最大值可达2V,且能保持(可如此理解,当

(0.8) )时,B点振铃幅度最大值可达2V,且能保持(可如此理解,当  时,驱动端A点发射电平已经稳定在1V,所以B点的振铃幅度能够保持在2V)。

时,驱动端A点发射电平已经稳定在1V,所以B点的振铃幅度能够保持在2V)。

振铃幅度越大,说明过冲(包括上冲和下冲)现象越严重。[见《信号完整性揭秘:于博士SI设计手记》4.15节]

所以,当信号在传输线上的延迟时间 Td (即信号传输延迟时间)等于信号上升时间 Tr 的1/2时, 对应的传输线长度称为临界长度或关键长度,即公式(0.7);它是接收端振铃幅度达到最大值的临界点(此时的反射噪声也是最大的)。走线长度小于关键长度的,可称为“短走线”,可以不做传输线阻抗匹配;走线长度大于关键长度的,可称为“长走线”,需要考虑传输线阻抗匹配。

有以下推论:

(1) 阻抗突变产生反射;反射在发射端和接收端反复进行,形成振铃现象。

(2) 接收端振铃幅度的大小,与传输线长度(或传输延时)以及信号上升时间有关,最终由传输线长度决定。

反射(reflection)和振铃(ringing)都是信号完整性问题。那么如何减小反射或减小振铃幅度的大小呢?首先,保证传输线阻抗均匀或阻抗稳定;其次,尽量缩短传输线长度。

5. 保证传输线阻抗均匀或阻抗稳定的方法(略)

说明:传输线阻抗均匀和传输线阻抗稳定,两个概念的侧重点不同。

阻抗均匀的根本,是要保证PCB中信号传输介质的相对介电常数均匀;比如FR4基板材料是环氧树脂和玻璃纤维的混合物,环氧树脂的相对介电常数约为3.0,玻璃纤维的相对介电常数约为6.0,根据二者比例不同,FR4基板材料的相对介电常数在3.5 - 4.5之间,多数情况下是4。若FR4混合物材料不均匀,将导致走线周围介质阻抗不均匀,引起EMI。

传输线阻抗稳定,指信号“发射端 - 传输线 - 接收端”这条链路的阻抗要相等;若不相等,一般要做传输线阻抗匹配或者说走线端接,即加入源端串联端接电阻或终端并联端接阻容等。

6. 反射噪声大小与传输线延时(或传输线长度,trace lengths)大小呈正比关系

如前文所述,当信号传输延迟时间 Td 小于信号上升时间 Tr 的1/2(即  )时,接收端B点的振铃幅度将小于2V(在驱动端高电平为1.2V,驱动端输出阻抗为10R,传输线阻抗为50R条件下)。

)时,接收端B点的振铃幅度将小于2V(在驱动端高电平为1.2V,驱动端输出阻抗为10R,传输线阻抗为50R条件下)。

实际仿真表明(参考《信号完整性揭秘:于博士SI设计手记》相关内容):

当  (将公式(0.4)(

(将公式(0.4)(  )代入,有

)代入,有  (0.9) )时,反射噪声约为25%;

(0.9) )时,反射噪声约为25%;

当  (即

(即  (0.10))时,反射噪声约为12.5%;

(0.10))时,反射噪声约为12.5%;

当  (即

(即  (0.11))时,反射噪声约为5%。

(0.11))时,反射噪声约为5%。

所以,反射噪声大小与传输线延时 Td 或传输线长度 L 呈正比关系。 即传输线的延时越大或线长越长,反射噪声也越大;传输线延时越小或线长越短,反射噪声越小,振铃幅度越小。

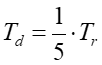

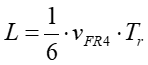

由此引出基于传输线延时的高速信号衡量标准的第一种表述是:

认为当传输线延时 Td 大于信号上升时间 Tr 的1/4(或1/5或1/6)时,

即  时是高速信号,

时是高速信号,

或  时是高速信号,

时是高速信号,

或  时是高速信号,这些只是衡量标准的严格程度不同而已,关键在于系统可以容忍多大的反射噪声。

时是高速信号,这些只是衡量标准的严格程度不同而已,关键在于系统可以容忍多大的反射噪声。

因而,在PCB上两个器件布局位置固定的情况下,为了走线等长而延时相等,应优先缩短长走线信号的布线长度,而不是通过蛇形走线延长短走线信号的长度。

实际应用时,先连接最长走线,再将短走线通过蛇形延长,与长走线等长,以获取相等的信号延时和时序偏差最小化。

所以,若对基本原理不清楚,遇到时钟频率50MHz以上的电路,就蛇形走线满板飞,结果可能是得不偿失。

7. 基于传输有效长度的高速信号衡量标准

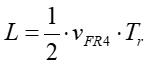

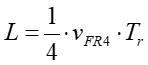

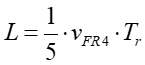

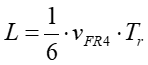

信号的上升时间(上升沿)Tr 对应的传输线长度,称为 传输有效长度 ,即

将(0.12)式代入(0.11)(  )式,有

)式,有

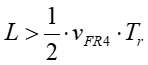

由此得到高速信号衡量标准的第二种表述是:认为当传输线长度大于传输有效长度的1/4(或1/5或1/6)时,

即  时是高速信号,

时是高速信号,

或  时是高速信号,

时是高速信号,

或  时是高速信号。

时是高速信号。

8. 基于信号有效波长的高速信号衡量标准

由信号的上升时间 Tr 获得的信号波长,称为 信号有效波长 ,即

注意:此处并非速度除以信号实际频率而得到的信号实际波长,而是由上升时间 Tr 得到的称为 “信号有效波长” 。

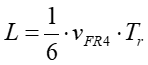

将(0.14)式代入(0.11)(  )式,有

)式,有

由此得到高速信号衡量标准的第三种表述是:认为当传输线长度大于信号有效波长的1/4(或1/5或1/6)时,

即  时是高速信号,

时是高速信号,

或  时是高速信号,

时是高速信号,

或  时是高速信号。

时是高速信号。

另外,比较(0.12)和(0.14)式知,传输有效长度和信号有效波长,在数值和量纲上是相同的,只是表述侧重点不同而已。

9. 总结

本文通过公式推导总结了常见的三种高速电路的衡量标准,即基于传输延时和上升时间的衡量标准、基于传输线长度和传输有效长度的衡量标准,以及基于传输线长度和信号有效波长的衡量标准。

通常意义上,“高速电路设计”的侧重点在于如何得到电源完整性PI(Power Integrity)和信号完整性SI(Signal Integrity),如何避免电磁干扰EMI(Electromagnetic Interference),使电路板获得较好的电磁兼容性EMC(Electromagnetic Compatibility);其根本思路或目的在于,用各种方法(如控制PCB加工工艺使其相对介电常数均匀,或使用阻抗匹配方法降低反射噪声)将系统反射噪声控制在可容忍范围内。

所以,于争博士在其信号完整性网上说“什么是高速信号?没有答案,我们也不需要答案。”

一方面,由于时钟频率越来越高,信号周期越来越小,可分配给信号的上升时间也越来越短(多数高速数字系统中,分配的上升时间约为时钟周期的1/10);另一方面,更低功耗的要求使得数字信号的摆幅也越来越小;所以,此二者导致信号的上升时间越来越短,对噪声更加敏感,系统越趋近于是高速电路。

一般情况下,当系统时钟大于50MHz时(当然还要依据系统对噪声的容忍程度),就要考虑进行PI / SI / EMC设计。当系统噪声无法容忍,需要进行PI / SI / EMC设计时,“高频信号”的概念基本等同于“高速信号”。

上述推导过程中用到的最基本物理量依然是速度、时间和距离,只是由于系统时钟越来越高,信号电平越来越低,系统噪声变得重要而无法忽视,电路设计的思维需从宏观过渡到微观,从集总参数电路过渡到分布参数电路(从电路器件尺寸和工作信号波长的角度分为集总参数电路和分布参数电路)。

-

哪位大神能给科普一下产品加密保护方面的知识?2016-12-08 0

-

VR一体机防艾科普教学(艾滋病认知科普)概述2018-10-15 0

-

VR防艾科普教学艾滋病认知科普概述2018-10-25 0

-

为什么说现在具备高速信号仿真知识非常重要?2019-11-22 0

-

小编科普D类音频功率放大器的热耗散知识2021-06-03 0

-

科普电涌的知识2021-09-14 0

-

科普知识:太阳能光伏知识2009-02-23 3980

-

科普:信号与频谱知识!2020-10-14 5310

-

10个和高速PCB设计相关的重要知识分享2020-10-23 2814

-

涡流的基本知识科普2022-05-19 6371

-

知识科普 | 沙子变“芯”计2022-11-10 338

-

电气基本知识科普2023-09-09 4923

-

pcb高速信号知识科普2023-09-15 844

-

科普|电源管理知识2023-10-17 361

全部0条评论

快来发表一下你的评论吧 !