海思Hi3566V100 SDIO硬件设计要点

描述

上一期我们介绍了 【Hi3566V100 I2C 硬件设计要点】,本期将继续给大家推出海思硬件设计系列:Hi3566V100 SDIO 硬件设计要点。

一、前言

Hi3566V100 是一颗面向车载行车记录仪、驾驶员状态监控等领域推出的高性能、低功耗的 Camera SoC。Hi3566V100 内核为 Cortex A7 MP2 @792MHz,支持双路 1080p@30fps H.265/H.264 编码。

二、Hi3566V100 SDIO 原理设计思路

Hi3566V100 有 2 个SDIO3.0 接口,其中 SDIO0 支持 SDIO3.0、SDXC 存储卡;

SDIO1 只支持对接 Wi-Fi,接口支持 1.8V 和 3.3V 电平;

SDIO0_CARD_DETECT 和 SDIO0_CARD_POWER_EN 只支持 3.3V 电平;

SDIO0 数据线电压域是 SDIO0_VOUT,自动识别 1.8V/3.3V,支持 1.8V/3.3V SD 卡。

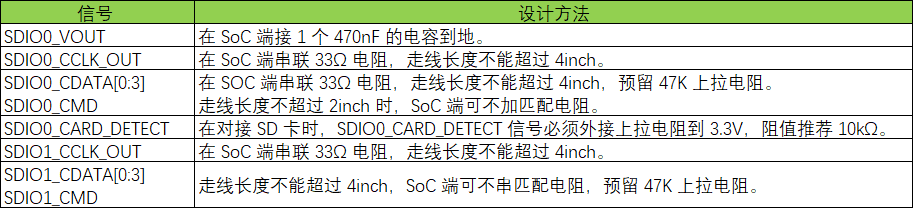

图 1 SDIO 信号设计要求

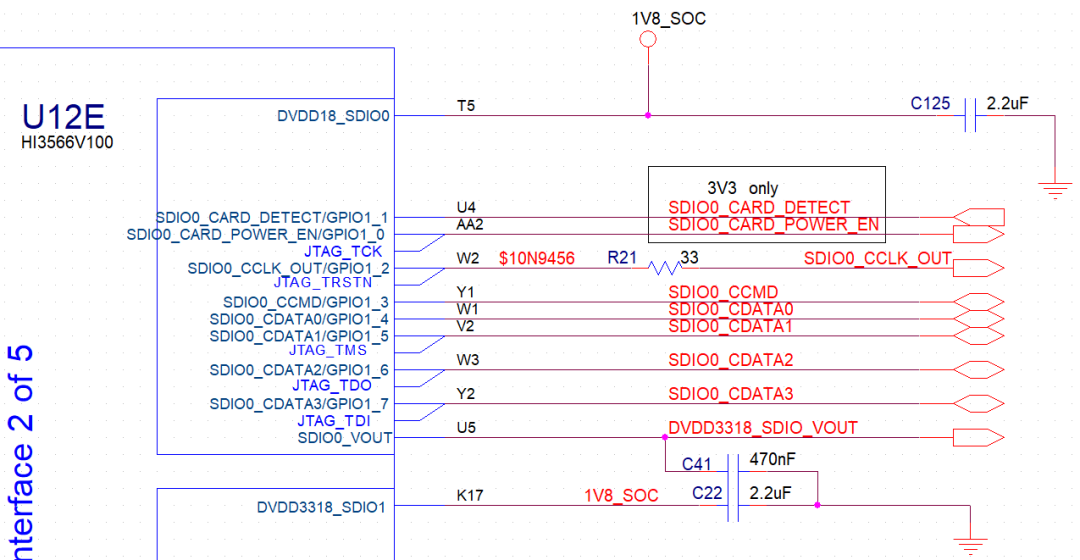

图 2 SDIO0 的 SoC 端原理图

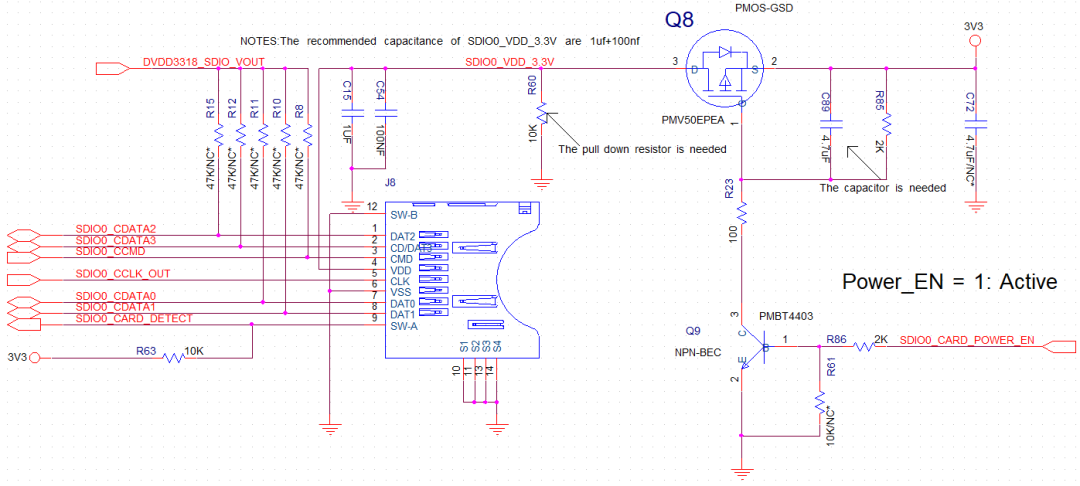

图 3 SDIO0 的 SD 卡端原理图

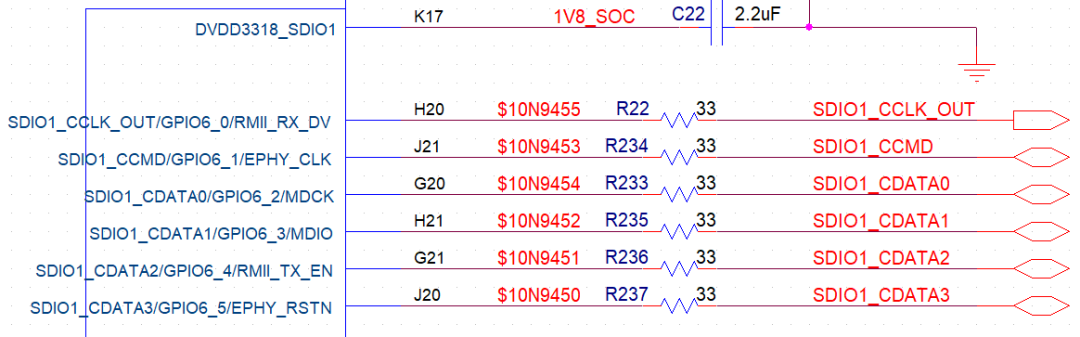

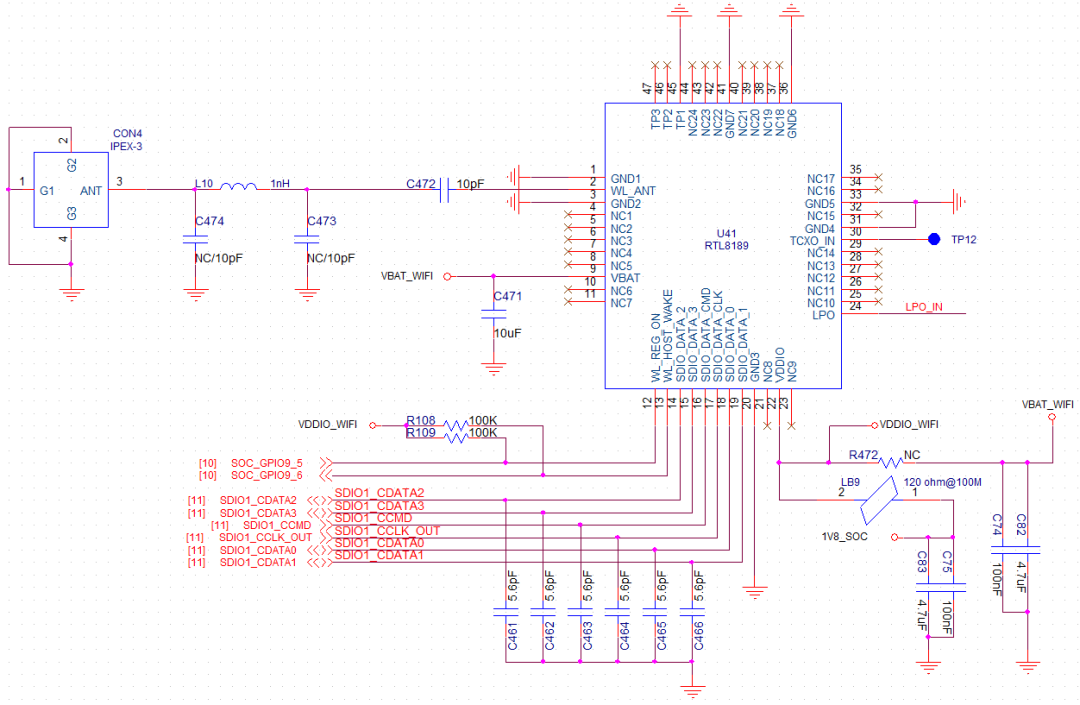

图 4 SDIO1 的 SoC 端原理图

图 5 SDIO1 的 Wi-Fi 端原理图

三、PCB 设计思路

- 相邻信号走线间距保证“3W”原则。

- SDIO0/1_CDATA[0:3]、SDIO0/1_CCMD 的线长以 SDIO0/1_CCLK_OUT 的线长为基准,偏差控制在 ±500mil。

- 如果 SDIO0 需要支持 SDXC 卡,那么 SDIO0 的数据信号必须以 GND 为参考平面,并保持信号参考平面完整。

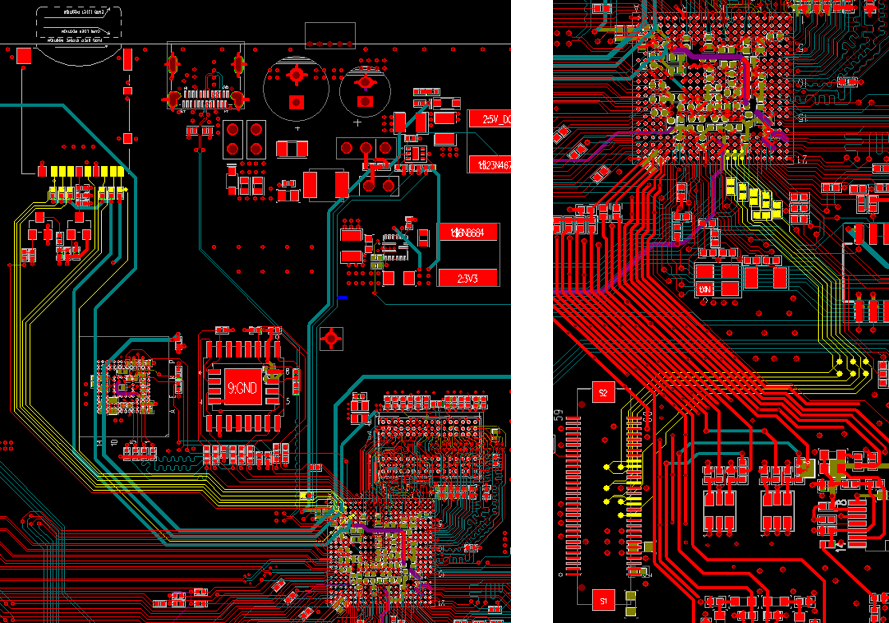

图 6 SDIO0 PCB 走线 图 7 SDIO1 PCB 走线

以上便是 Hi3566V100 SDIO 硬件设计要点的全部内容。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

海思系列 HI3521RFCV100 HI3521ARBCV100 HI3531RFCV102019-06-27 0

-

海思Hi3519V101,Hi3519AV100,Hi3519A图像 芯片 规格书2019-07-01 0

-

海思芯片Hi3556AV100,Hi3556A等各型号现货供应2019-07-03 0

-

海思Hi3531A,Hi3531D,Hi3531DV100,Hi3531AV100图像处理芯片现货供应2019-07-03 0

-

海思 索尼 镁光,OV,PIXELPLUS HI3519Av100 HI3516DV500 芯片规格现货2019-07-05 0

-

海思Hi3559V100,Hi3559V200,Hi3559A人脸识别 开发板 芯片2019-07-06 0

-

供应海思系列Hi3519V1002019-07-19 0

-

海思Hi3516DV300 Hi3516CRBCV100 Hi3531ARBCV100Hi3536DRBCV100 Camera芯片产品现货2019-08-03 0

-

海思系列芯片Hi3516D Hi3516DRBCV100等现货 Hi3516 Hi3516ERBCV100处理器2019-08-06 0

-

海思IC芯片 Hi3556AV100 Hi3556ARFCV100 Hi3519AV100 Hi3519ARFCV100 等各型号现货2019-08-27 0

-

海思HI3531ARBCV100芯片2019-10-13 0

-

海思Hi3559A Hi3519A Hi3519V101 Hi3519C系列芯片算力参数选型参考2020-09-01 0

-

海思方案Hi3861V100&&LV100硬件资料(10份)2021-05-09 0

-

海思Hi3861V100硬件资料2021-08-16 0

-

海思Hi3566V100 I2C硬件设计要点2023-12-04 767

全部0条评论

快来发表一下你的评论吧 !