全面解读电阻式内存的技术架构及其应用

存储技术

描述

全球存储器产业已进入一个必须寻求新兴替代技术的时代。在多样化的次世代存储器技术中,为何电阻式存储器,在类神经仿生运算的应用上值得期待?其更被业界认为是最有机会成为下一代通用存储器的选择,同时也是目前投入研发厂商最多之技术?本篇将带您一探究竟。

本文是闳康科技特别邀请在电阻式内存研究领域顶尖学者 王永和教授撰文介绍此新兴内存组件的发展概况与技术趋势,与读者分享此一重要科技领域的学术研究进展。

迈入寻求全新嵌入式非挥发性存储器技术的时代

全球内存产业已进入一个必须寻求新兴替代技术的时代了。近年来由于物联网、移动装置、高速计算机和智能汽车等产业的快速发展,大幅推升了人工智能 (AI) 及边缘计算 (Edge Computing) 等巨量运算架构的应用需求,也因此既有高容量存储组件例如 DRAM 及 NAND Flash,其在耗电量及数据访问速度上已无法跟上需求的脚步。并且,随着半导体工艺线宽缩微已超越 14nm、晶体管发展主流迁移到 FinFET 或 GAA 等先进结构,长期应用于 CMOS 芯片上存储的嵌入式 NOR Flash 碍于「闪存缩放限制 (Flash Memory Scaling Limit)」问题,也已无法跟上 SoC 芯片整合工艺的发展要求,必须要有全新的嵌入式非挥发性内存技术,才能搭配下一世代以先进工艺所制造的 ASIC 和 MCU。

电阻式存储器为何备受期待?

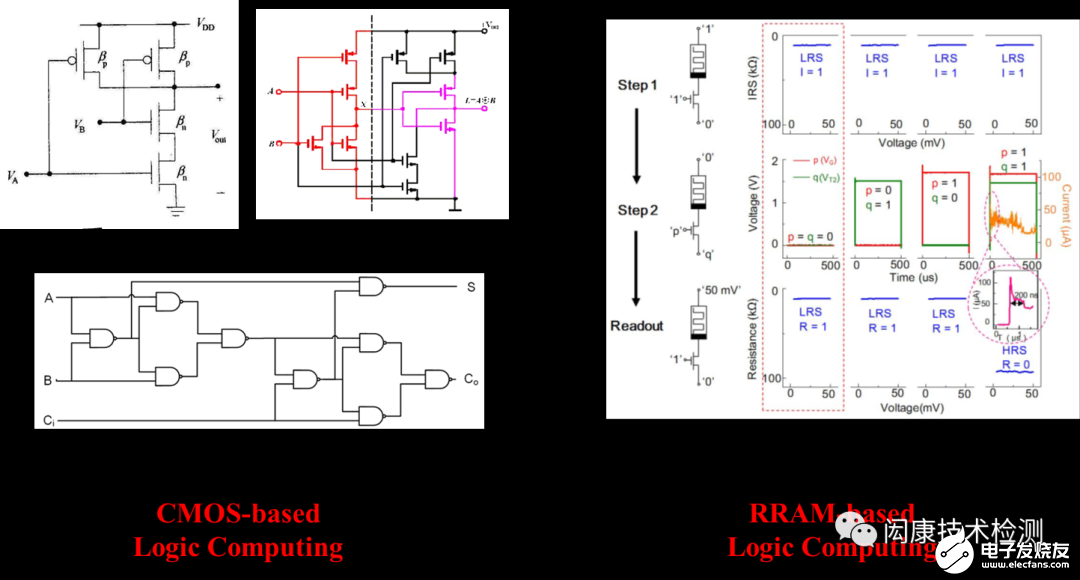

过去数十年来在世界各国合力开发下,已初略成形的次世代非挥发性内存技术包括铁电内存 (FRAM)、相变化内存 (PRAM)、磁阻式内存 (MRAM)、以及电阻式内存 (RRAM) 等。这些候选的新兴技术,不仅读写速度都比 NAND Flash 要快 1,000 倍以上,并且皆能够在纳安培 (nA) 的极低电流下操作。同时,也都具有潜力可突破 von Neumann 架构瓶颈,实现内存内运算 (In-memory Computing) 之能力。

在多样化的次世代内存技术中,电阻式内存由于相对具有读写快速、低耗能、结构简单、数据储存时间长、重复操作可靠度佳与成本便宜等产品优势,以及适合应用于类神经仿生运算的电导 (电阻) 渐变模拟特性,被业界认为是最有机会成为下世代通用内存的选择,同时也是目前投入研发厂商最多之技术,包含 Adesto (2020年已被Dialog并购)、Crossbar、Samsung、Panasonic、Micron、Hynix 及 Intel 等公司,都各别拥有不同的电阻式内存技术。尽管电阻式内存应用潜力巨大,但至今大多数仍然处于开发阶段,至目前为止有对外供货的公司仅 Crossbar、Panasonic 与 Adesto 三家而已。甚至该技术在其电阻变化的物理机制研究与最佳材料选定上,至今也仍未有定论。然而,业界普遍认为,随着人工智能应用的疾速发展、市场需求商机涌现,必然将带动电阻式内存在未来 3 至 4 年内迎来快速成长。产官学界都应及早进行策略布局、掌握此新兴内存的产业契机,创造下一个半导体奇迹。

电阻式内存由来

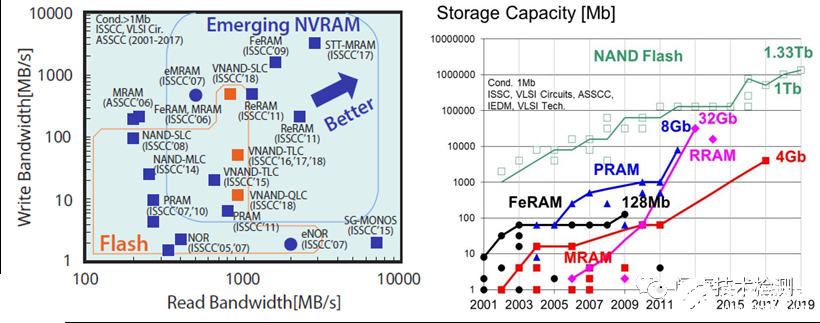

电阻式内存 (Resistive Random Access Memory, RRAM) 结构为简单的金属-绝缘层-金属 (Metal-Insulator-Metal, MIM),其原理为施予电压或电流操作,利用物质电阻改变组件的高低电阻状态,达成数字讯号储存效果。

电阻式内存最早起源自 1960 年代,研究学者 Hickmott 发现氧化铝 (AlOx) 材料经过电压或电流操作后,其电阻状态会因此改变[1];近年来,研究发现氧化镍 (NiO)[2-5]、氧化钛 (TiOx)[6-9]、氧化铪 (HfOx)[10-13]等绝缘体材料,亦可用于 RRAM 的中间绝缘层。RRAM 可利用特定的电压来读取不同状态的电阻值 (电流值),进而判读组件 ”1” 和 ”0” 的逻辑状态。此外,RRAM 具有良好的非挥发性记忆特性,其讯号储存状态可在不施加外在偏压的情况下,保存至下一次讯号的写入或抹除。

RRAM 物理机制与操作特性

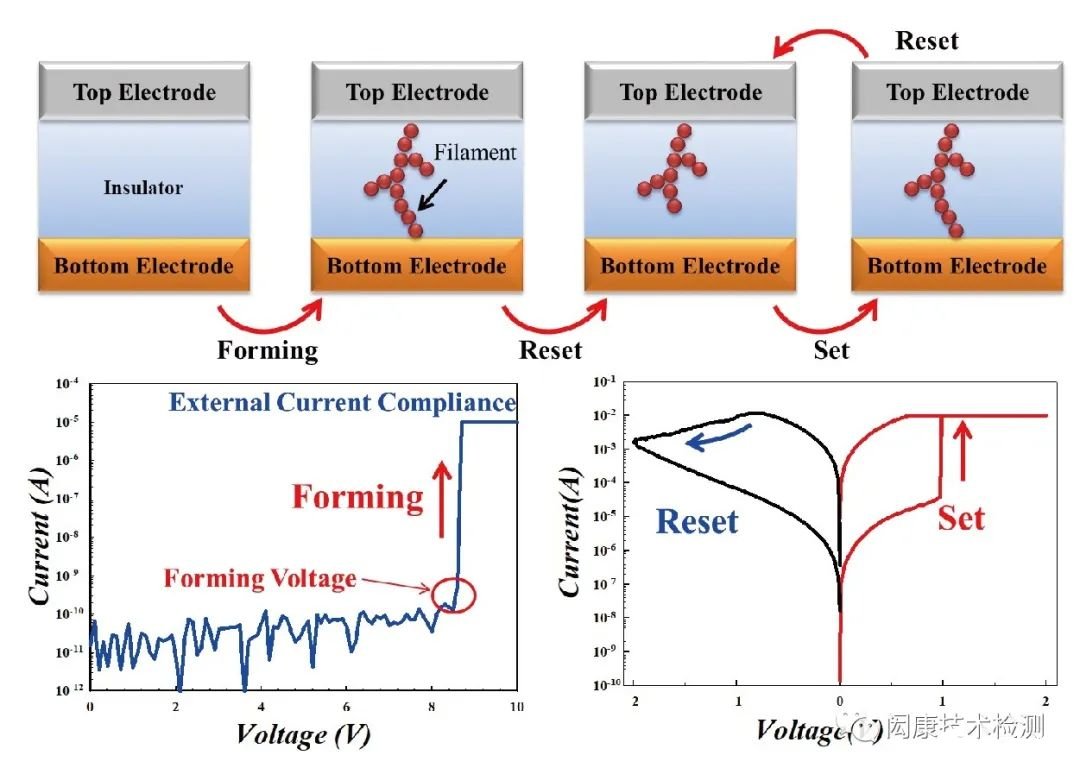

RRAM 的物理机制目前较受到注目的是灯丝理论 (Filament Theory)[14-16],普遍认为 RRAM 的操作方式是在一开始时给予组件一较大的外加偏压,使氧化物绝缘层内部形成导通路径,此时绝缘层会变为低阻态 (Low Resistance State, LRS),此过程通常需要限制电流 (Compliance Current),避免电流过大反应剧烈使组件永久崩溃,此步骤称之为 Forming。接着以组件偏压控制氧离子与氧空穴复合,使导通路径阻断,进而从低电阻态 (LRS) 回到高电阻态 (High Resistance State, HRS),此过程称为 Reset;而再次给予小于 Forming 所需的电压,即可将阻断的导通路径重新连接,从高阻态 (HRS) 再次回到低阻态 (LRS),此步骤称为 Set。

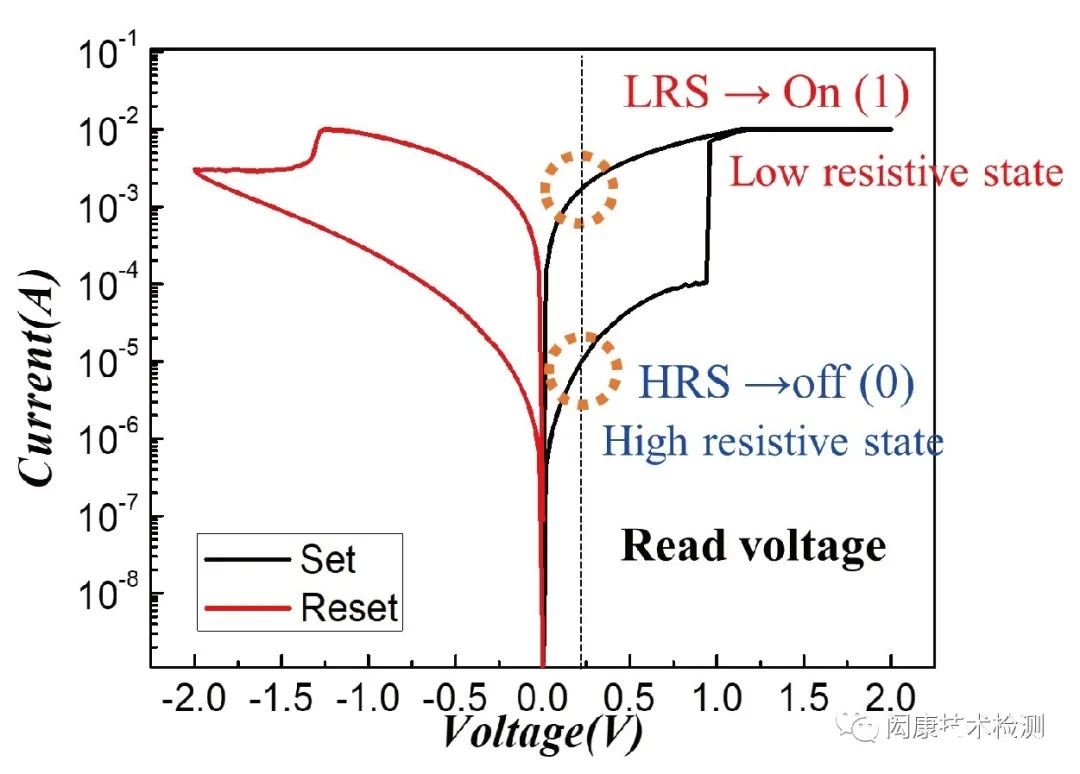

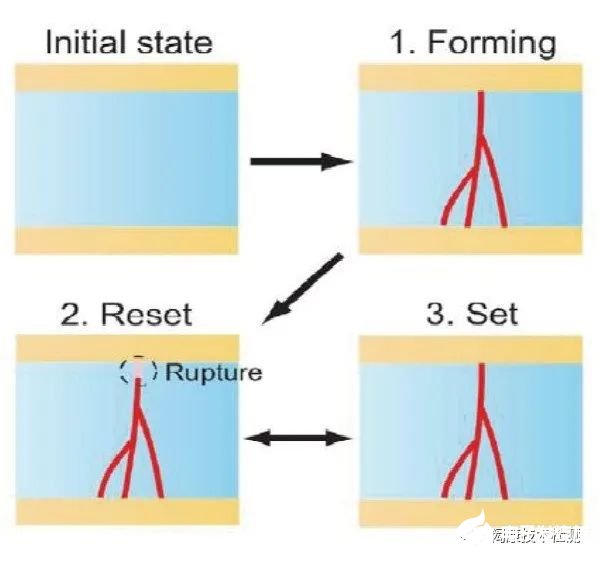

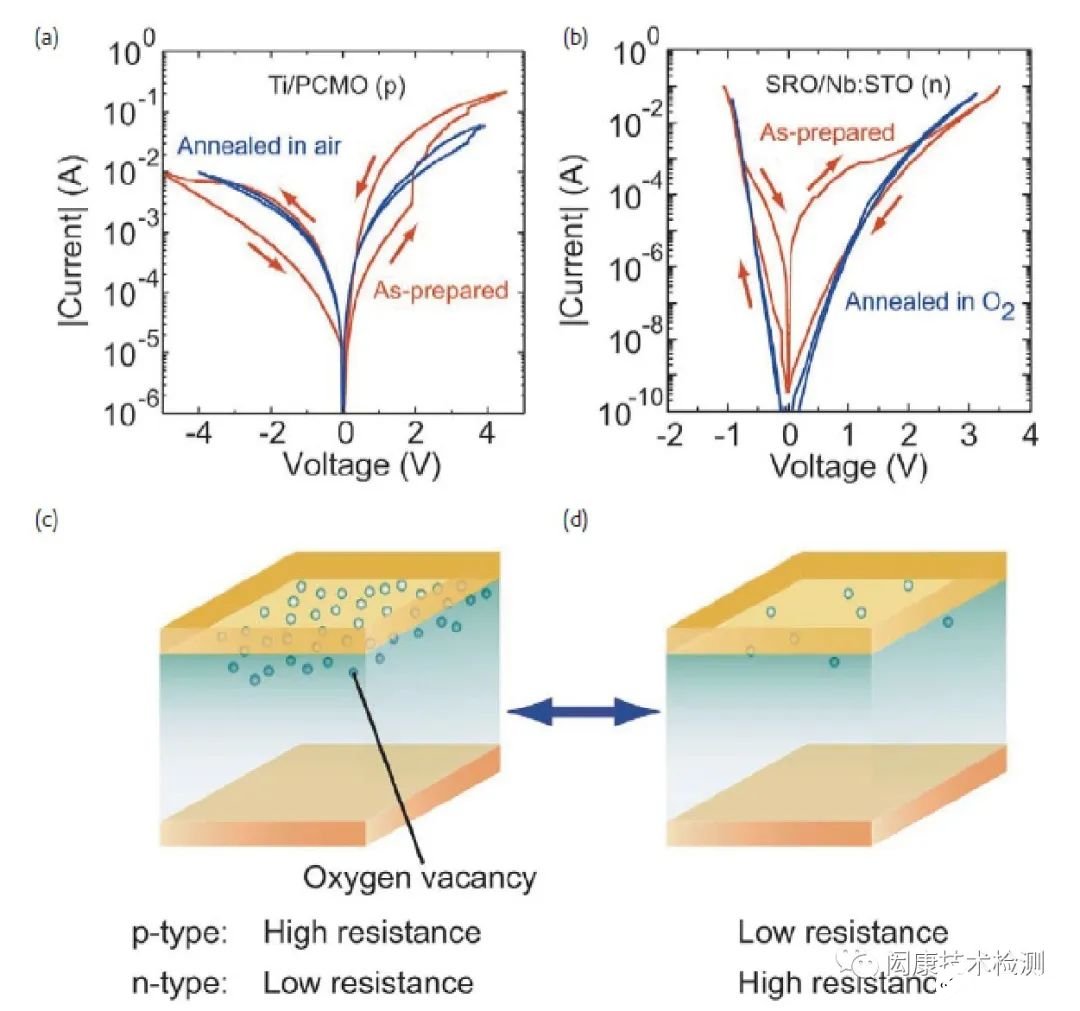

来回操作 Set 与 Reset process 就可以达成 RRAM 的写入与抹除,RRAM 的操作流程如图一所示,而在读取方面主要是藉由一微小的读取电压来判读不同的电阻值,以分辨数字讯号 0 和 1(图二)。RRAM 依阻值状态变化的不同可区分为阻丝型与界面型,阻丝型 RRAM 即于上下两电极间有一连续传导路径(图三),也是目前 RRAM 在传导机制中较受到广泛认同的类型;另一为界面型 RRAM (图四),透过施加外部电压,使绝缘体层中形成氧空穴或载流子电荷进行电子传递使其阻态改变,当氧空穴或载流子电荷变多,其电流增大,因此组件电极间的绝缘体层面积大小会影响阻态变化。

图一 RRAM 切换流程与电性输出图

图二 RRAM 用于数字内存判读方式

图三 灯丝型 RRAM 操作过程[14]

图四 界面型 RRAM 输出特性曲线与操作原理[14]

RRAM 操作方式分为两种特性:

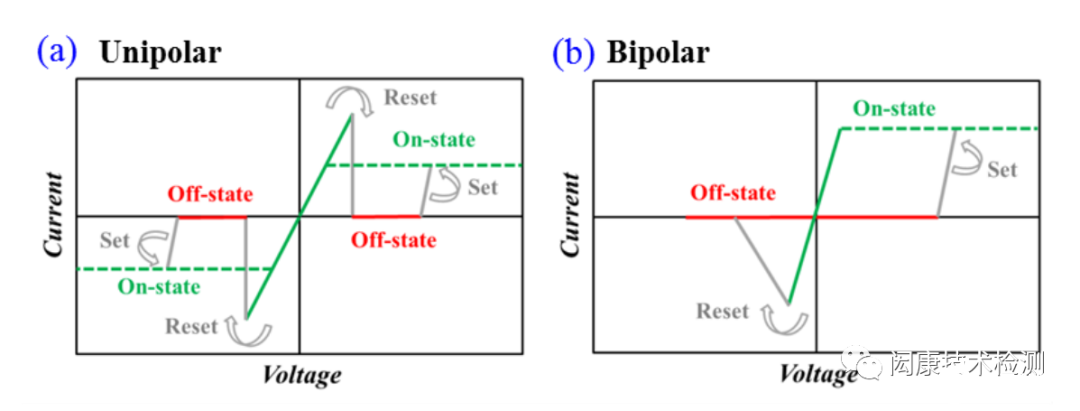

单极性 (Unipolar):如图五(a)所示,此种可藉由单一方向的电压即可作 Set 与 Reset 操作,Reset 过程以焦耳热 (Joule Heating) 造成电阻灯丝熔断使得阻态变化。

双极性 (Bipolar):指的操作电压需相反才能进行 Set 与 Reset,而阻态能切换的原因则主要认为来自于氧离子移动,对电阻灯丝进行氧化还原作用,使其有高低阻态变化,如图五(b)所示。

图五 RRAM 操作方式 (a)单极性操作 (Unipolar)、(b)双极性操作 (Bipolar)[17]

理想的金属 / 绝缘体 / 金属结构中,中间的绝缘层在施加偏压时并不会有电流通过,但实际上当组件受到过大电场或温度时,载流子能在绝缘层中移动传导,而有漏电流的产生,进而读出 HRS。其中电流的移动机制可利用电流-电压进行电流机制拟合 (Current-Fitting) 评估在绝缘层间电流主要透过何种机制进行移动,其传输机制主要可分为以下几种:

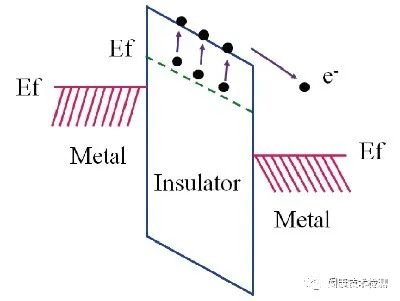

1.欧姆传导机制 (Ohmic Conduction):

主要以位于导带 (Conduction Band) 的自由电子 (Free Electron) 与价带 (Valence Band) 的空穴当作载流子传输的机制,在一小电压下电阻为常数,与电流呈线性关系。图六为 RRAM 结构的欧姆传导能带示意图,材料中的载流子受到外加电场的作用移动,进而产生电流[18]。

图六 欧姆传导之能带图

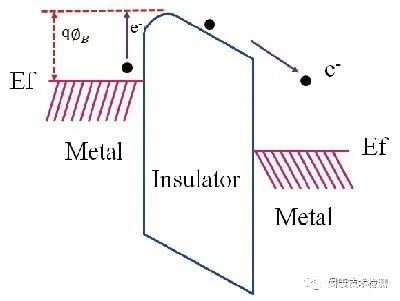

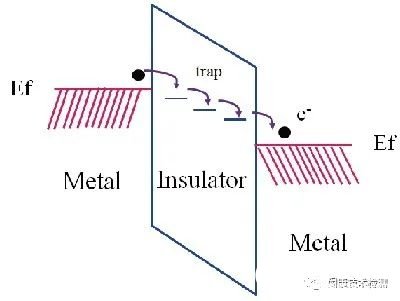

2.肖特基发射 (Schottky Emission):

一般金属与绝缘体的结面会存在着势垒高度 (Barrier Height),此势垒高度指的是绝缘体电子亲和力与金属功函数之间差值。图七所示为一 RRAM 之能带图,施加外加电场情形下与电子通过金属表面时产生的镜像电荷,使势垒高度下降,电子透过热激发影响越过势垒高度,电子能在绝缘体的传导带上传递,而产生电流称为肖特基发射 (Schottky Emission)[19]。

图七 肖特基发射之能带图

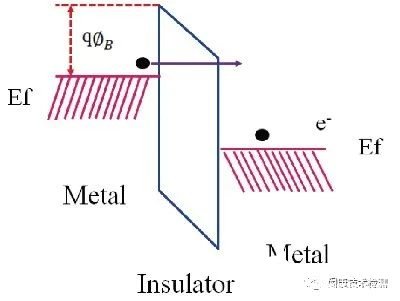

3.法兰克-普尔发射 (Frenkel- Poole Emission):

此传导机制与肖特基发射类似,同样受到外加电场影响,电子因热激发获得能量,且载流子跳至价带或导带的势垒高度降低,使载子能越过能障高度跳至价电带或导电带,进而由导带传递产生电流。

此时的势垒高度指的是在沉积绝缘体或半导体薄膜时,薄膜所产生的悬浮键或是缺陷,这些缺陷会在靠近价电带或导电带的边缘形成缺陷能级,而缺陷能级到价带或导带之间的差值,即为法兰克-普尔发射 (Frenkel-Poole Emission) 所需越过之势垒高度[20],如图八所示其能带图。

图八 法兰克-普尔发射之能带图

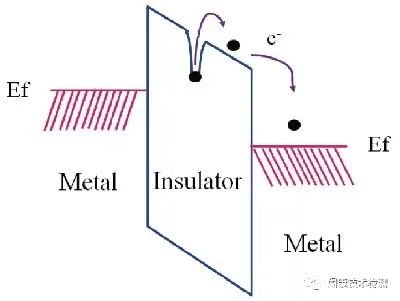

4.跳跃传导 (Hopping Conduction):

若薄膜之中含有许多连续缺陷存在时,这些连续缺陷会在绝缘体中产生连续缺陷能级,此时不需将电子激发至导电带,而是藉由彼此相近的缺陷能阶进行跳跃传递,进而产生电流。当缺陷彼此间距离越小时,其电子跳越能阶所需之活化能越小,称为跳跃传导 (Hopping Conduction),其能带图如图九所示[21]。

图九 跳跃传导之能带图

5.穿隧传导 (Tunneling):

主要是当外加电场过大时,能带图 Ec、Ev 更倾斜 (两侧电压差更大),使得绝缘体能带变薄,电子可直接穿隧过绝缘层至另一侧产生电流,其能带图如图十所示[22]。

图十 穿隧传导之能带图

6.空间限制电流传导 (Space Charge Limited Current):

当绝缘体单边或双边形成欧姆接触时,电极能不间断地提供载流子,当接触电极将电子注入至绝缘体或半导体的传导带时,由于载流子注入速率大于复合速率,电荷会在绝缘体内慢慢累积,进而影响电流流动,此为空间限制电流传导 (Space Charge Limited Current),能带图如图十一所示[23]。

图十一 空间限制电流之能带图

交叉数组架构的内存虽拥有较高的组成密度,却会产生使组件读取误判的潜行电流,由 RRAM 与晶体管组成的 1T1R 架构虽具备解决此问题的能力,且已被广泛应用,为何却仍不是最终答案?

提高密度的交叉阵列结构,以及解决潜行电流的1T1R 架构

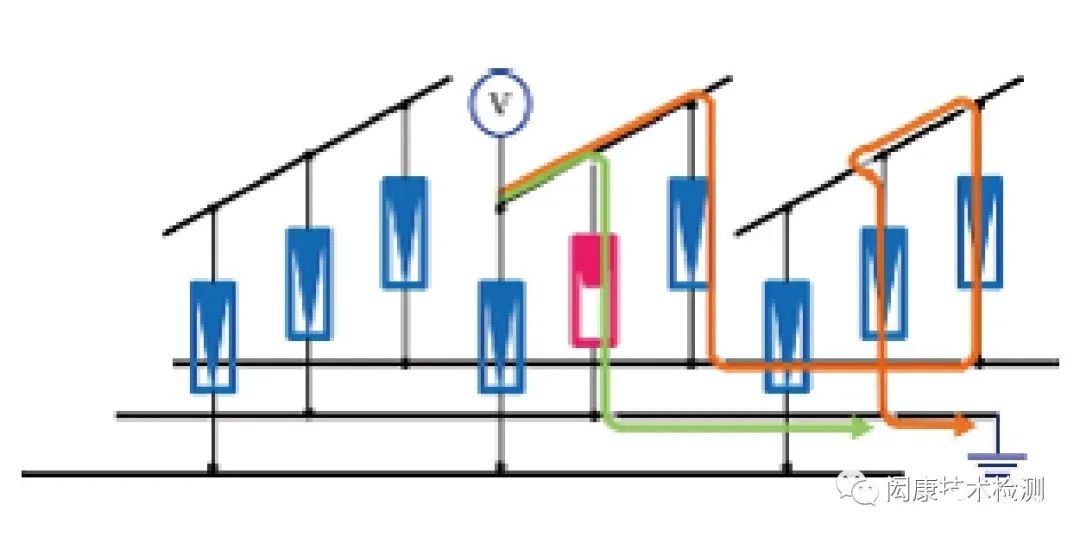

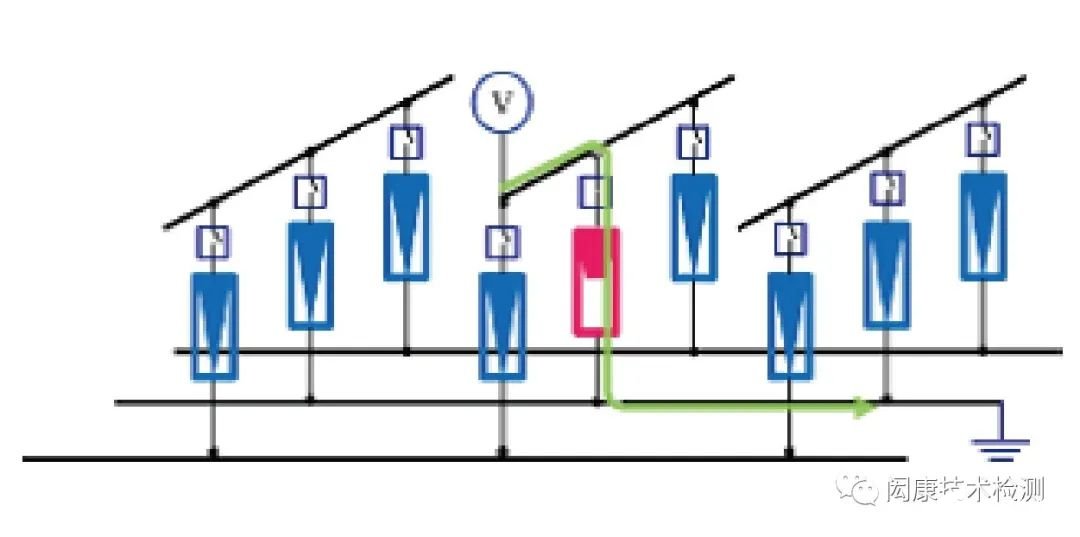

内存为提高集成电路上的密度,发展出一种排列结构方式,称为交叉数组 (Crossbar Array) [24-26],这种方式虽拥有较高的组成密度,但采用交叉数组结构会产生一个很大的问题,即潜行电流 (Sneak Path Current) 的产生 (如图十二所示),造成在读取特定组件状态时,受邻近组件影响导致状态误判。

为了解决潜行电流的问题,现今 RRAM 组件已发展出多种架构以解决潜行电流的问题 (图十三),包括将 RRAM 与晶体管 (Transistor) 组成的 1T1R 架构[26-27],或是 RRAM 与选择器 (Selector) 组成的 1S1R[28-29] 架构等方式。其中 1T1R 架构因结构简单且兼容于现今 CMOS 工艺受到广泛重视,目前多用于强调操作速度与低成本的嵌入式内存 (Embedded Memory) 上,并与微控制器 (Microcontroller Unit) 相互结合,进一步提升其效能。

图十二 RRAM 形成数组因潜行电流造成组件读取误判

图十三 RRAM 搭配一开关可解决潜行电流问题

然而在晶体管尺寸持续微缩的状况下,其能承受的电压将越来越小,这将使 RRAM 可能面临到操作电压不足的问题,为解决此问题势必需从结构与材料着手,因此近年来在 1T1R 架构组件的发展上,更衍生出相关仿生与逻辑运算等重要的新颖应用[30-32]。

生物世界历经数十亿年不断演化,为了适应多变生态系环境,生物往往发展出十分精致且节能的功能,电子组件利用仿效大脑神经的仿生技术,将为未来电子科技带来突破性发展。

RRAM 元件近年衍生的新颖应用

由于人工智能 (Artificial Intelligence, AI) 的快速发展,其相关应用包括影像辨识、语音识别、智能监控、智慧驾驶等均受到广泛瞩目,而深度学习等技术亦具备庞大发展潜能。在 AI 相关技术中,最被广为应用的即是机器学习,机器学习乃是利用多层次人工神经网络 (Artificial Neural Networks, ANN) 进行数据学习,RRAM 组件因具备非挥发性 (Non-Volatility) 与多位存储 (Multi-Bit Storage) 之特性,加上低耗能、高操作速度等优点,近年来产生许多新颖应用,包括类神经型态 (Neuromorphic) 与非范纽曼 (Non-Von-Neumann) 架构的智能运算。

因此基于先前研究成果,在薄膜晶体管结合 RRAM 组件所成为的 1T1R 架构下,透过组件数组运用于智能运算的主要架构,其中欲探讨并解决的问题有三项:

1. 结合组件特性与工艺,实现仿生 RRAM 数组结构。

2. 利用 RRAM 组件数组结构进一步实现逻辑运算。

3. 最终于 RRAM 组件数组实现人工神经网络的智能运算。

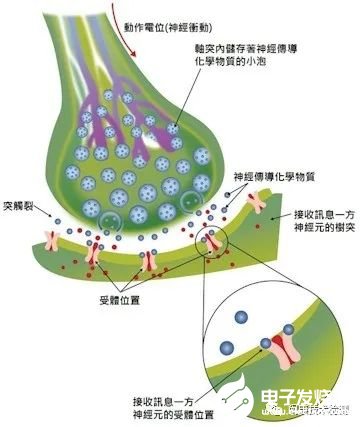

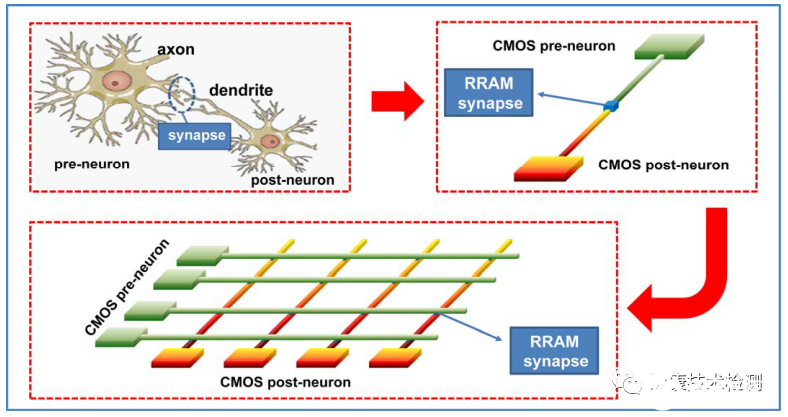

何谓仿生技术?

仿效生物能力以提升科学技术称之为仿生 (Bionic),人类的大脑即是相当好的例子。大脑是一个高效率且低功耗的系统,不只能够传递讯息,且具有学习与记忆的能力。人脑神经元间的连结称为突触 (Synapse) (图十四),突触间的传导行为在讯息传递的过程中扮演相当重要的角色。突触间的连接强度具有可调性,称为脉冲时序依赖可塑性 (Spike-timing-dependent plasticity, STDP),藉由调节进行增益 (Potentiation) 或抑制 (Depression)[33],进行整合后再依体内电位变化,决定是否藉由突触输出神经传导物质至下个神经元中,STDP 同时也是神经生物学中被认为是构成记忆和学习的重要基础。

图十四 人脑神经元及突触示意图

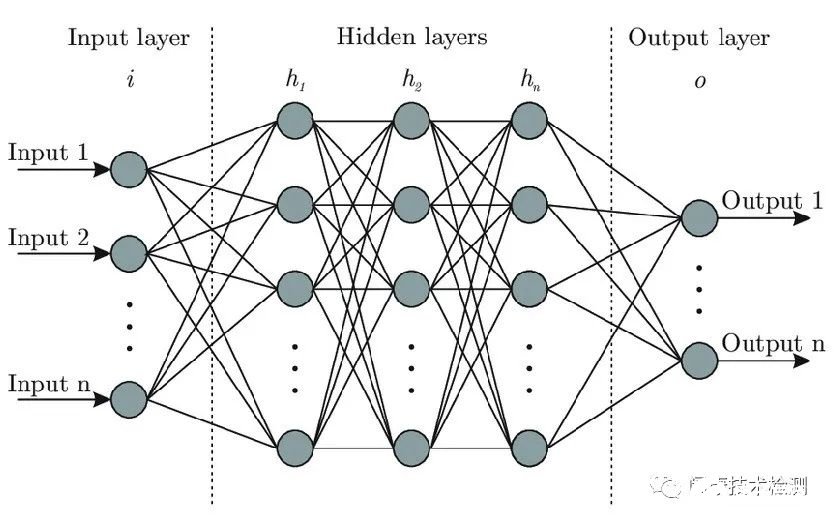

图十五 人工神经网络架构示意图[34]

未来利用电子组件仿效大脑神经讯息传递与学习记忆方式,将使电子科技与应用产生突破性发展。现代计算机储存记忆系以 0 和 1 的数字讯号来进行运算与记忆,而人脑不同于计算机是以模拟讯号来进行传递讯息与储存记忆,藉由对人类中枢神经系统的观察进而启发 ANN 概念。如同大脑中神经元 (Neurons) 构成人类的神经网络,ANN 是由许多节点运算单元 (Nodes) 互相链接 (图十五),通常可区分成三个部分,即输入层、隐藏层 (通常可为多层) 与输出层。每一层的所有节点皆与前、后层的节点连结[34],彼此连接形成类神经网络结构,藉数学计算模型对函式进行估算近似而得输出结果,使 ANN 在人脑所擅长如图像语音识别、分类、预测、记忆等领域具备高度发展潜力。

RRAM 元件于仿生技术的应用

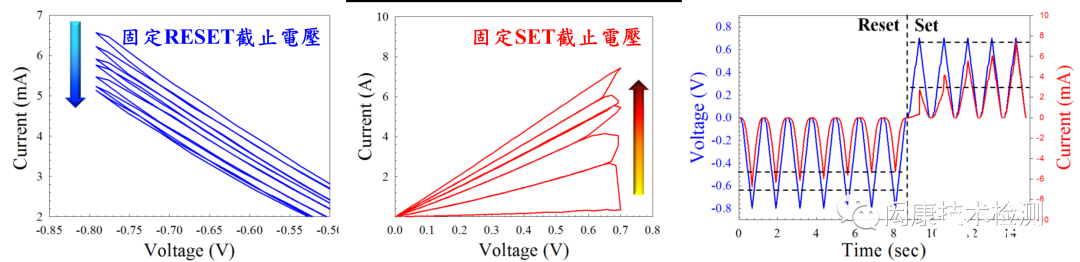

要了解RRAM 元件如何于此领域的应用,则需了解RRAM 元件的多重组态特性(Multi-level ResistanceCharacteristics),其相关研究与控制方法近年已受到广泛重视[35-37],对于单颗元件的多重阻态操作方式为:当元件在Set 过程时,设定不同的限制电流使元件LRS 阻值可分为多重阻态;而Reset 过程则利用不同截止电压范围,使得HRS 可得不同阶层变化的阻值,如此即可在单一存储器元件上拥有多位元存取的能力。

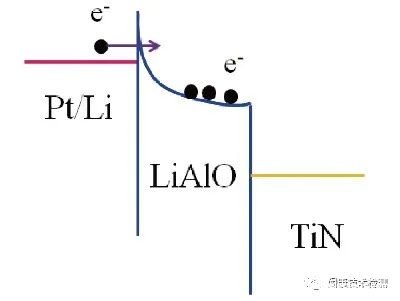

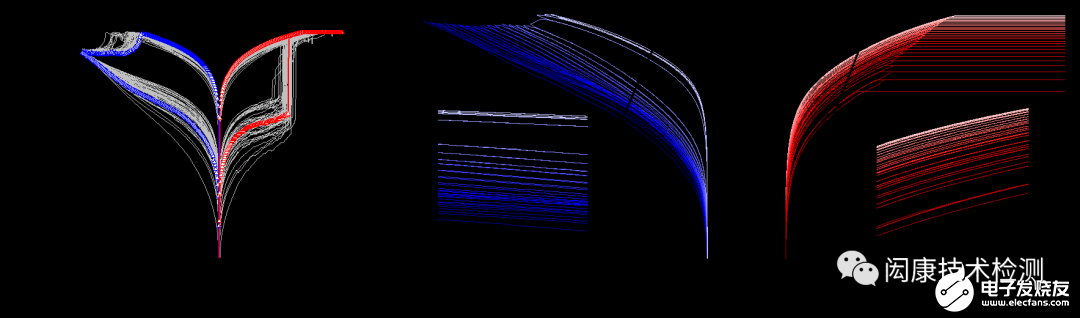

图16 为一Pt/LiSiO x/TiN 元件,具有良好多位元储存功能,我们操作在不同的Reset 截止电压与Set 限制电流条件下,可以使元件阻值变化状态成为连续态形式,此电阻变化形式又称为模拟式(Analog)电阻转换特性。

图十六 Pt/LiSiOx/TiN 组件直流特性、Reset 与 Set 过程之渐进变化情形

由于上述的操作方式在电路设计与运用上相当复杂,故将 RRAM 组件产生类式的连续态形式尚有另一种操作方法,即利用固定截止电压对组件进行连续扫描 (Consecutive Voltage Sweeping),藉由电压扫描方式渐进式地操作改变组件电阻状态。如图十七所示,当 Pt/LiSiOx/TiN 组件以 DC 操作时,若输入一个小于 Reset 电压并连续操作状态下,其电流会缓慢下降而阻态会渐渐上升;反之,若输入一个小于 Set 电压并连续操作,其电流会缓慢上升阻态会渐渐下降。若将操作电压与电流对时间轴作图,即可发现组件的阻值状态亦呈现渐进方式转换。上述除利用电阻值或电流参数呈现组件切换特性外,一般研究则多以电导 (Conductance) 变化呈现组件阻值变换特性。

图十七 Pt/LiSiOx/TiN 组件已连续定电压扫描下,阻值呈渐进方式变化

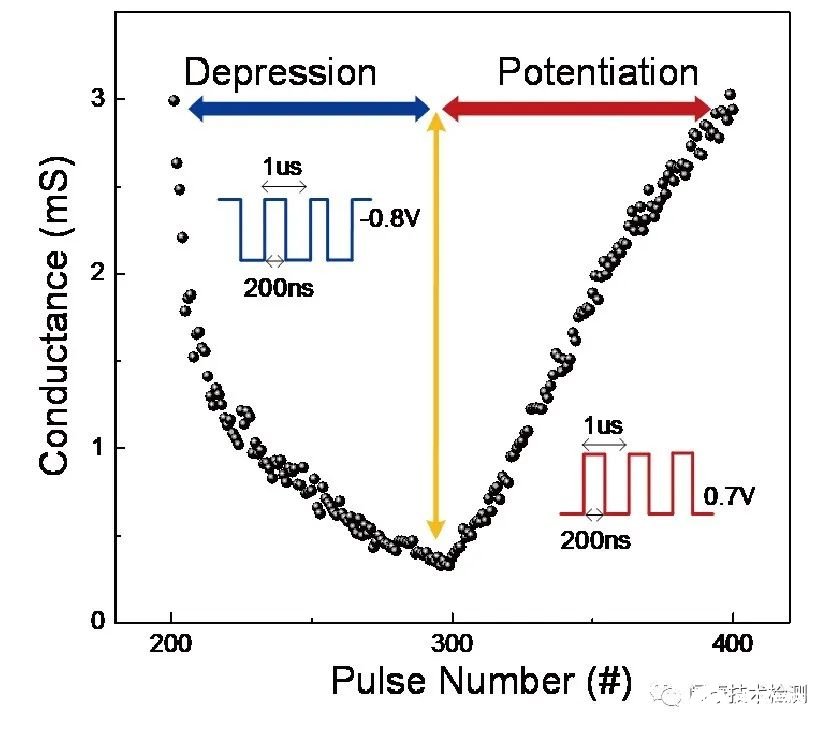

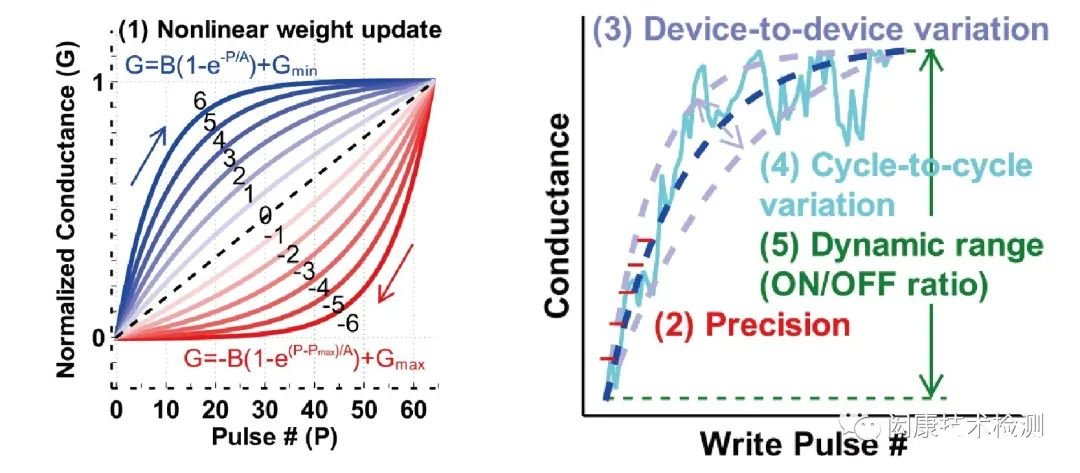

RRAM 组件如欲仿效突触的行为,则需利用组件电导 (电阻) 的渐变特性模拟突触权重的连续调节,进而模拟突触的可塑性,因此相关 RRAM 组件的突触特性关键参数相当重要,包括:

Linearity:电导调节线性度

Precision:权重 (电导值) 调节精度

ON/OFF Ratio:在脉冲操作下组件可调节的最大与最小电导值范围

Variation:组件的 Cycle-to-Cycle & Device-to-Device 变化度

Defective Rate:组件数组良率 (Yield) 与阻态保持 (Retention) 特性

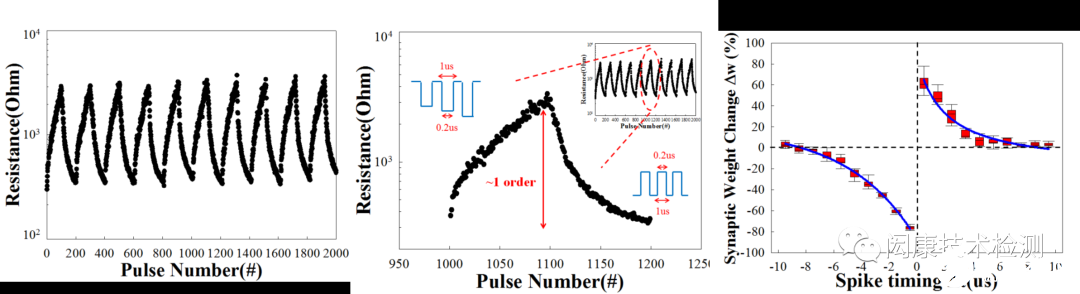

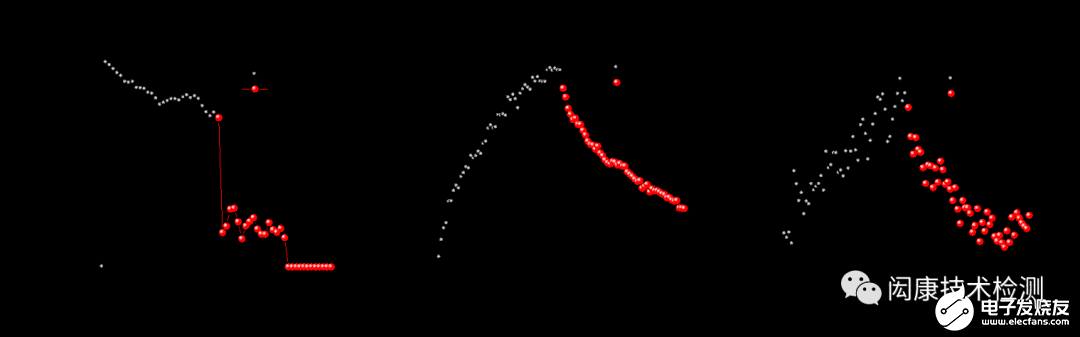

图十八系将 Pt/LiSiOx/TiN 组件利用连续脉波操作,以验证组件仿真神经元突触的仿生特性,藉由调整脉波电压大小、脉冲时间、脉波次数,即可改变组件阻态与导电性,使组件组态由 LRS 连续缓升至 HRS,再从 HRS 缓降至 LRS,以连续正负电压脉波操作仿真电阻增益 (Potentiation) 及抑制 (Depression) 行为。

图十八 Pt/LiSiOx/TiN 组件以连续脉波操作下阻值逐渐变化与 STDP 测试结果

由 STDP 实验结果显示,此组件仿效大脑突触行为将有助于类神经网络的发展。RRAM 欲作为仿生组件使用,则其阻值变化状态须具备连续态形式,藉以反复设定多种突触权重数值应用于类神经运算。理想的 RRAM 组件运用于突触操作的需求包括[38] (图十九、图二十):

稳定多阶的电导状态数

在脉冲操作下,拥有线性且对称的组件电导值变化

良好的组件均匀度,减小 Cycle-to-Cycle、Device-to-Device 的变化

足够的组件电导变化范围 (ON/OFF Ratio)

图十九 RRAM 组件有效电导状态

图二十 RRAM 组件的突触特性关键参数[38]

通常界面型 RRAM 组件的阻态变化虽较为线性,但是因其记忆窗口、持久性 (Retention) 与耐读写度 (Endurance) 的可靠度较差,实际运用上有相当难度,故寻求阻值变化具高度线性的 RRAM 组件对于仿生组件操作相当重要。先前研究结果显示,RRAM 组件中间绝缘层若含有高氧空穴密度,容易形成导电路径,其电阻转换多为突升或突降,意味着电阻切换行为如同数字讯号的 0 与 1,无法表现出模拟式的电阻渐变切换行为;而绝缘层中含氧空穴密度的 RRAM 组件,可能较有机会表现出模拟式电阻切换特性,同时能兼具较佳的可靠度[38-39]。除了 LiSiOx 材料外,先前实验结果亦发现基于 HfOx 材料结合不同电极或迭层组合,也可具备模拟式电阻转换特性 (图二十一)。

图二十一 HfOx 材料结合不同电极或迭层组合实现模拟式电阻切换特性

图二十二 模拟式 RRAM 组件由单一组件进而形成数组组件,对于仿生电子组件发展有相当重要性[35]

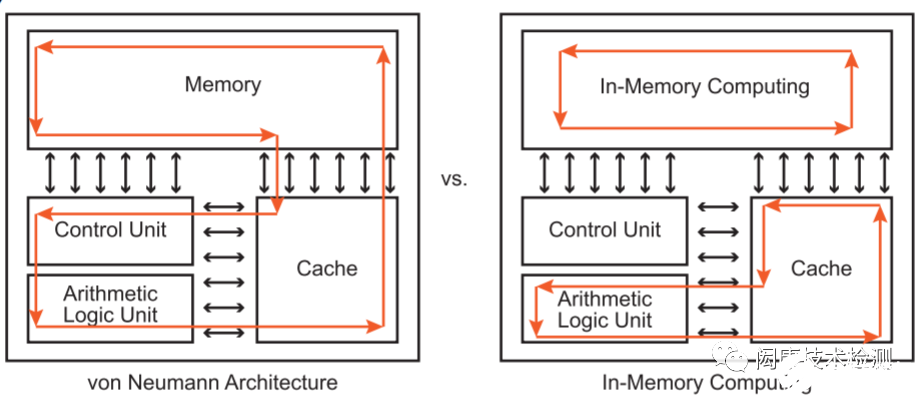

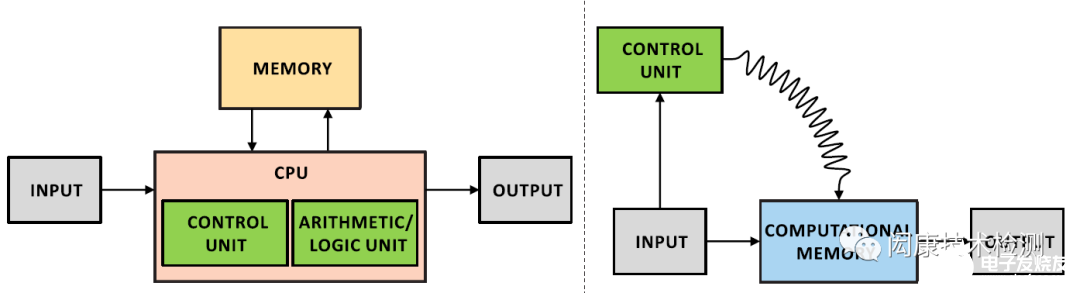

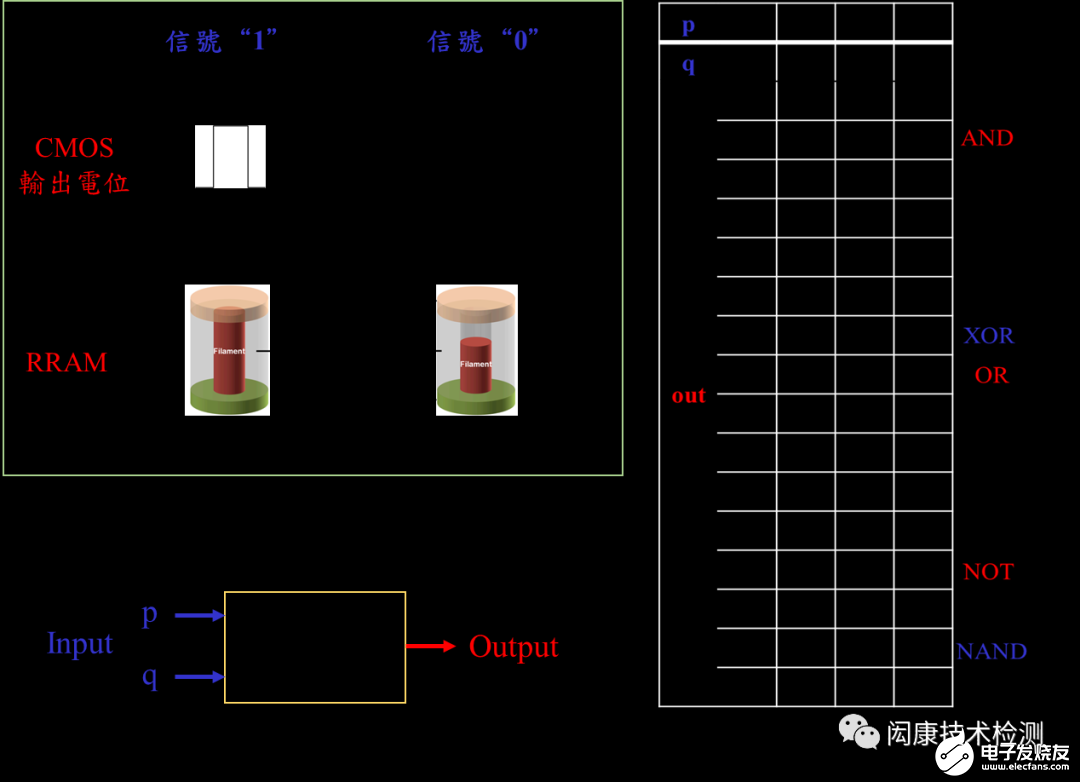

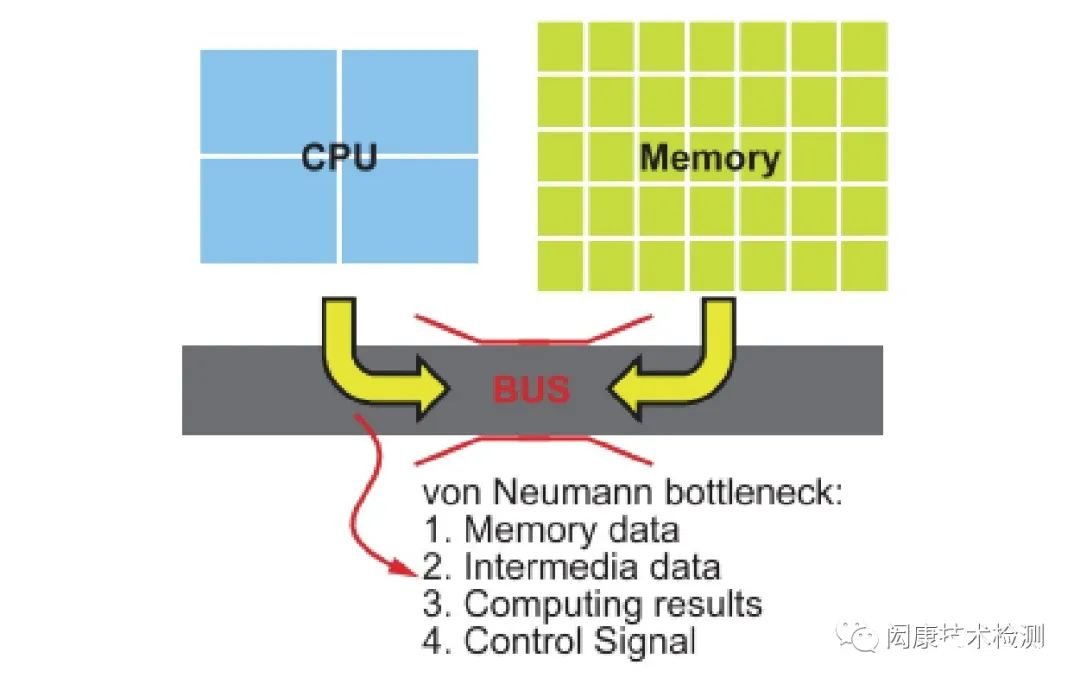

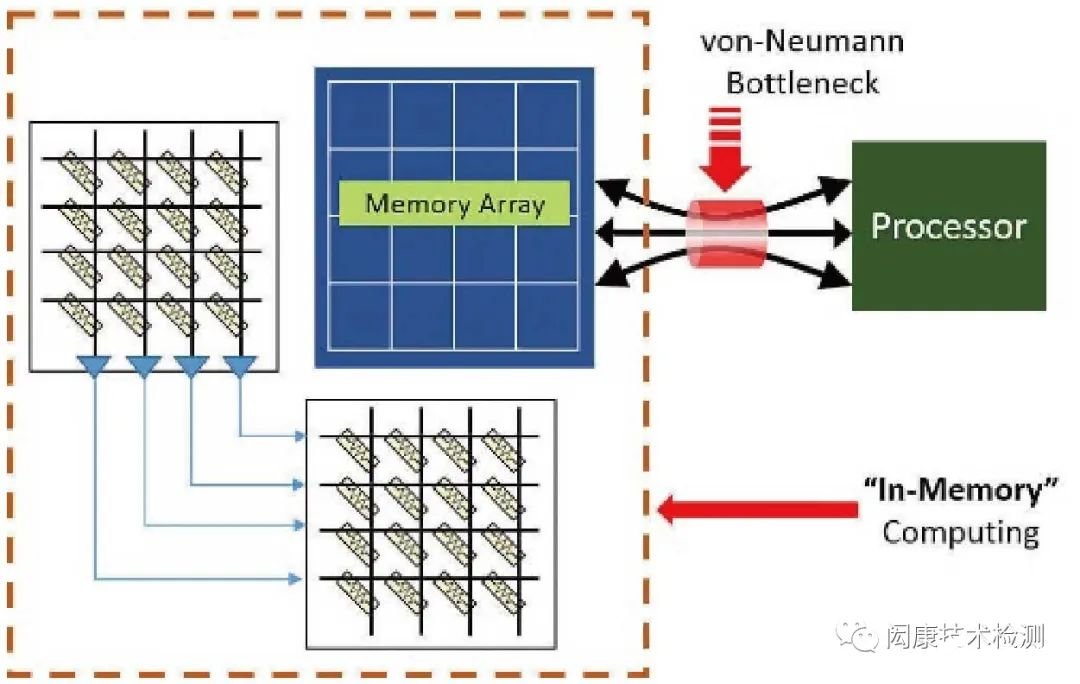

现今计算机均采用冯纽曼型架构 (Non-Von-Neumann),即信息处理和存储为分立架构 (图二十三),这样的方式使总线传输速度限制了数据的存储和指令周期。而计算机逻辑运算的实现系基于互补式金属氧化物半导体 (Complementary Metal-Oxide-Semiconductor, CMOS) 架构,逻辑电路的输入与输出系依赖电压的高或低电位来执行运作,但是逻辑运算结果通常需仰赖外加电路或装置才能进行储存。而利用冯纽曼 (Non-von-Neumann) 计算架构,可以实现内存内运算 (Computing in Memory),实际运算过程是经过内存的数据数据,直接在内存内先行运算,再将结果传送至处理器进行后续分析,能以低功耗、高效率的方式,提升计算机运作效能[40]。

图二十三 冯纽曼型架构与内存内运算之系统架构[38]

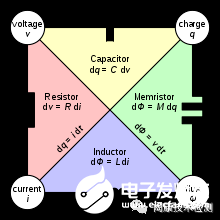

除了电阻、电感与电容组件外,RRAM 被视为是第四种基本被动组件 (图二十四)[41],RRAM 组件兼具非挥发特性与类神经运算的功能,使其可在单一组件上结合计算与储存之功能,实现内存内计算 (In-Memory Computing) 架构,因此非常有机会做为冯纽曼 (Non-von-Neumann) 计算架构之核心组件 (如图二十五)。

图二十四 RRAM 是第四种被动组件[41]

图二十五 冯纽曼计算架构可单一组件结合计算与储存功能

利用 RRAM 组件取代逻辑电路中的晶体管,可以有效节省组件面积。以 RRAM 做为逻辑组件运算时,分别以 HRS 与 LRS 代表数字讯号的 0 与 1,透过操作组件的 HRS 或 LRS 状态改变来实现逻辑运算。而在多 R 数组组件中,即可将组件阻值状态改变做为参数以实现逻辑运算(图二十六),并将结果直接储存在 RRAM 组件中,这种兼具数字讯号存储与逻辑计算的功能,省去了一般传统计算机架构之缓存器功能,可以有效降低数据传输的负荷,得以提高处理速度和效率,且具备低功耗的优点[42-43]。但是相较于传统 CMOS 电路,如何基于不同的 RRAM 组件结构,完整实现逻辑运算中的逻辑完整性 (Functional completeness)、计算复杂度 (Computation complexity) 以及逻辑的可重构性 (Reconfigurability),关系着 RRAM 组件是否能运用于冯纽曼计算架构,值得我们持续深入研究探讨其他可能的运用 (图二十七)。

图二十六 利用 RRAM 组件高低阻值状态做为输入端,可运用于布尔逻辑运算

图二十七 CMOS 电路基于晶体管架构实现逻辑运算,而 RRAM 组件可利用 1T1R 结构实现逻辑运算

展望

RRAM 可以藉由交叉数组的形态实现内存数组架构,以极低功耗实现内存内计算技术,在各种 AI 技术发展庞大的应用潜力,极有机会整合目前已面临发展瓶颈的各式内存组件,成为未来通用内存。

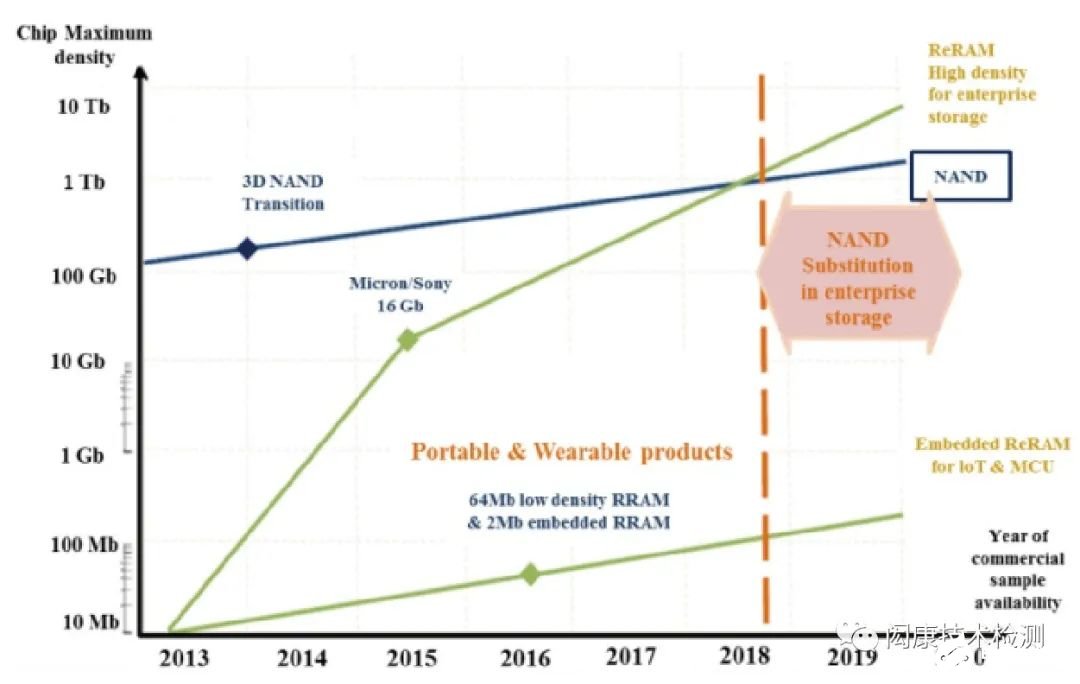

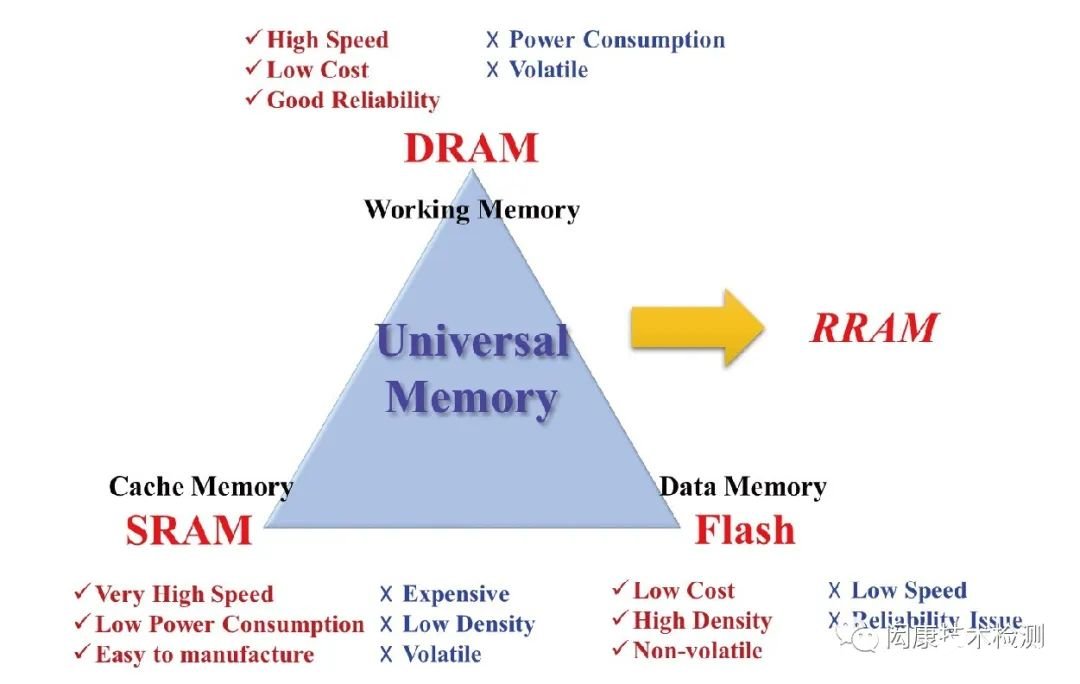

目前传统浮动栅极结构 (Floating-Gate Structure) 内存遭遇到微缩的困境,对此各方开始极力发展次世代内存,期能透过全新的储存方式或内存结构取代 Flash 内存。除了希望能提升组件操作的带宽及可靠度之外,同时也希望能透过简单的交点式结构 (Cross-point Structure) 达成高度组件微缩,增加内存储存容量 (如图二十八所示)。而 RRAM 组件拥有低操作电压、低功耗、操作速度较 NAND Flash 快 1000 倍以上的特性,还兼具低成本、非挥发性及高度可微缩性的优点[44],除可作为工作内存 (Working Memory) 外,还有制作高密度内存潜力。除了上述优点外,RRAM 的材料与工艺与目前 CMOS 后段工艺 (Back end of line, BEOL) 具有高度兼容性,所以 RRAM 相当具有实际产品化潜力与可行性 (图二十九)[45],极有机会整合目前已面临发展瓶颈的各式内存组件,成为通用内存 (Universal Memory)(图三十

。

图二十八 不同新兴内存的操作带宽以及内存的存储容量[44]

图二十九 RRAM 未来的发展趋势[45]

图三十 RRAM 有机会整合内存成为通用内存

近年利用 RRAM 组件结合人工智能运算的应用受到广泛瞩目,AI 即是基于 ANN 结构运用在图像识别、语音识别等场合,不同的神经网络 (如卷积神经网络 CNN、循环神经网络 RNN) 亦可用于人工智能核心,提供如智能监控、智能驾驶等相关应用。在大多数情况下,ANN 能在外界信息基础上改变内部结构,是一种具备学习 (Learning) 功能的自适应系统。

AI 的运作就是基于 ANN 架构模仿人类大脑神经进行学习动作,透过输入大量已知答案数据对计算机进行训练,若结果出现错误则调整突触间权重 (Weight),重复进行直到输出结果接近于正确答案,最终使计算机在接受输入讯息后,能够根据先前的学习经验做出判断结果。为了得到正确的输出结果,ANN 系统需进行大量反复矩阵乘法运算 (Iterative Matrix Multiplication Operation),故如何使计算机进行快速运算且得到正确结果,同时又能降低能量消耗,这对未来人工智能系统发展至关重要。

现代计算机架构主要采用范纽曼架构 (Von Neumann Architecture) 中央处理器负责运算,CPU 从储存数据的内存中取得数据进行运算,再将结果回传至内存储存。由于内存读写速度远较 CPU 运算来得慢,故于处理大量的数据运算时,不断地来回读取会大幅限制计算机的处理速度 (如图三十一所示)。近年来基于非挥发性内存的人工神经网络运算引起了许多关注,RRAM 可以藉由交叉数组 (Crossbar) 的形态实现内存数组架构,并以极低功耗进行运算,而数组结构更可用于向量与矩阵乘法运算,实现内存内计算 (In-memory Computing) 技术,在未来对于各种 AI 技术发展有很大的应用潜力[46] (图三十二)。

图三十一 冯纽曼计算架构之瓶颈[40]

图三十二 冯纽曼计算架构有机会突破计算与储存间的架构瓶颈[46]

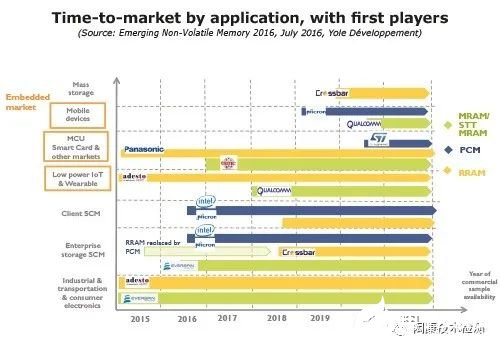

一个新兴内存技术的兴起,将带动全球的 IT 产业,影响的产业层面相当广 (图33),从产业链上游的 Microprocessor Unit、Fabless Companies 与Integrated Device Manufacturers (IDM) 公司,到中间的半导体制造产业 (Foundries),最后至应用端,而其中还包含了很多设备产业的参与。根据调查报告,未来几年是 RRAM 发展最关键的时期,各国际大厂与新兴公司都分别针对 MCU、Mass Data Storage 以及以内存为中心的全新运算架构等运用,制定出明确的 RRAM 开发 Roadmap (图三十四)。大数据结合 AI 科技的应用持续推动内存技术,需要更密切结合系统运算资源,无论是从性能或效率方面来看,当今多核心处理架构已无法满足未来实时运算需求。在这个关键时期,利用 1T1R 组件数组的仿生特性与逻辑运算,拓展组件在智能运算的发展与实际运用价值已显而易见 (图三十五)。

图三十三 新兴内存技术所影响的诸多产业链[45]

图三十四 相关半导体大厂对 RRAM 的开发 Roadmap[45]

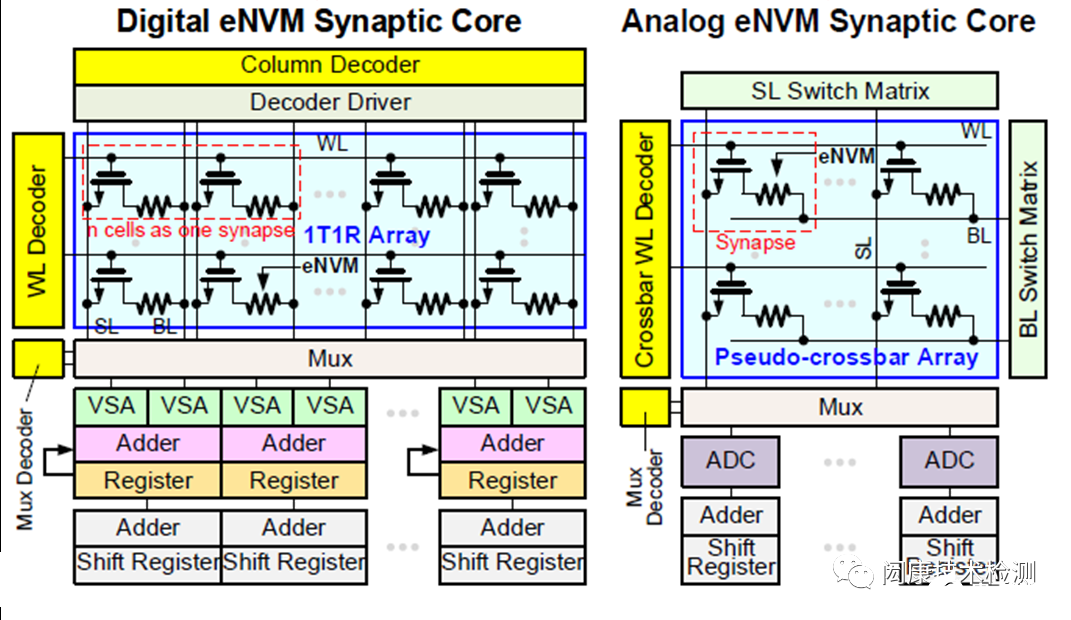

图三十五 基于 1T1R 组件数组架构基础上实现智能运算功能[38]

内存在整个半导体产业中占据极重要的地位,目前全球内存市场仍是以 DRAM 与 NAND Flash 为主流,其在内存应用领域的占比超过 90%。然而,近年来随着半导体产业持续朝更小的技术节点迈进,DRAM 与 NAND Flash 严重面临到尺寸微缩挑战,DRAM 目前已接近微缩极限、而 NAND Flash 则全力朝 3D 架构转型;除此之外,此两者在高速运算的进阶应用上也遭遇到阻碍。在人工智能、物联网、5G 强势崛起的数字时代下,数据处理需求量暴增,半导体业者皆加大对新兴内存技术的研发与投资力道,开始寻求成本更佳、速度更快、效能更好的储存解决方案。

目前已开发的次世代内存例如 FRAM、PRAM、MRAM、及 RRAM 等,无论是在尺寸缩微、操作能耗、读写速度、运作次数等方面,皆完胜现今稳固的 DRAM 及 NAND Flash 存储架构。与 DRAM 相比,其可以降低至少 20% 的功耗,并且由于它们都可以在不擦除资料的情况下直接覆盖旧数据,此可节省闪存 (Flash Memory) 所需的高擦除能耗、及因擦除数据导致的时间延迟,并减少或消除了其对电荷泵的需求。而所有新内存技术都能够对于储存地址的数据随机存取,也无须如目前内存的架构作法,采用个别保留两个数据副本在闪存及 DRAM 的动作来实现单次存取目的。上述这些功能特点,都将带来显著的功率节省以及性能提升效果。此外,新兴内存技术也具有实现芯片内嵌设计的潜力,可将逻辑 IC 与内存组件整合在同一颗芯片中。这样的设计不仅可以达成最佳的传输性能,同时也缩小了芯片体积。以单一芯片就能达成运算与储存的功能,这对于物联网或人工智能装置、经常需要大量数据运算与数据储存来说,非常具有吸引力。

然而,尽管有许多新兴的存储组件技术已经研发出来,但在这竞争激烈的规模产业中,只有极少数有机会成功。就目前次世代内存的发展现况来看,仍没有一种新型内存速度可以像 SRAM 及 DRAM 那样快。并且,在未来几年之内,也没有任何一款设计架构可以在成本上与 NAND Flash 竞争。在具有经济规模的供需基础下,NAND Flash 制造价格非常便宜,此将致使多数芯片供货商愿意接受闪存复杂的写入过程与高耗能代价来换取低成本优势,以满足消费者的期望。因此,如何在低成本前提下来实现小尺寸、高计算能力、以及超低功耗等目标,将是次世代内存在激烈的市场竞争中胜出之关键。

「电阻式内存」目前是取代现有内存应用技术最具吸引力的方案。相对于其它新兴存储技术而言,电阻式内存除了在功耗与速度方面有相当的优势之外,由于其结构特别简单,而电阻材料也可采用半导体工艺通用的二元金属氧化物例如二氧化钛、氧化铪、氧化镍等来制作,因此也能具有低成本的产品特点。根据市调机构 GII 预测,全球电阻式内存市场自 2018 至 2023 年期间成长率 CAGR 将高达 29.9%。就市场投入的情形来看,晶圆代工大厂台积电和三星的竞争,近年来由逻辑芯片快速扩及到内存市场,两家公司皆将电阻式内存列为重点技术开发目标。而半导体设备大厂美商应用材料公司 (Applied Materials Inc.) 也于 2019 年发布其 Endura Impulse PVD 平台,可精确沉积并控制电阻式内存中使用的多种材料。此外,2020 年初电阻式内存制造商 Crossbar 和其他几家公司也共同成立了一个名为 SCAiLE 的 AI 联盟,致力于提供高速且节能的 AI 平台。该联盟的主要工作是将电阻式内存、先进的计算器硬件、以及优化的神经网络算法作结合,用以提供低功耗的智慧运算解决方案。随着众多半导体厂及设备供货商相继投入推动,相信电阻式内存势必会快速崛起,成为次世代内存的市场主流技术。

本篇文章针对电阻式内存的技术架构及其应用提供了全面性介绍,同时也清楚阐述了该组件运作时电阻非线性变化的物理机制,可有效帮助读者快速地学习了解此最具市场潜力的前瞻技术。成大王永和教授的研究领域十分广泛,包括半导体组件及物理、微波集成电路、以及光电组件等,其团队发表的学术期刊及会议论文超过 400 篇、获证的相关专利超过 100 件。此外,王教授于 2007 年至 2020 年期间,曾先后担任中国台湾重要科研单位副院长及院长,对于建构台湾地区的研发平台、支持学术研究、推动前瞻科技、及培育科技人才等,也都有极大的贡献。

总结

内存在整个半导体产业中占据极重要的地位,目前全球内存市场仍是以 DRAM 与 NAND Flash 为主流,其在内存应用领域的占比超过 90%。然而,近年来随着半导体产业持续朝更小的技术节点迈进,DRAM 与 NAND Flash 严重面临到尺寸微缩挑战,DRAM 目前已接近微缩极限、而 NAND Flash 则全力朝 3D 架构转型;除此之外,此两者在高速运算的进阶应用上也遭遇到阻碍。在人工智能、物联网、5G 强势崛起的数字时代下,数据处理需求量暴增,半导体业者皆加大对新兴内存技术的研发与投资力道,开始寻求成本更佳、速度更快、效能更好的储存解决方案。

目前已开发的次世代内存例如 FRAM、PRAM、MRAM、及 RRAM 等,无论是在尺寸缩微、操作能耗、读写速度、运作次数等方面,皆完胜现今稳固的 DRAM 及 NAND Flash 存储架构。与 DRAM 相比,其可以降低至少 20% 的功耗,并且由于它们都可以在不擦除资料的情况下直接覆盖旧数据,此可节省闪存 (Flash Memory) 所需的高擦除能耗、及因擦除数据导致的时间延迟,并减少或消除了其对电荷泵的需求。而所有新内存技术都能够对于储存地址的数据随机存取,也无须如目前内存的架构作法,采用个别保留两个数据副本在闪存及 DRAM 的动作来实现单次存取目的。上述这些功能特点,都将带来显著的功率节省以及性能提升效果。此外,新兴内存技术也具有实现芯片内嵌设计的潜力,可将逻辑 IC 与内存组件整合在同一颗芯片中。这样的设计不仅可以达成最佳的传输性能,同时也缩小了芯片体积。以单一芯片就能达成运算与储存的功能,这对于物联网或人工智能装置、经常需要大量数据运算与数据储存来说,非常具有吸引力。

然而,尽管有许多新兴的存储组件技术已经研发出来,但在这竞争激烈的规模产业中,只有极少数有机会成功。就目前次世代内存的发展现况来看,仍没有一种新型内存速度可以像 SRAM 及 DRAM 那样快。并且,在未来几年之内,也没有任何一款设计架构可以在成本上与 NAND Flash 竞争。在具有经济规模的供需基础下,NAND Flash 制造价格非常便宜,此将致使多数芯片供货商愿意接受闪存复杂的写入过程与高耗能代价来换取低成本优势,以满足消费者的期望。因此,如何在低成本前提下来实现小尺寸、高计算能力、以及超低功耗等目标,将是次世代内存在激烈的市场竞争中胜出之关键。

「电阻式内存」目前是取代现有内存应用技术最具吸引力的方案。相对于其它新兴存储技术而言,电阻式内存除了在功耗与速度方面有相当的优势之外,由于其结构特别简单,而电阻材料也可采用半导体工艺通用的二元金属氧化物例如二氧化钛、氧化铪、氧化镍等来制作,因此也能具有低成本的产品特点。根据市调机构 GII 预测,全球电阻式内存市场自 2018 至 2023 年期间成长率 CAGR 将高达 29.9%。就市场投入的情形来看,晶圆代工大厂台积电和三星的竞争,近年来由逻辑芯片快速扩及到内存市场,两家公司皆将电阻式内存列为重点技术开发目标。而半导体设备大厂美商应用材料公司 (Applied Materials Inc.) 也于 2019 年发布其 Endura Impulse PVD 平台,可精确沉积并控制电阻式内存中使用的多种材料。此外,2020 年初电阻式内存制造商 Crossbar 和其他几家公司也共同成立了一个名为 SCAiLE 的 AI 联盟,致力于提供高速且节能的 AI 平台。该联盟的主要工作是将电阻式内存、先进的计算器硬件、以及优化的神经网络算法作结合,用以提供低功耗的智慧运算解决方案。随着众多半导体厂及设备供货商相继投入推动,相信电阻式内存势必会快速崛起,成为次世代内存的市场主流技术。

本篇文章针对电阻式内存的技术架构及其应用提供了全面性介绍,同时也清楚阐述了该组件运作时电阻非线性变化的物理机制,可有效帮助读者快速地学习了解此最具市场潜力的前瞻技术。成大王永和教授的研究领域十分广泛,包括半导体组件及物理、微波集成电路、以及光电组件等,其团队发表的学术期刊及会议论文超过 400 篇、获证的相关专利超过 100 件。此外,王教授于 2007 年至 2020 年期间,曾先后担任中国台湾重要科研单位副院长及院长,对于建构台湾地区的研发平台、支持学术研究、推动前瞻科技、及培育科技人才等,也都有极大的贡献。

审核编辑:黄飞

-

诚聘嵌入式软件架构师2017-03-01 0

-

全面解读触摸屏技术与触控设计技巧2018-11-13 0

-

嵌入式系统的软件架构设计!2020-08-10 0

-

【6.2】技术解读(框架、场景案例解读)2021-06-04 0

-

解读CPU的组成指令集架构2021-07-30 0

-

决定嵌入式系统软件架构的因素和架构的影响2021-11-08 0

-

【视频】UX设计第一期:HarmonyOS超级终端体验全解读(一)2021-12-01 0

-

如何使用嵌入式的内存分配管理技术2021-12-17 0

-

OpenHarmony技术日全面解读3.1 Release版本,系统基础能力再升级2022-04-27 0

-

了解电阻式触摸屏的原理及其应用2023-04-06 0

-

全面解读人脸识别技术发展史2018-07-16 8273

-

intel新CPU架构详细解读2018-12-25 13288

-

压敏电阻选型、参数解读及作用2021-06-25 1596

-

全面解读电子封装工艺技术2022-10-10 897

-

多维度全面解读集成电路相关技术2022-11-21 657

全部0条评论

快来发表一下你的评论吧 !