先进封装技术在三维闪存中的应用

描述

近年来,随着人工智能、物联网和 5G 等技术的蓬勃发展和应用,市场对数据处理以及存储的需求逐渐增大。根据 IDC 预测,全球数据圈每年被创建、采集或复制的数据量,由 2018 年的 32 ZB 到 2025年将增至 175 ZB。半导体存储具有存取速度快、功耗低、体积小、可靠性高等优势,广泛应用在电子设备中,并且正逐步取代机械硬盘成为主流存储器。其中闪存不同于 DRAM,因其具有断电数据不丢失的优点,多用于“数据仓库”来使用。其技术的发展也是朝着不断增大单位面积存储容量的方向发展,由二维到三维,再到不断地增加堆栈层数,当前业界已经推出 200 层以上堆栈的产品,未来还会向 1000 层发展。

闪存因其采用电荷隧穿的方式实现存储功能,相比 DRAM 的电容方式,存储速度上大打折扣,封装方式上也以传统的封装形式为主,目前市面上采用先进封装工艺来实现其存储功能的产品非常少。随着数据时代的发展,各领域 AI 应用对数据传输及处理的多样性需求逐步增多,同时伴随摩尔定律的放缓和各类先进封装技术的涌现,持续探索新的封装形式,将处理器、DRAM、闪存采用新的形式结合起来,提升总体运算能力,将会影响未来三维闪存封装发展方向。

三维闪存及当前主要封装形式简介

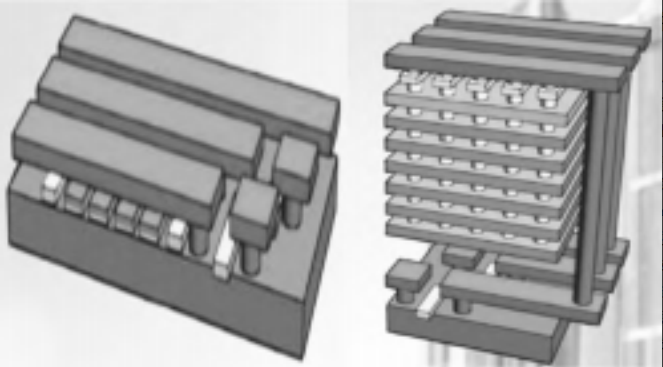

东芝公司于 1989 年开发了 NAND Flash 的结构,主要目的是降低每比特的成本,获得高性能,并且可以通过接口轻松升级。最初 2D 结构的存储单元仅仅是布置在平面中,因此想要提高单位存储密度,唯一方法就是微缩晶体管,不断减小制程工艺的节点。但是对于 NAND Flash 器件,减小晶体管会带来电荷存储空间不足、电荷串扰等问题。在不增大芯片面积的情况下,为了提高存储密度,NAND Flash厂商纷纷推出 3D 堆叠技术,将存储单元沿垂直方向进行堆叠,从而提高单位面积的存储量,如下示意图 1所示。目前,NAND Fash 的主要代表公司有三星、铠侠、西数、海力士、美光,英特尔和国内的长江存储等。

2D 结构和 3D 结构的 NAND 示意图(图片来源于网络)

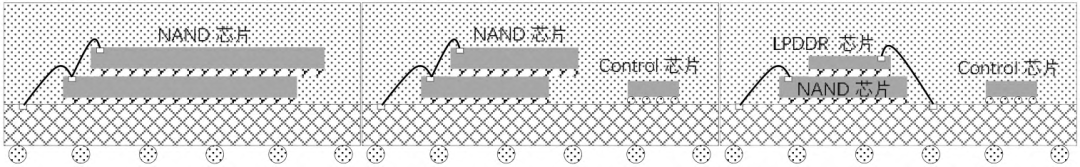

从封装角度来看,BGA 形式是实现大容量存储的主要方案,且主要有 3 种,即封装体内只含有NAND 芯片的 Raw NAND,增加控制芯片的 ManagedNAND (eMMC/UFS/NVMe),和增加主控芯片以及LPDDR 芯片的 eMCP,如图 2 所示。内部实现电连接主要采用 Wire Bonding 形式,对部分高端 ManagedNAND 产品中的控制芯片会采用 Flip Chip 形式(图示为 Flip Chip)。

由于 3D NAND 产品目前主要应用在存储卡、闪存盘和固态硬盘等,以 Wire Bonding 为主的传统封装方案可以满足对高密度数据存储的需求。未来,随着物联网(IoT)、人工智能、自动驾驶和其他数据密集型应用的不断发展,对数据的存储和读写速度的要求将变得更具挑战性,因此有必要思考更多封装形式及技术,来解决相应的需求。

先进封装技术及其在三维闪存中的可能应用

随着半导体行业进入后摩尔时代,在成本和性能要求的综合驱动下,涌现出各种先进封装形式,并已成为行业未来发展的趋势之一。当前主要的先进封装形式有 SiP (System in a Package) Fan in/out、2.5D/3D、Chiplet 等,相关的技术有凸块(Bumping)、RDL( Redistribution Layer),TSV(Through Silicon Via )等技术。此类封装技术的特点是:封装内部连接摆脱传统的焊线方式.基板被部分或全部取代使用凸块及直接键合等方式实现连接,从而在提高集成度、降低封装尺寸的同时,缩短电流传导路径、减少能耗、降低成本,满足性能需求。

Bumping & RDL

Bumping 和 RDL(Redistribution Layer)的工艺在流程上大体一致,都包含喷涂、曝光、显影、溅射、电镀和刻蚀等主要的工艺过程,Bumping 工艺最后流程需要经过回流焊形成凸块,实现与外界的电性能连接,而 RDL 的最外层线路也需要 Bumping 工艺实现内外的线路的导通。

RDL 也称重新布线层,由金属层和介质层组成,其工艺是在载体或者晶圆的表面沉积金属层和相应保护的介质层形成金属布线,对 IO 的端口进行重新布局,可以根据产品的需求相应地增加端口的数量及布局的位置,形成面排布的过程。目前RDL 技术主要应用在晶圆级封装、2.5D/3D 和 Chiplet封装等,不仅完美地解决了高密度集成芯片的 I/O间距受限的问题同时也利用 RDL 取代基板实现芯片与外界的电性连接,以此降低封装体的体积。

TSV

TSV(Through Silicon Via)技术是一种穿透硅的通孔技术,简称硅通孔技术。该技术利用硅通孔结构,使芯片与芯片之间、芯片与基板之间实现垂直连接,从而有效缩短传导线路,降低功耗,提高芯片的运行速度。应用在存储芯片时,可以通过增加芯片堆叠数量,实现高带宽、大容量存储;其次,还可以实现不同功能芯片之间的互连,使单个封装体具有更多的功能。TSV 工艺主要包括通孔刻蚀、通孔薄膜淀积(绝缘层、阻挡层、种子层的沉积)、通孔填充、化学机械抛光(CMP)、晶圆减薄和 RDL 与微凸点制作等关键技术。

RDL/Bumping,TSV 在三维闪存封装中的可能应用方案

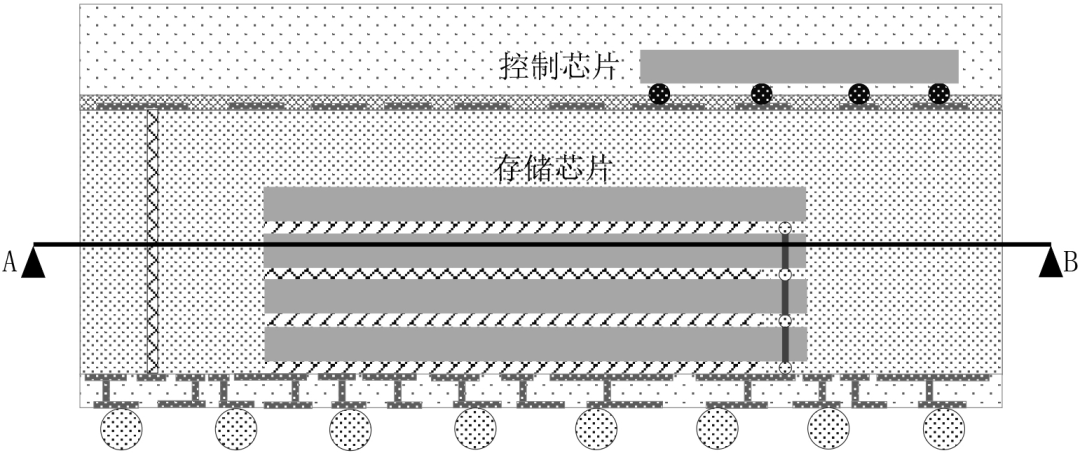

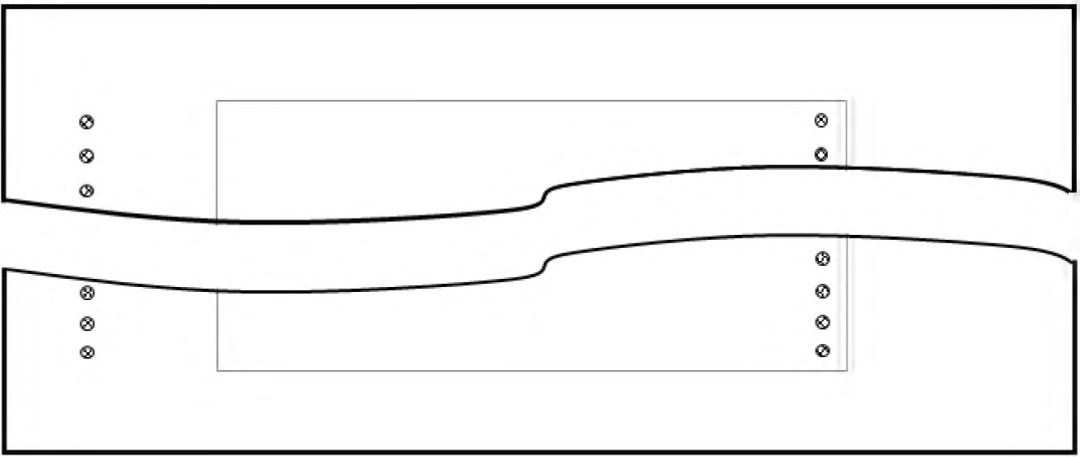

相比 DRAM 产品,将先进封装技术应用到NAND 产品上,并实现商用的案例几乎很少,本文基于 NAND 芯片的功能和先进封装技术,对其应用做了一些设想,其中一个方案如图 3 所示。将 NAND芯片以垂直方向堆叠,利用 TSV 技术制作的通孔导电结构代替传统的 WB 打线,用微 Bumping 来实现芯片与芯片、芯片与 RDL 之间的互连,并利用Molding 工艺对整个封装体进行第一次塑封。然后将控制芯片以倒装的形式键合在另一 RDL 上,并且通过导电结构实现两层 RDL 的互连,以此实现内部异质芯片电路的连接。该结构难点主要在于分层的问题,因为 TSV 中导电结构的金属 Cu 的热膨胀系数(1.8x10-5℃-1)和 Si 的热膨胀系数(3x10-6℃-1)差距较大,当该结构热量不能及时散出时,金属层 Cu 和Si 表面可能发生分层,从而导致产品的失效。

图 3(a) 封装体的剖面结构示意图

图 3(b) 封装体 AB 截面的俯视图

本文内容源于【中国集成电路】

审核编辑:汤梓红

-

三维曲线加速度2013-10-23 0

-

如何使用labview根据XYZ坐标实时绘制三维曲线2014-04-12 0

-

如何用labview在三维图里画多条线?2014-11-08 0

-

高速摄像系统在三维运动康复中的应用案例2015-09-02 0

-

关于三维曲面找坐标点的问题2015-10-18 0

-

三维逆向工程的成果及应用案例2016-03-02 0

-

高速相机在三维运动康复中的应用案例2016-06-07 0

-

三维触控技术突破“二向箔”的束缚2016-12-19 0

-

三维快速建模技术与三维扫描建模的应用2018-08-07 0

-

三维设计应用案例2019-07-03 0

-

结合三维可视化的智慧电厂方案设计2020-06-28 0

-

三维立体数字沙盘是是什么?2020-08-28 0

-

晶圆级三维封装技术发展2020-12-28 0

-

安徽三维动画制作和二维动画有哪些区别呢?(一)2022-01-22 0

-

先进封装技术在三维闪存产品中的应用探讨2023-12-14 561

全部0条评论

快来发表一下你的评论吧 !