静电放电问题典型案例分析

描述

这期我带大家继续进行静电放电问题典型案例分析,前篇文章分别介绍了复位信号、DC-DC芯片设计问题引发的静电放电问题;这篇文章将介绍软件设计、PCB环路设计引发的静电放电问题;话不多说,还是通过两个案例展现给大家。

一、环境温度控制器接触放电±15KV测试出现黑屏等问题案例分析

产品形态图

1. 问题现象描述

某猪舍智能环境控制器产品依据GB/T17626.2标准进行接触放电±15KV测试时,当对温度探头的金属外壳进行±15KV接触放电测测试时,显示屏出现黑屏、花屏等现象且无法自动恢复,按复位键没有作用,需要断电重启,方可以恢复,不符合A等级判定标准。

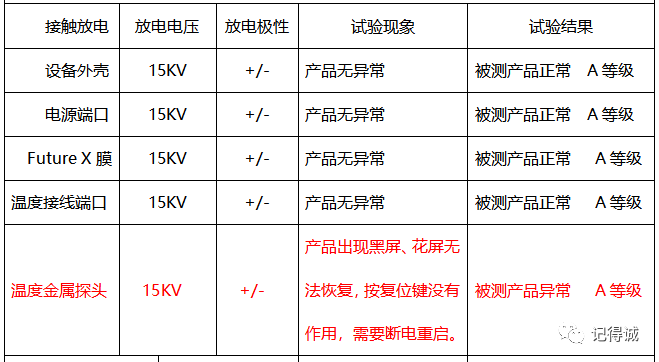

试验结果如表:

2. 问题现象分析

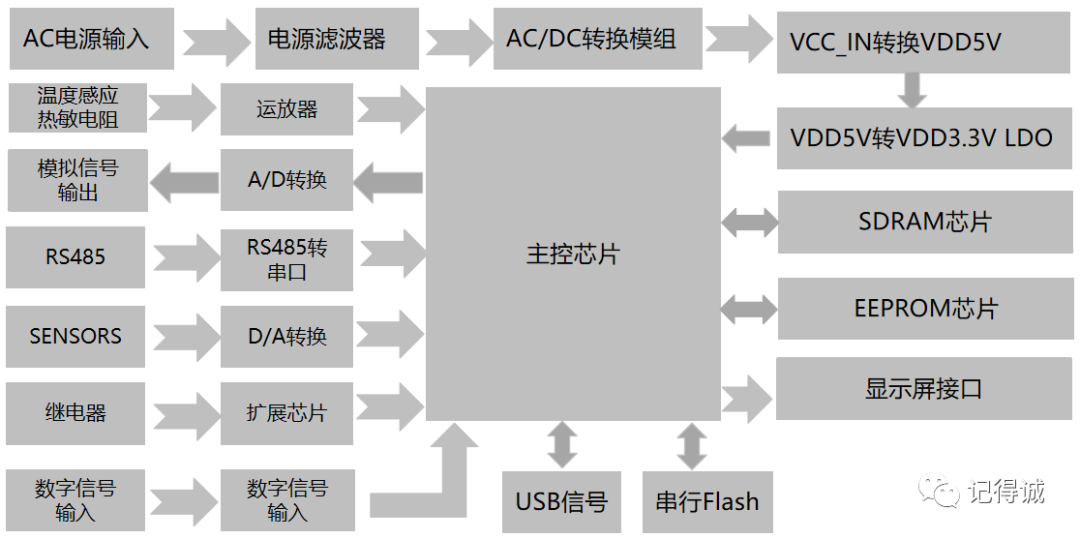

产品原理框图

对样机进行±15KV接触放电摸底测试,其问题现象同反馈相同,排除测试场地、测试仪器差异的可能性。静电放电测试不通过的测试点是温度金属探头,其它测试点均可测试通过。

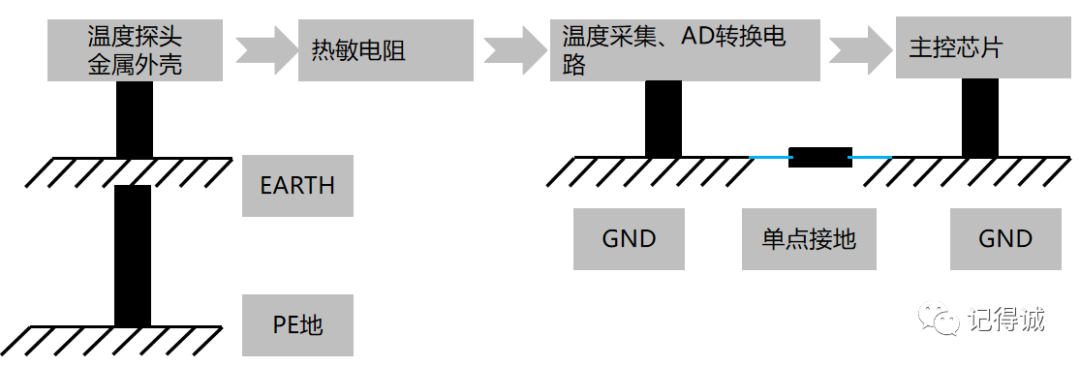

温度金属探头外壳是直接连接在EARTH,EARTH是直接连接到PE地;金属探头的内部是热敏电阻,热敏电阻通过信号采集转换为AD信号输入到主芯片,由芯片判断后调整控制环境温度。温度采集、AD转换电路与主控芯片之间采用单点接地,与温度金属探头外壳的PE地完全隔离,即整个系统是浮地的方式。

3. 问题分析验证过程

3.1 根据温度金属探头连接图,尝试从如下试验协助判断静电干扰路径:

将温度探头内部热敏电阻连接的电路靠近板端断开,只保留温度探头的金属外壳连接到EARTH线,对温度金属探头接触15KV放电,不良现象很快重现,对策无任何的改善效果,判断静电放电干扰不是从信号路径耦合干扰内部电路的。

温度探头的金属外壳是直接接PE地,对PE地直接接触放电15KV,原则上静电电流很快泄放到电网或者大地,且PE地与系统GND之间无物理连接,不存在传导耦合的路径。

通过排除试验确认静电放电干扰不是通过传导耦合的路径干扰系统内部敏感电路,判断是通过空间辐射的方式干扰内部敏感电路,空间辐射方式主要有磁场、电场、电磁场。

3.2 初步判定为静电放电电流磁场辐射,根据磁场耦合的机理,需要分析寻找到系统内部的敏感电流环路,并增加抑制对策方可解决

根据磁场耦合的机理可知,构成磁场耦合必须有环路,环路阻抗相对较低,否则就无法形成磁场耦合。环路面积越大耦合能力越强,反之环路面积越小耦合能力相对较弱。

功率信号的环路面积、高速信号的环路面积控制很容易引起工程师重视,在PCB设计中进行有效管控,而控制信号的回流路径,即信号环路则很容易被工程师忽略;恰恰控制信号构成的环路面积极容易感应静电放电干扰,导致系统工作异常。

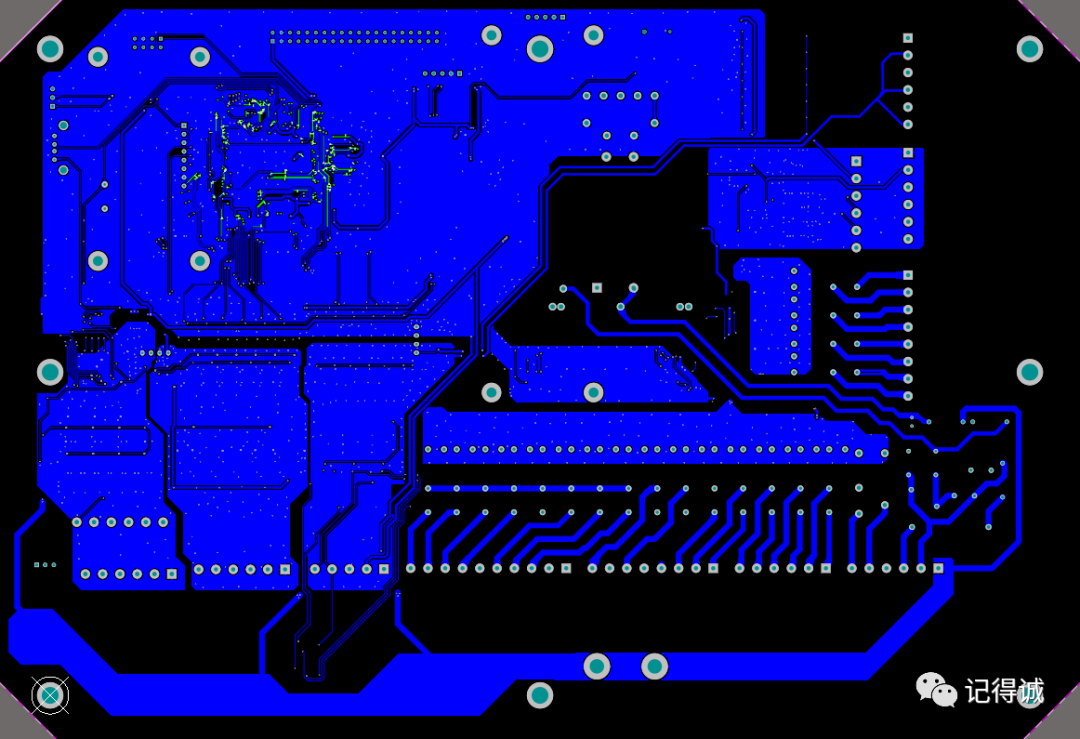

对PCB Layout图进行深入分析,发现地平面分割非常严重,且模块与模块之间或采用单点接地,或因地分割导致信号环路面积失控,都为静电放电干扰耦合提供了条件。

3.3 PCB Layout设计分析

系统出现显示花屏、黑屏现象,而不是温度采集信息错误,则说明主控MCU芯片受到干扰,导致系统工作出现异常,显示花屏、黑屏、宕机现象。

静电放电干扰是通过空间耦合的方式进入主控芯片,主要与信号环路面积、PCB布线长度高度相关,需要重点排查PCB Layout设计。

主控芯片与各个模块电路互连时,信号从远端到接受端再通过参考地平面返回到远端构成的信号环路面积越小,耦合外部静电放电干扰的能力就越弱,反之则越强。地平面无规划性的分割,是很容易噪声信号回流路径的失控,而引发信号环路面积的失控。

主控板PCB Layout图

3.4 温度采样电路模块信号环路面积缩小试验

沿着温度采样电路信号传输轨迹,将其邻层参考地平面保持完整,达到信号环路面积最小化的规范要求。

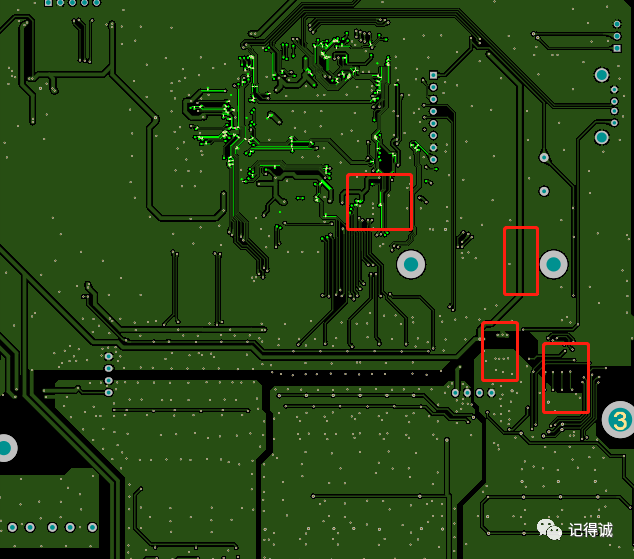

具体操作是使用金属铜箔,在信号轨迹下方将分割的参考地平面连接起来,构成相对完整的参考地平面,下图红色方框处底层使用铜箔连接起来。

温度采样电路信号轨迹参考地平面完整性措施

审核编辑:汤梓红

-

系统层级静电放电与芯片层级静电放电有什么差异2019-07-25 0

-

静电发生器,静电放电模拟仪,静电枪手册2011-11-25 1367

-

电缆对静电放电的影响分析2020-10-23 0

-

静电放电抗扰度对手机的影响2011-10-20 3396

-

静电放电原理2016-12-30 829

-

静电放电及防护基础知识2017-11-23 1136

-

模拟分析静电放电(ESD)事件2019-08-11 8994

-

静电放电测试实验分析2020-11-19 8090

-

静电放电问题案例分析资源下载2021-07-01 776

-

ESD静电放电问题仿真分析2023-06-30 2938

-

静电放电的测试方法 静电放电问题整改案例2023-09-05 538

-

静电放电电流环路的干扰机理分析2023-10-30 1190

-

【电磁兼容技术案例分享】静电放电(ESD)整改案例分析2023-11-03 847

-

静电放电发生器原理 静电放电发生器的主要用途 静电发生器怎么使用2023-11-23 957

-

静电放电问题典型案例分析2023-11-29 414

全部0条评论

快来发表一下你的评论吧 !