ADC架构的无采样保持(SHA-less)结构分析

模拟技术

描述

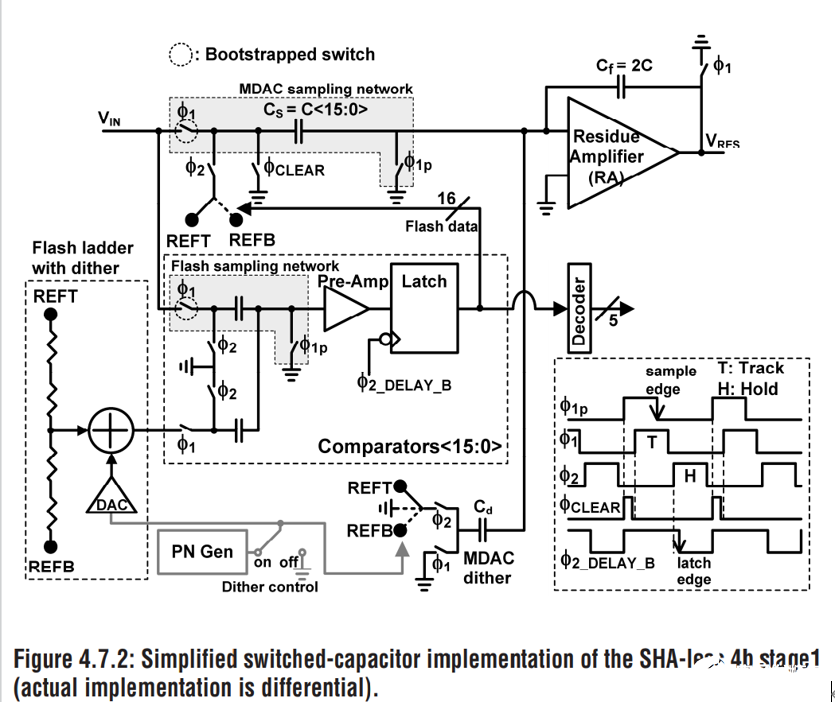

通常来说pipelined ADC的每个子级需要一个SHA(sample/hold Amplifier)来对上一级的残差进行采样,但是在典型的运放共享的结构中,这个SHA往往花费了20%-30%的总体功耗[1](大的负载及带宽要求),同时由于它存在于每个子级的最前端,其非线性和噪声会经过后面的流水级逐级放大,这也极大程度影响整个ADC的非线性及动态范围,因此实际上现如今pipelined ADC的架构往往采用无采样保持(SHA-less)结构,此方法由文献[2]提出,采用此方法的其中一个的电路架构如下图所示[3]。

可以看到,此结构移除了SHA来实现实现低功耗设计,上面为一个开关电容运算放大器实现的MDAC,下面为子ADC,比较器为离散时间的开关电容比较器。图中给出了时序图,我们简单说明一下工作时序,在φ1高电平,MDAC和比较器同时对输入进行采样,同时φ1p也为高电平使得输入端保持为共模电平,φ1p先断开以消除开关的沟道电荷注入效应(Razavi书中有解释,注意反相输入节点浮空),随后φ2控制开关闭合,比较器开始工作,预放大器建立起一定的差分电压送至latch,φ2_DELAY_B为复位时钟,在φ2为高电平后留出预放大器的延迟时间,随后φ2_DELAY_B变为低电平,latch进入锁存建立阶段,通过快速正反馈将差分输入放大并锁存,编码后输出至MDAC的控制开关。

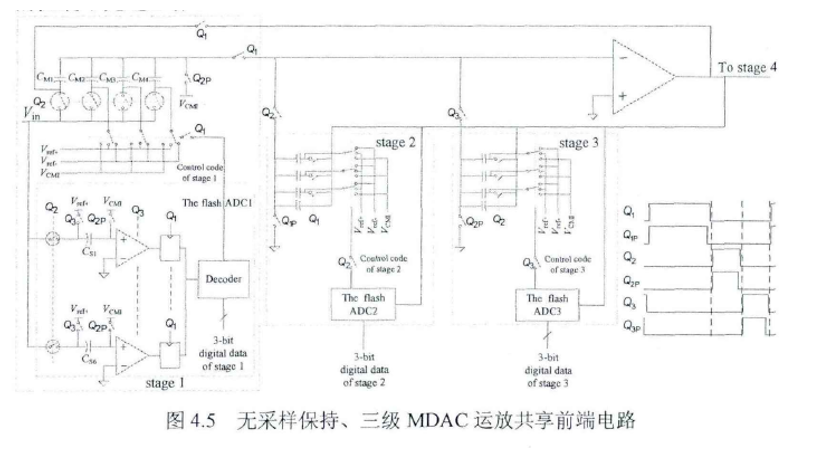

这种结构依然存在一些弊端, MDAC和子ADC的信号输入路径可能存在不匹配,也就是开关的RC时间常数的不匹配,导致在输入频率很高时,可能导致采样的信号存在很大的差异(孔径误差)[2],这个问题可以通过在MDAC和比较器的采样端使用相同的拓扑结构并合理设计采样开关的宽长比来实现RC时间常数的匹配,第二就是速度受限[1],通过上面的时序分析也看到在采样相和放大相之间存在一个额外的比较时间,只有比较器的输出建立完成之后MDAC的开关才会拨到正确的参考电压完成运算,这个问题可以通过将采样相分为两段,在第二段进行比较来实现。一种将采样相分段的结构及时序如下图所示[4]。

审核编辑:黄飞

-

高速ADC模拟输入架构类型详解2018-01-23 0

-

AD9233-105EBZ,用于评估ADC AD9233,具有高性能采样保持放大器(SHA)和片内基准电压源2019-11-11 0

-

采样保持放大器(SHA)工作原理与基本操作规格2022-04-06 0

-

高速ADC模拟输入架构类型介绍2023-12-18 0

-

ADC需要采样保持器的原因及采样ADC的工作原理2021-04-28 24437

-

AD783:高速单片采样保持放大器(SHA)数据表2021-04-14 496

-

SHA3:采样保持放大器过时数据表2021-04-22 605

-

SHA5:采样保持放大器过时数据表2021-04-23 432

-

SHA1144:过时的高分辨率14位采样保持放大器数据表2021-05-20 526

-

SHA6:采样保持放大器过时数据表2021-05-26 441

-

SHA1A:采样保持放大器过时数据表2021-05-26 469

-

SHA4:采样保持放大器过时数据表2021-05-26 436

-

SHA1134:通用采样保持放大器过时数据表2021-05-26 449

全部0条评论

快来发表一下你的评论吧 !