Vivado常见Warning问题解决方法

描述

目录

1、[Synth 8-2611] redeclaration of ansi port XXX is not allowed

2、[Constraints 18-619] A clock with name 'InClk' already exists

3、 [Synth 8-2611] redeclaration of ansi port InClk is not allowed

4、 [Vivado 12-1017] Problems encountered:

5、 [Constraints 18-5210] No constraint will be written out.

6、[Common 17-1548] Command failed: can't read "output_ports": no such variable

7、[filemgmt 20-2001] Source scanning failed (terminated by user) while processing fileset "sources_1" due to unrecoverable syntax error or design hierarchy issues. Recovering last known analysis of the source files.

8、[Synth 8-1849] concatenation with unsized literal; will interpret as 32 bits

9、[Constraints 18-549] Could not create 'SLEW' constraint because cell 'OBUFDS_inst' is not directly connected to top level port. 'SLEW' is ignored by Vivado but preserved inside the database.

1、[Synth 8-2611] redeclaration of ansi port XXX is not allowed

程序中重复声明输出端口信号

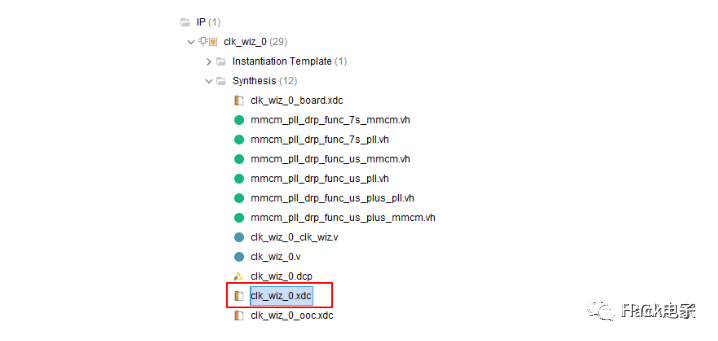

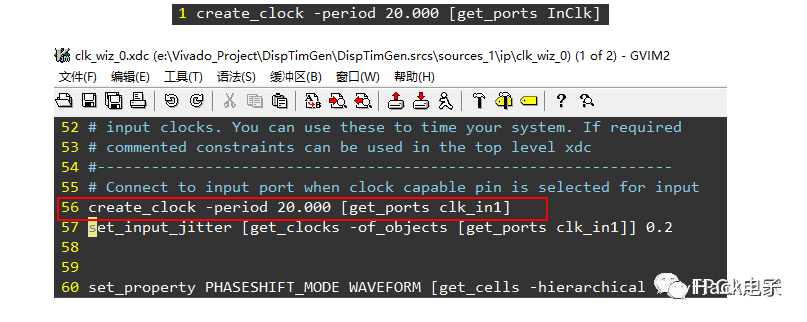

2、[Constraints 18-619] A clock with name 'InClk' already exists

描述:

在约束文件XDC(SCOPED_TO_REF、SCOPED_TO_CELLS)中使用“create_clock -name”约束时,在打开综合设计或实现设计时,或者在综合或实现期间,可以观察到以下警告。

[Constraints 18-619] A clock with name 'InClk' already exists overwriting the previous clock with the same name. ["E:/Vivado_Project/DispTimGen/DispTimGen.srcs/constrs_1/new/DispTimGenTiming.xdc":1]

解决方案:

如果时钟约束已存在于 IP XDC 中,则无需在顶级 xdc 中写入约束。

clk_wiz_0.xdc文件中如下已经约束InClk;

当设计中有多个作用域单元/引用的实例时会显示此警告,因此多次读取相同的“create_clock -name”约束。

如警告消息中所示,仅最后一个读取保留,所有其他读取都丢失。

推荐的解决方案是从 create_clock 命令中删除 -name 选项。

如果未使用 -name 选项,系统会根据网络名/位置创建唯一名称。

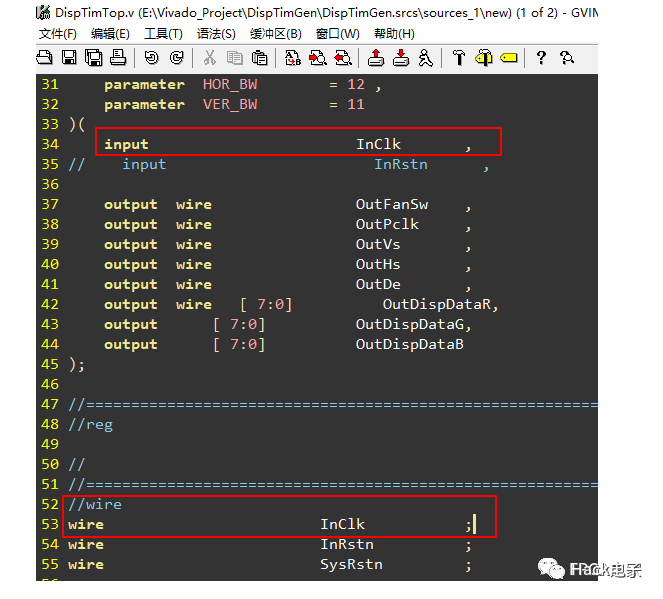

3、 [Synth 8-2611] redeclaration of ansi port InClk is not allowed

输入端口不需要申明wire型

4、 [Vivado 12-1017] Problems encountered:

[Vivado 12-1017] Problems encountered: Failed to delete one or more files in run directory E:/Vivado_Project/DispTimGen/DispTimGen.runs/synth_1

描述:保存Project文件夹为可读模式

解决方案:设置保存Project文件权限,设置为读写模式

5、 [Constraints 18-5210] No constraint will be written out.

解决方案:Vivado 中的一个已知错误,将在 2020.1 中修复(可以忽略)

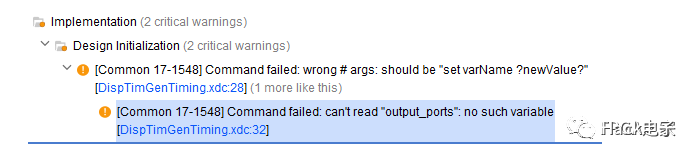

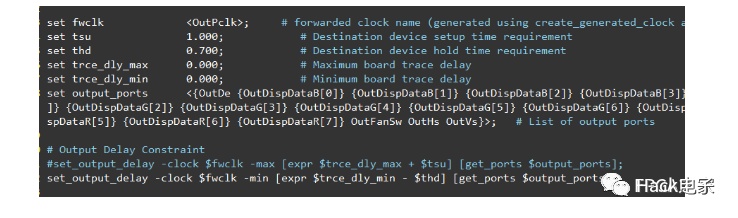

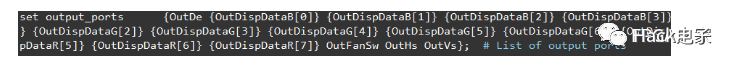

6、[Common 17-1548] Command failed: can't read "output_ports": no such variable

描述:set_input_delay时,端口命名错误

解决方案:set_input_delay端口命名时,将< >去掉

7、[filemgmt 20-2001] Source scanning failed (terminated by user) while processing fileset "sources_1" due to unrecoverable syntax error or design hierarchy issues. Recovering last known analysis of the source files.

重启软件可解决

8、[Synth 8-1849] concatenation with unsized literal; will interpret as 32 bits

问题在了 {} 里面的 “0” 了,原来在拼接符中的0,如果不指定其位数,则软件会将其默认为32bit,如果这个0不在高位,那么在进行赋值的时候就会形成了将一个很多位的数据赋值给了2bit的BramRst。

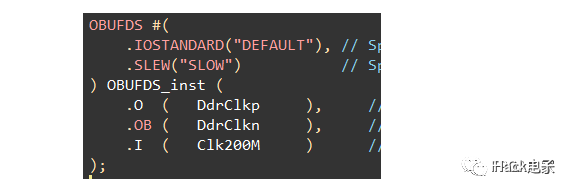

9、[Constraints 18-549] Could not create 'SLEW' constraint because cell 'OBUFDS_inst' is not directly connected to top level port. 'SLEW' is ignored by Vivado but preserved inside the database.

约束 [18-549] 无法创建“SLEW”约束,因为单元“OBUFDS_inst”未直接连接到顶级端口。Vivado 会忽略“SLEW”,但会保留在数据库中。

注意:INBUFDS与OBUFDS这类源语言是必须要有硬件连接的In或Out接口!

审核编辑:汤梓红

-

PADS2007问题解决方法2012-04-25 0

-

通信电源系统维护要求及常见问题解决方法(6)2012-08-20 0

-

Linux嵌入式系统初学者的常见问题解决方法大全2018-10-16 0

-

Xavier入门踩坑PWM问题解决方法2022-01-10 0

-

分享一篇15547电路问题解决方法的记录2022-01-25 0

-

电视卡常见问题解决方法(驱动问题等)2007-12-06 2326

-

爱普生打印机清零问题解决方法2010-01-14 2613

-

频展示台自我维护及常见问题解决方法2010-02-08 1426

-

通信电源系统维护要求及常见问题解决方法2011-11-08 671

-

protel 99se 使用技巧以及常见问题解决方法2012-09-13 1763

-

基于MPC7448的高端PowerPC常见问题解决方法2013-09-23 981

-

通用智能后视镜常见问题解决方法2015-11-17 1193

-

Jlink V8灯不亮USB无法识别及克隆版问题解决方法资料下载2018-02-27 884

-

CAD的常规操作及常见问题解决方法2022-07-12 1222

-

PCB压合问题解决方法2024-01-05 406

全部0条评论

快来发表一下你的评论吧 !