怎样减少路径上的LUT个数使速度更快呢?

描述

对FPGA设计而言如果想速度更快则应当努力减少路径上LUT的个数,而不是逻辑级数。如果想面积更小则应当努力减少LUT的个数而不是逻辑门数。

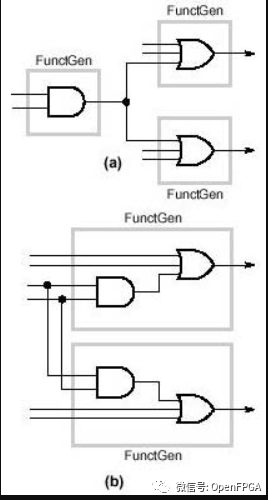

如下图:

采用图a结构,我们知道一个LUT只有一个输出,因此前面的2输入与门要占用一个LUT 后面的2个三输入或门要各占用一个LUT 总共占用3个LUT LUT级数是2级。

采用图b结构,其实现结果等效于图a结构,虽然增加了一个2输入与门并且逻辑级数与图a一样也是2级但我们根据LUT特点它只占用2个LUT:

2输入与门和3输入或门由一个LUT实现LUT级数只有1级,这就是一个门数增加逻辑级数未变但资源占用减少速度更快典型案例

审核编辑:刘清

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

LUT实现的逆变器真的是FPGA上的逆变器吗?2019-01-29 0

-

Spartan 3器件上的专用乘法器路径时间随着阶段数量的增加而减少2019-06-13 0

-

如何让这个设计通过减少颜色量可能更快2019-07-23 0

-

Kintex 7输入IO焊盘和FF(片寄存器)之间的额外LUT是什么2020-07-16 0

-

请问如何使FRAM MCU速度更快所需功耗最低?2020-12-30 0

-

怎样去调好速度环呢2021-09-29 0

-

怎样更快地去下载STM32的PACK包呢2021-10-22 0

-

怎样去解决STM32串口第一个数据丢失的问题呢2021-12-09 0

-

怎样去解决NVIC_EnableIRQ使能无法进行的问题呢2022-01-18 0

-

如何更快的使硬件数据传到webservice服务接口呢2022-02-22 0

-

怎样使使Android板子HDMI输出4K呢2022-03-03 0

-

使用ST的FOC,给定3000速,速度波动在60左右速,有什么办法减少速度波动2022-10-20 0

-

求助前辈们Verilog lut个数的问题2022-12-13 0

-

网线接口在PCB板上该如何连线才使信号传输速度更快呢?2023-04-07 0

-

需要更快的速度:CAN FD2022-11-07 196

全部0条评论

快来发表一下你的评论吧 !