MCU内部SRAM的ECC初始化竟可由ROM完成

描述

大家好,我是痞子衡,是正经搞技术的痞子。今天痞子衡给大家分享的是i.MXRT1170内部RAM的ECC初始化工作可全部由ROM完成。

痞子衡之前写了三篇文章 《M7 FlexRAM ECC》、《M4 L-MEM ECC》、《MECC64》 分别介绍了 i.MXRT1170 片上 2MB RAM 的不同 ECC 控制器用法,尤其是第三篇文章最后介绍了当 MECC64 特性被激活之后,BootROM 虽然使能了 MECC1&2 但并没有一步到位初始化相应的全部 RAM 区域(仅初始化了 48KB ROM RW 区),这给后续调试和应用开发带来了一定隐患。

难道 BootROM “挑了事”就这么不负责任吗?当然不是!我们需要主动让 BootROM 负全责,今天痞子衡就聊一聊这个话题:

一、RAM ECC初始化相关Fuse位

前面的文章讲了 Fuse MECC_ENABLE bit 主要控制 MECC64 模块是否被激活,但其实它还有另外一层关于 RAM ECC 初始化控制。痞子衡在此列出了如下跟 RAM ECC 初始化相关的全部 Fuse bit,其中最核心的是 ROM_ECC_PRELOAD_POR bit,这个 bit 决定是否在芯片 POR 上电时让 ROM 去做额外的 RAM ECC 初始化工作。

Fuse 0x840[2] - MECC_ENABLE bit, 是否开启MECC模块(默认0即不开启)

ROM做ECC初始化是否包括M7 FlexRAM OCRAM、M4 TCM、M4 OCRAM(默认0即不包含)

Fuse 0x840[15] - TCM_ECC_ENABLE bit, ROM做ECC初始化是否包括M7 TCM(默认0即不包含)

Fuse 0x850[7] - OCRAM1_DISABLE bit, ROM做ECC初始化是否包括扣去ROM RW区之后的OCRAM1(默认0即包含)

Fuse 0x850[6] - OCRAM2_DISABLE bit, ROM做ECC初始化是否包括OCRAM2(默认0即包含)

Fuse 0x950[0] - ROM_ECC_PRELOAD_POR bit,是否在POR时让ROM去初始化RAM ECC(默认0即不做)

上述区域里关于 OCRAM1 ECC 初始化需要特别说一下,因为前 48KB 是 ROM RW 区,其在 ROM 刚执行就被初始化过了,这里 ROM_ECC_PRELOAD_POR bit 控制的初始化就不再重复操作 ROM RW 区了。因为如果包含这个区域,那就会破坏 ROM 程序的正常执行了。

二、检验ROM做RAM ECC初始化工作

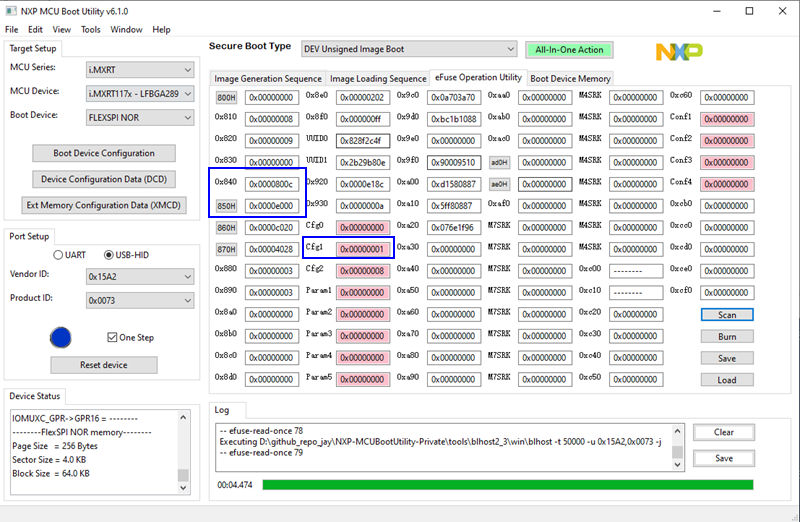

为了检验 BootROM 是否很好地完成了 RAM ECC 初始化工作,痞子衡找了块 RT1170 板卡使用 MCUBootUtility 工具将 Fuse 0x840、0x850、0x950 全部设成 RAM ECC 初始化使能状态:

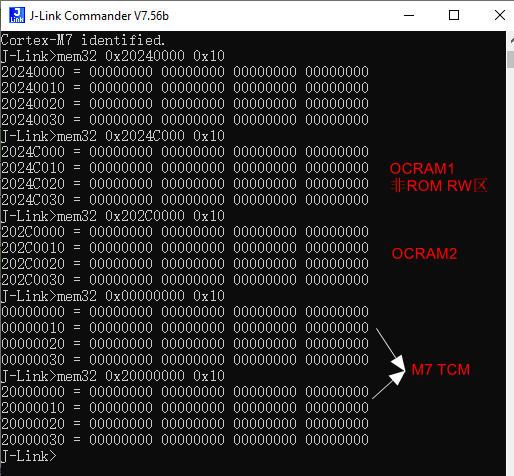

芯片保持 Serial Downloader 模式,挂上 JLink 读取内存,好家伙,内部 RAM 全部整齐划一地保持全 0 队形,不再是随机值了,看起来 ROM 很好地完成了 ECC 初始化工作。

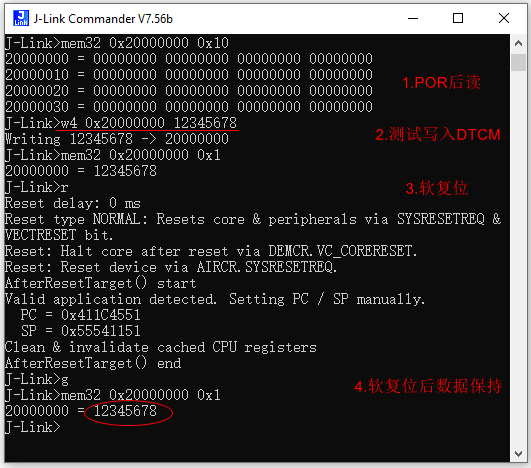

这时候尝试在 DTCM 里写入一些测试数据,然后做软件复位,再回读发现测试数据依然保持着,这说明 ROM 只在 POR 硬复位时做一次 RAM ECC 初始化,其后发生软复位导致 ROM 再执行时就会跳过 ECC 初始化。

至此,i.MXRT1170内部RAM的ECC初始化工作可全部由ROM完成痞子衡便介绍完毕了,掌声在哪里~~~

审核编辑:汤梓红

-

MCU重新上电后,如何进行ECC初始化?2024-03-19 0

-

在modelsim中初始化ROM2013-05-13 0

-

ISE中ROM初始化文件(.coe)的建立2015-04-29 0

-

关于ISE调用ROM IP核并初始化的问题?2015-09-29 0

-

FPGA片内ROM初始化文档创建2019-04-08 0

-

SRAM在芯片复位时不初始化的办法2020-11-27 0

-

如何使用FPGA内部的ROM以及程序对该ROM的数据读操作2021-01-07 0

-

SRAM上的ECC是否默认启用?哪些代码使SRAM上的ECC启用?2023-03-27 0

-

是否没有必要初始化SRAM_L因为它不受ECC保护?2023-03-31 0

-

S32K146 ECC初始化器,为什么不初始化堆栈空间?2023-04-20 0

-

求助,MCU重新上电后如何进行ECC初始化?2023-08-07 0

-

蜂鸟内部通用寄存器为什么不做复位初始化?2023-08-16 0

-

FPGA的ROM初始化问题讨论2012-02-08 5279

-

四种常见的ROM、RAM初始化文件格式2018-06-29 11182

全部0条评论

快来发表一下你的评论吧 !