基于FPGA的轻量级CAN总线控制器

描述

0、CAN总线介绍

1、CAN权威文档

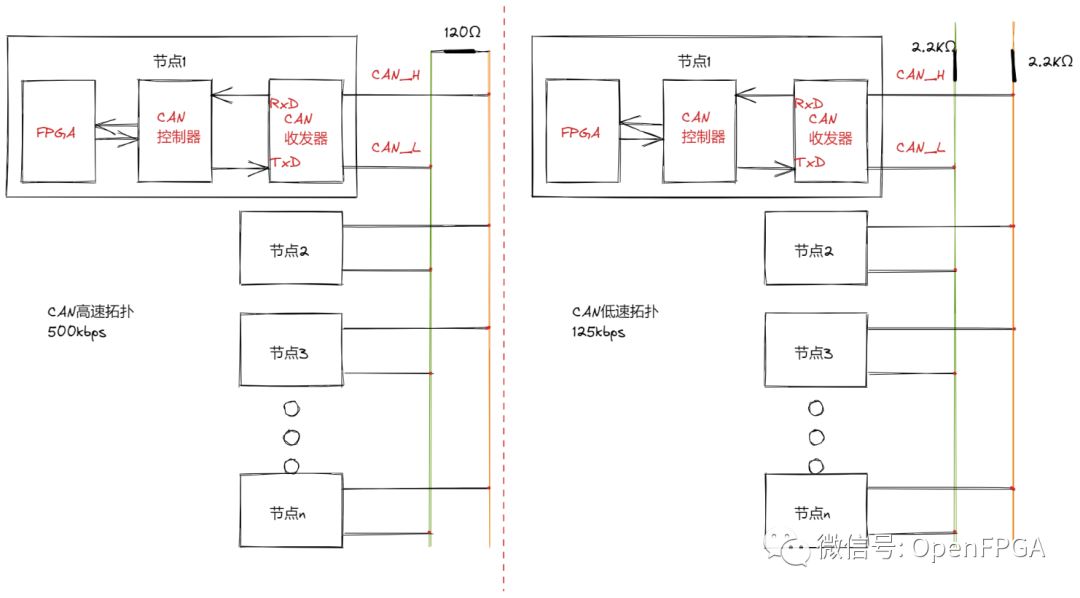

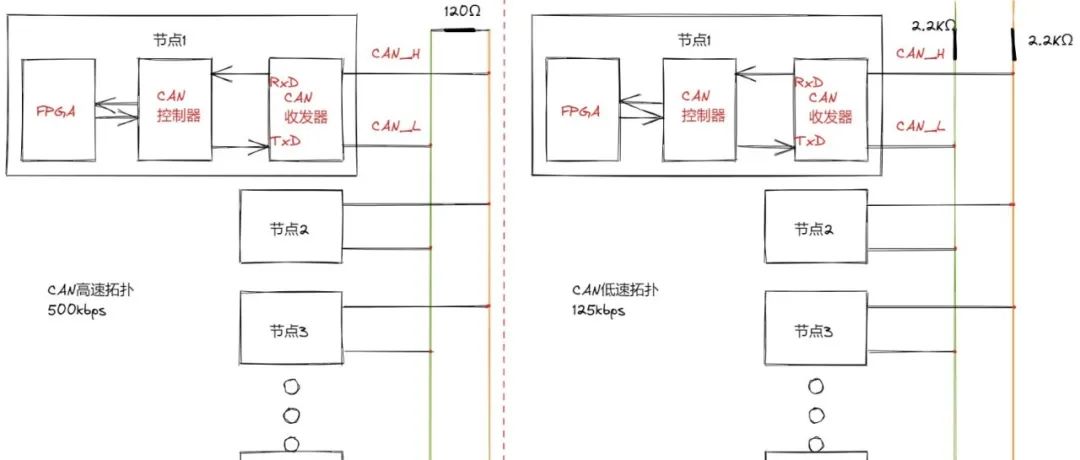

CAN总线有两个ISO国际标准:ISO11898 和 ISO11519。其中:

ISO11898 定义了通信速率为 125 kbps~1 Mbps 的高速 CAN 通信标准,属于闭环总线,传输速率可达1Mbps,总线长度 ≤ 40米。

ISO11519 定义了通信速率为 10~125 kbps 的低速 CAN 通信标准,属于开环总线,传输速率为40kbps时,总线长度可达1000米。

ISO 11898 文档在这里

3、【小梅哥FPGA】使用FPGA实现CAN通信的例子(NIOS+CAN IP)

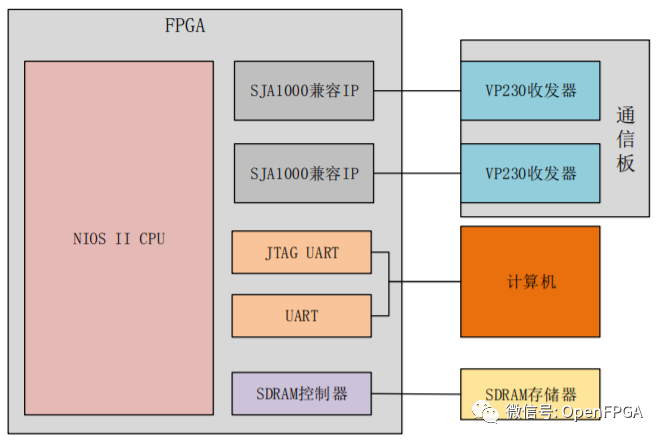

这是小梅哥FPGA开发板上的实例,之所以放到第一个是因为这是目前FPGA实现CAN通信的比较完美的解决方案,单纯使用硬件描述语言的IP,会有一些不可预知的BUG,但是使用软核处理器是比较完美的。

上图就是整个项目的系统方案,也很好理解,就不过多赘述了。

SJA100就是CAN控制器;

VP230就是CAN收发器。

PS:代码在上诉链接中。

4、liteCAN

基于 FPGA 的轻量级CAN总线控制器

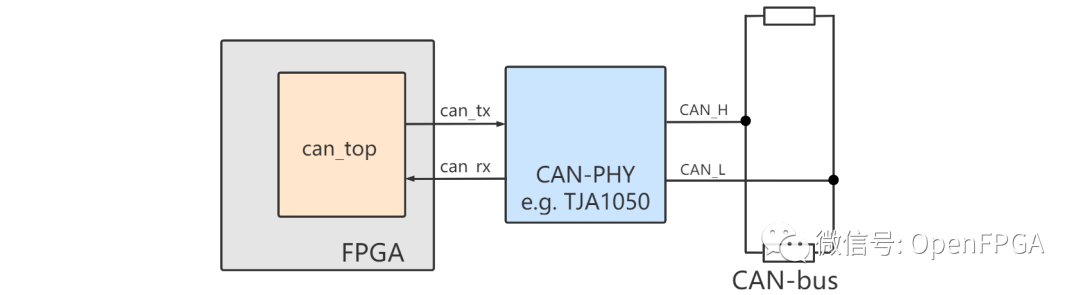

此项目实现的是CAN控制器,CAN收发器还是需要外挂。

简介

CAN总线作为工业和汽车领域最常用的通信总线,具有拓扑结构简洁、可靠性高、传输距离长等优点。CAN总线的非破坏性仲裁机制依赖于帧ID,CAN2.0A和CAN2.0B分别规定了11bit-ID(短ID) 的标准帧和29bit-ID(长ID) 的扩展帧,另外,还有远程帧这种数据请求机制。关于CAN总线的更多知识可以参考这个科普文章。

CAN总线的复杂机制决定了控制器设计的复杂性。本库实现了一个轻量化但完备的CAN控制器,特点如下:

本地ID可固定配置为任意短ID。

发送 : 仅支持以本地ID发送数据长度为4Byte的帧。

接收 : 支持接收短ID或长ID的帧,接收帧的数据长度没有限制 (即支持 0~8Byte ) 。

接收帧过滤 : 可针对短ID和长ID独立设置过滤器,只接收和过滤器匹配的数据帧。

自动响应远程帧 : 当收到的远程帧与本地ID匹配时,自动将发送缓存中的下一个数据发送出去。若缓存为空,则重复发送上次发过的数据。

平台无关 :纯 RTL 编写 (SystemVerilog),可以在 Altera 和 Xilinx 等各种 FPGA 上运行。

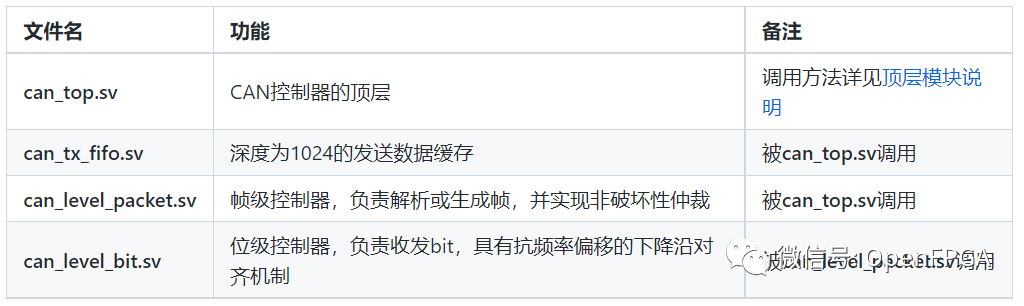

设计文件说明

设计相关的4个文件在 RTL 文件夹中,各文件功能如下表。你只需将以上4个文件包含进工程,就可以调用can_top.sv进行更高层次的CAN通信业务的二次开发。

此项目非常完整,项目由中文说明,完备的TB及测试方案。

5、CAN-fpga

项目没有任何介绍,看文件结构,是基于Quartus II建立的,结构和上一项目完全没什么区别。整个项目应该是完备的,有兴趣可以看看。

6、sja1000

这个就是Verilog编写的外挂SJA100的驱动程序,这里就不过多介绍了。

7、Click_MCP25625

这是MCP25625(控制器+收发器集合)的SPI驱动(ARM单片机的)。

这个项目和这个功能一样,就不展开描述了。

USB-CAN(调试利器)

因为本期没几个开源项目,所以这里在推荐几个开源的USB-CAN方案,大部分都是可以直接打板使用的。

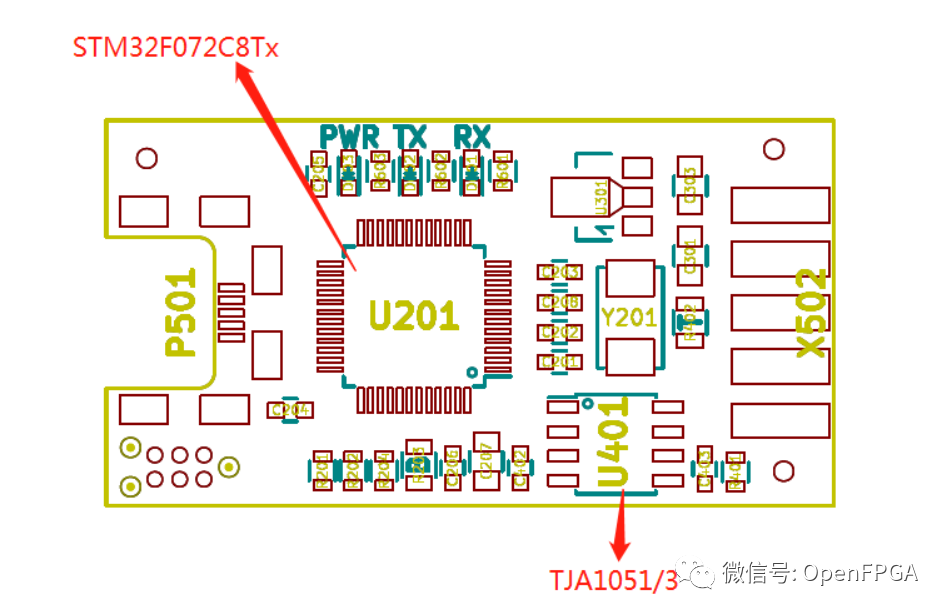

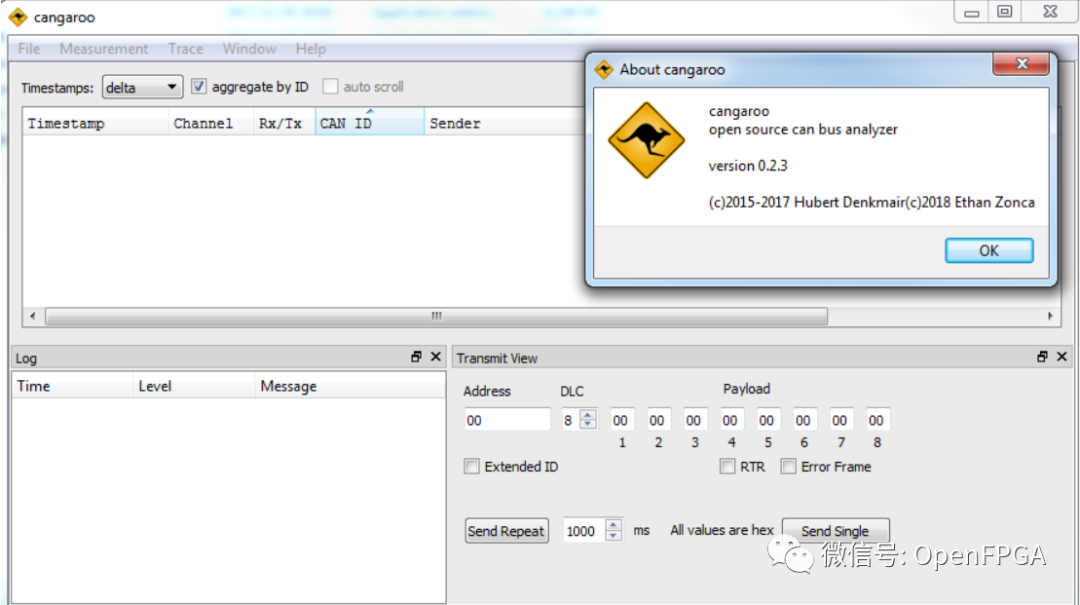

一、stm32f0 + CAN收发器TJA1051/3

ta有完全开源的软硬件及上位机支持,支持windos和linux Stock can并且都免驱哦。且支持Python。

上述的方案某宝上也有成品。

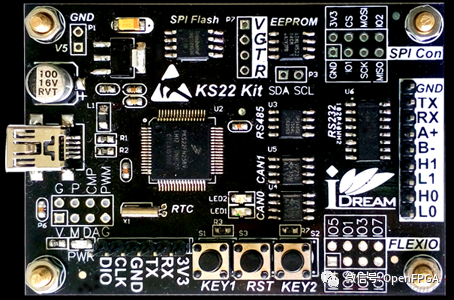

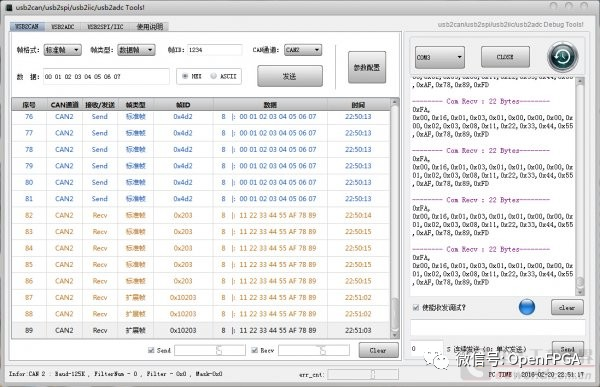

二、KS22方案

相关文档及上位机:

三、open-usb-can

文档很完备。

该项目是基于 ATMega32U2 和 MCP2515 SPI CANBus 控制器的 USB 转 CANBus 接口。

最后,还是感谢各个大佬开源的项目,让我们受益匪浅。后面有什么感兴趣方面的项目,大家可以在后台留言或者加微信留言,今天就到这,我是爆肝的碎碎思,期待下期文章与你相见。

审核编辑:汤梓红

-

CAN总线控制器与DSP的接口2018-12-03 0

-

基于FPGA的CAN总线通信系统2012-08-11 0

-

关于FPGA的can总线嵌入式设计2013-02-06 0

-

CAN总线控制器Verilog代码2008-05-20 1008

-

基于CAN总线的悬浮控制器监控终端的设计2010-01-25 629

-

基于STM32和FPGA的CAN总线运动控制器的设计2013-01-31 1114

-

FPGA实现CAN总线控制器源码2016-06-07 854

-

基于FPGA和CAN控制器MCP2515设计惯导系统的CAN总线2016-07-13 1298

-

基于DSP_FPGA与CAN总线的跟踪控制器设计2017-10-21 613

-

基于FPGA与CAN总线控制器的自适应汽车前照灯系统的设计2018-12-10 3115

-

如何使用FPGA进行CAN控制器软核的设计与实现2019-07-19 1161

-

如何用FPGA实现CAN总线通信控制器2022-07-29 2292

-

基于FPGA的CAN总线控制器的设计(附代码)2022-11-14 1153

-

基于FPGA的CAN总线控制器的设计2023-05-18 922

-

基于FPGA的CAN总线通信节点设计2023-06-18 2007

全部0条评论

快来发表一下你的评论吧 !