GD32F1硬件开发指南之复位电路

描述

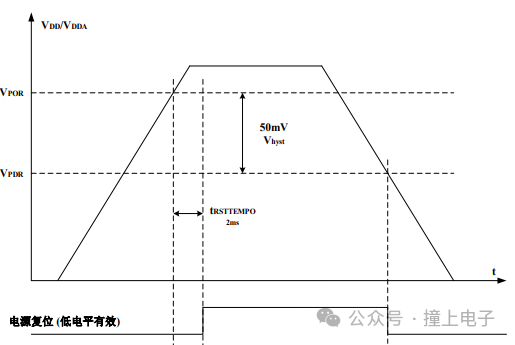

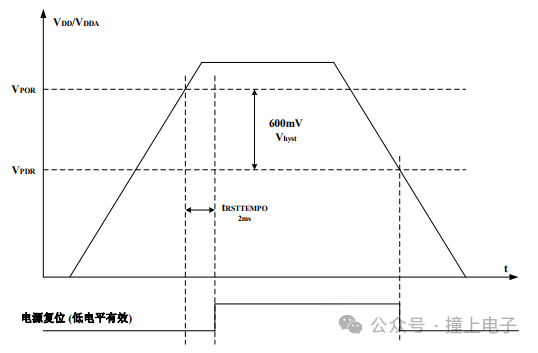

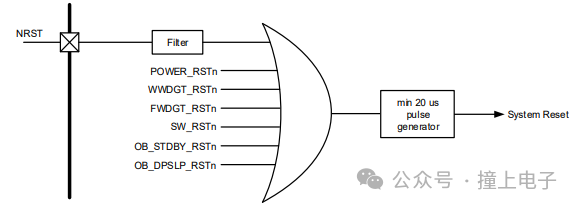

GD32F10x系列复位控制包括三种复位:电源复位、系统复位和备份域复位。电源复位为冷复位,电源启动时复位除了备份域的所有系统。电源和系统复位的过程中,NRST会维持一个低电平,直至复位结束。MCU无法执行起来时,可以通过示波器监测NRST管脚波形来判断芯片是否有一直发生复位事件。 芯片内部集成POR/ PDR(上电/掉电复位)电路,用于检测电源并在电压低于阈值时产生电源复位信号复位除备份域之外的整个芯片。GD32F1中flash容量不超过128KB的GD32F103产品,VPOR表示上电复位的阈值电压,典型值约为2.4V,VPDR表示掉电复位的阈值电压,典型值约为2.35V,迟滞电压Vhyst值约为50mV。flash容量大于128KB的GD32F103产品,VPOR表示上电复位的阈值电压,典型值约为2.4V,VPDR表示掉电复位的阈值电压,典型值约为1.8V,迟滞电压Vhyst值约为600mV。

注意:适用于GD32F101及flash容量不超过128KB的GD32F1产品。

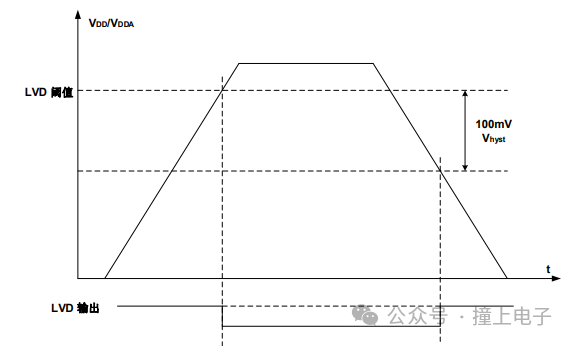

注意:适用于flash容量大于128KB的GD32F103产品。LVD的功能是检测VDD/VDDA供电电压是否低于低电压检测阈值(2.2 V~2.9V),该阈值由电源控制寄存器中的LVDT[2:0]位进行配置。LVD通过LVDEN置位使能,位于电源状态寄存器中的LVDF位表示低电压事件是否出现,该事件连接至EXTI的第16线,用户可以通过配置EXTI的第16线产生相应的中断。迟滞电压Vhyst值为100mV。LVD应用场合:当MCU电源受到外部干扰时,如发生电压跌落,我们可通过LVD设置低电压检测阈值,一旦跌落到该阈值,LVD中断被打开,可在中断函数里设置软复位等操作,避免MCU发生其他异常。

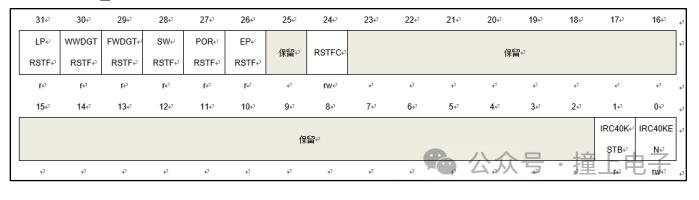

另外,MCU复位源可以通过查询寄存器RCU_RSTSCK来判断,该寄存器只有上电复位才能清除标志位,所以在使用过程中,获取到复位源后,可通过RSTFC控制位清除复位标志,那样发生看门狗复位或其他复位事件时,才能较准确在RCU_RSTSCK寄存器中体现出来:

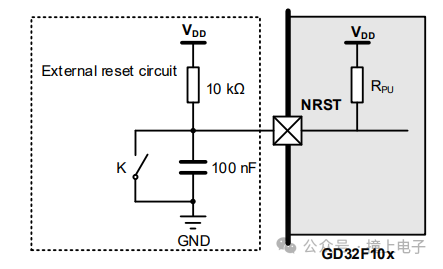

MCU内部集成有上电/掉电复位电路,在设计外部复位电路时,NRST管脚必须要放置一个电容,确保NRST管脚上电能产生一个至少20us的低脉冲延时,完成有效上电复位过程。

注意:1,内部上拉电阻RPU = 40kΩ,建议接外部上拉电阻10kΩ即可,以使得电压干扰不会导致芯片工作异常;2. 若考虑静电等影响,可在NRST管脚处放置ESD保护二极管;3. 尽管MCU内部有硬件POR电路,仍推荐外部加NRST复位阻容电路;4. 如果MCU启动异常,可适当增加NRST对地电容值,拉长MCU复位完成时间,避开上电异常时序区。

-

AN057 GD32F3x0系列硬件开发指南2023-02-23 175

-

AN056 GD32F4xx系列硬件开发指南2023-02-23 180

-

GD32W51x硬件开发指南2023-03-01 156

-

AN078 GD32E50x系列硬件开发指南2023-03-01 178

-

AN076 GD32F10x系列硬件开发指南2023-03-01 199

-

AN074 GD32E23x系列硬件开发指南2023-03-01 185

-

AN069 GD32L233系列硬件开发指南2023-03-01 177

-

AN053 GD32F30x和GD32F403硬件开发指南2022-10-19 171

-

AN061 GD32E103和GD32C103硬件开发指南2022-10-19 240

-

兆易创新AN056 GD32F4xx系列硬件开发指南2022-10-19 194

-

兆易创新AN057 GD32F3x0系列硬件开发指南2022-10-19 187

-

兆易创新AN069 GD32L233系列硬件开发指南2022-10-19 164

-

兆易创新AN074 GD32E23x系列硬件开发指南2022-10-19 169

-

兆易创新GD32W51x硬件开发指南2022-10-19 174

-

GD32L233硬件开发指南2024-01-05 100

全部0条评论

快来发表一下你的评论吧 !