AGM CPLD 应用指南

电子说

描述

AGM的部分料号跟Altera 硬件Pin to Pin兼容,映射关系表如下:

EPM240T100CxN—>AG256SL100(CPLD)

EPM240T100IxN---->AG256SL100(CPLD)

EPM570T100CxN—>AG576SL100(CPLD)

EPM570T100IxN---->AG576SL100(CPLD)

EPM570T144CxN—>AG576SL144(CPLD)

EPM570T144IxN---->AG576SL144(CPLD)

EP3C5E144—>AG6KL144

EP4CE6E22—>AG6KL144

EP3C5F256—>AG6KF256

EP4CE6F17—>AG6KF256

EP3C10E144—>AG10KL144

EP4CE10E22—>AG10KL144

EP3C10F256—>AG10KF256

EP4CE10F17—>AG10KF256

EP3C16F256—>AG16KF256

EP4CE15F17—>AG16KF256

Also for Lattice chip

ICE40LP1K-CM36, AGM also have Pin to Pin part " AG1KLPBGA36".

针对几颗用量广泛的CPLD料号,如AG256以及AG576系列,移植方法如下:

软件流程选择

Supra 共有 3 种开发 Mode:Native 选项(AGM 自有 EDA 综合工具),Synplicity 选项(第三方综合工具,例如 Synplify,Mentor 等),Compatible 选项(兼容 Altera Quartus II 的综合工具)。

文档中的 Supra 主要基于 Quartus II 综合的设计流程,其它工具设计流程类似。

AG576 IO

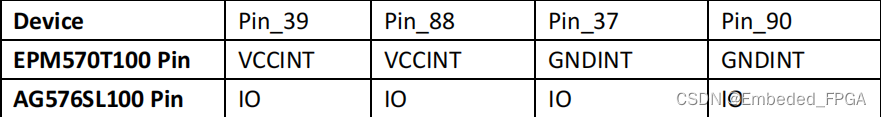

AG576SL100 的可用 IO 与 AG256SL100 一致,比 Altera EPM570T100 多 4 个 IO,分别为:

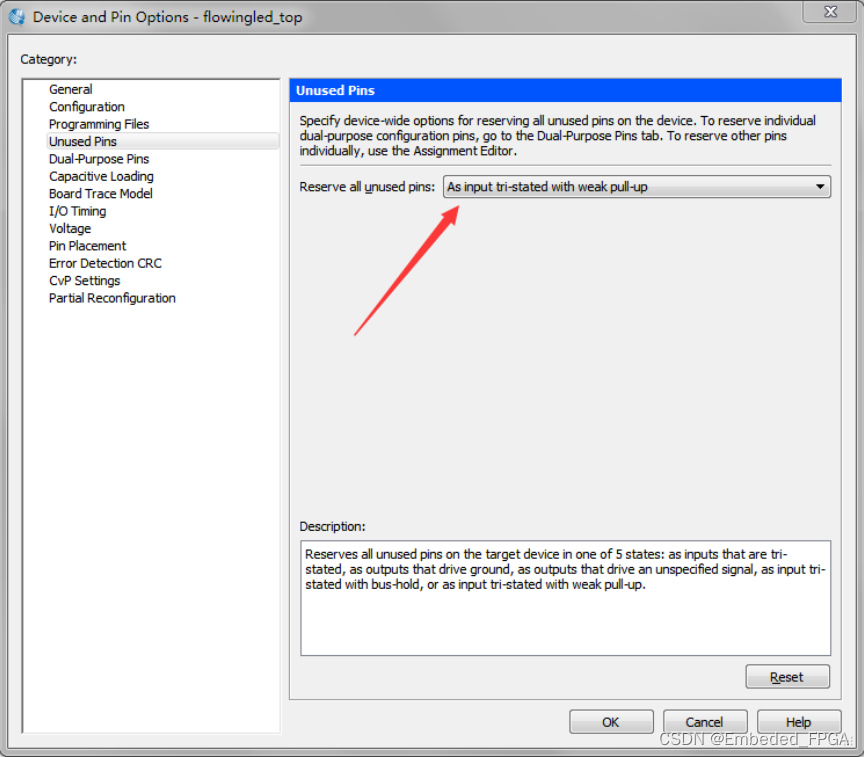

如果 PCB 兼容 EPM570,39/88 接 3.3V 供电的话,有可能会使芯片输入 IO 电流较大。可以通过设置,使 AG576 的未用 IO 为三态模式。请在 EPM570 的原设计中设置 Unused Pin 选项为

AS input tri-stated with weak pull-up。如下图:

如果希望利用 AG576 多的 4 个 IO,可以在 asf 文件中加入对这 4 个 pin 的分配,如:

set_location_assignment PIN_88 -to abc

安全位设置

AG256/576 安全位(SECURITY_BIT)可以使 CPLD 烧写好后,无法读取出内部程序,只能擦除或覆盖,从而实现用户设计的安全性。

设置方法:

方法一:Quartus MAX II 工程中,选 Assignment-Device 菜单,点 Device and Pin Options,选 General 类别,选中 Enables security bit support。重新编译。运行 Supra 转换流程。

方法二:在 Supra 生成的 asf 文件中,加入一行:

set_global_assignment -name SECURITY_BIT “ON”

PLL 的使用

AG576 内部带有 1 个 PLL,可通过以下方法调用:

在 Supra 中进入 Tools -> Create IP,选择 PLL 或 Memory。

PLL 类型选择 PLL,填写输入频率(MHz),输出频率,相移等数据。

注意:PLL 的输入时钟应是芯片的全局输入时钟 IO 管脚。

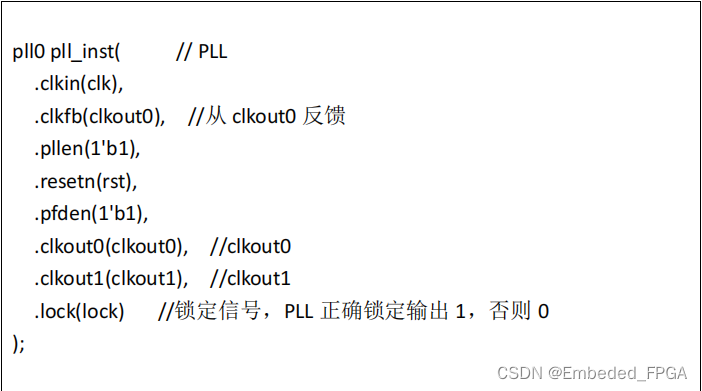

完成后点击 Generate,目录中会产生比如 pll0.v、pll0.ip 两个文件。在 Quartus II 设计代码中即可调用产生的模块(.v)。

新生成的 Quartus II 工程中编辑源文件(如.v)加入 pll 模块(这样,原 MAX II 工程就不能正确编译了,请留好备份)

Verilog 文件方式:

在 Supra Migrate 时需要将产生好的 IP 加入 IP Files(.ip)。

如果在设计过程中添加或修改 IP 文件,Supra project 需要重新再新建一次并覆盖原工程,并执行 Migrate 一次,和运行 af_quartus.tcl。

应用 AGM IP 的 Quartus II 工程中需要注意并确认下面信息,正确执行 Tcl 后会出现:

由于 IP 声明包含在 alta_sim.v 的库文件中,这个文件默认在 supra 的安装目录中,如:

C:Supraetcarchrodinia,Quartus II project 应包含这个文件。

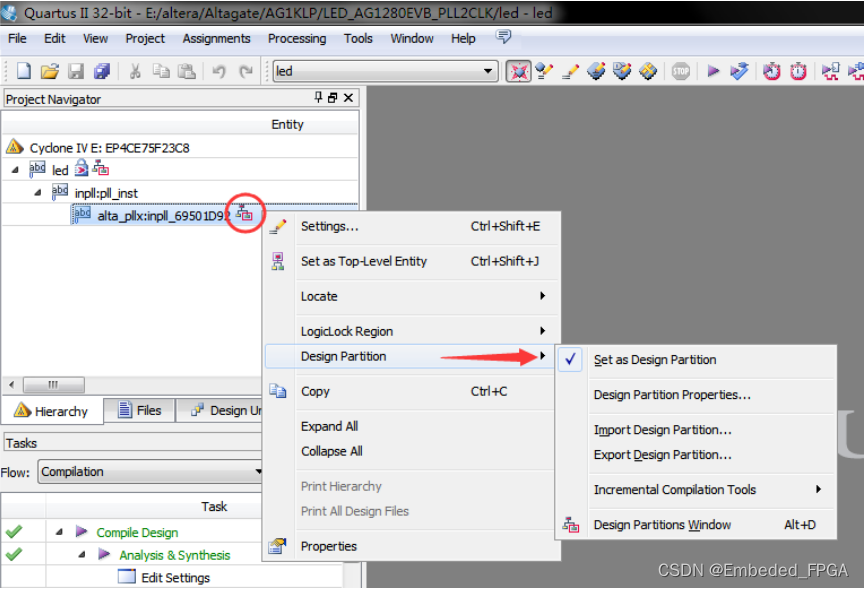

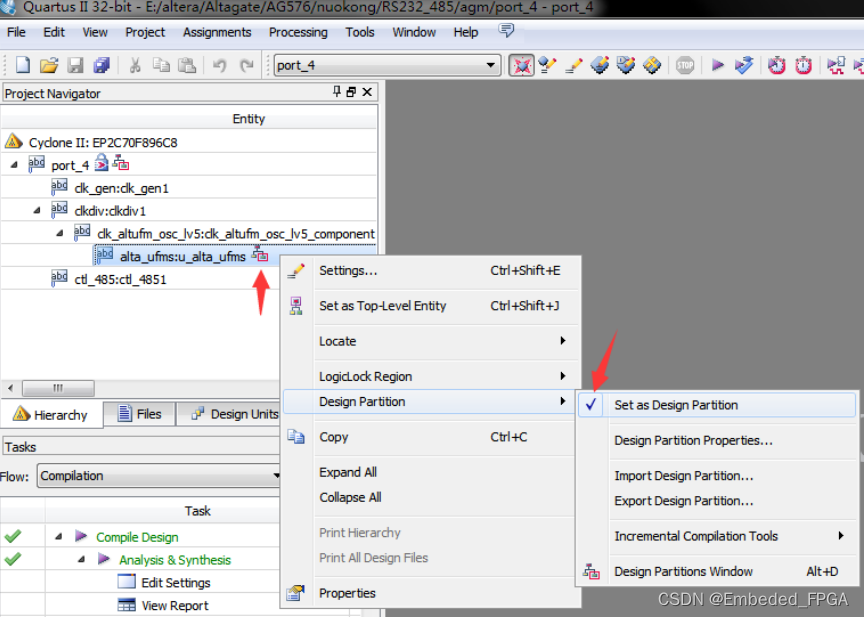

同时,alta_pll 应设为 Design Partition,如图:

注意:

如果 Supra 编译出错,有可能是新加入 PLL 使得 clk 时钟线布线不成功,说明 576 的全局时钟不够,可修改新项目中的下面设置:

Settings->Fitter Settings,More Settings, Maximum number of global clocks allowed,改为 2或 3(一共是 4,PLL 用 2 个或 1 个时钟)。

UFM 的使用

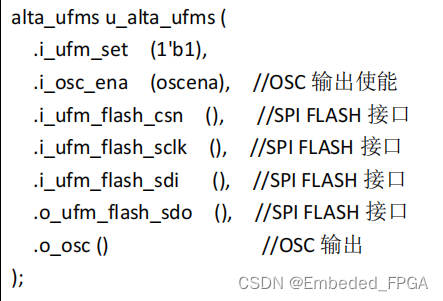

需要调用 alta_ufms 模块:

使用 USER FLASH,需要通过 SPI 口控制输入输出。

同时提供内部晶振 OSC,可输出 4MHz 左右时钟,用于精度不高的时钟设计。

在设计中加入后,转换好的项目中,alta_ufms 需要在 Quartus II 中设为 Design Partition,如下图,然后进行正常编译。

总的来说,硬件无需过多调试;

软件按上述流程移植,绝大部分情况下均能成功。

审核编辑 黄宇

-

AGM Micro推出STM32兼容MCU产品系列2023-12-29 0

-

AGM Micro发布兼容STM32的MCU产品系列2023-12-29 0

-

国产FPGA傲格芯AGM,分享大家的AGM FPGA的技术资料2020-09-01 0

-

学习 AGM 与FPGA快速入门2020-09-03 0

-

AGM FPGA快速入门2021-06-01 0

-

AGM FPGA 快速入门手册2021-07-26 0

-

教你怎样去选择AGM FPGA呢2021-12-09 0

-

CPLD FPGA高级应用开发指南2010-04-15 388

-

什么是AGM电池?2009-11-06 4178

-

Xilinx-ISE9.x-FPGA-CPLD设计指南合集2022-03-22 553

-

Xilinx的CPLD IO用户指南2019-02-14 777

-

AGM CPLD数据手册2022-03-21 764

-

Compact系列CPLD配置(configuration)用户指南2022-09-26 386

-

Compact系列CPLD嵌入式硬核用户指南2022-09-26 326

-

Xilinx CPLD在线编程参考指南2022-10-14 311

全部0条评论

快来发表一下你的评论吧 !