VLSI设计验证及其方法的重要性

电子说

描述

VLSI设计验证及其方法的重要性

在 VLSI(超大规模集成)的动态世界中,对创新产品的需求比以往任何时候都更高。从概念到功能齐全的产品的过程涉及许多挑战和不确定性,其中设计验证通过确认设计满足其预期要求和规格,在确保复杂电子系统的功能和可靠性方面发挥着关键作用。据 Research and Markets 称,到 2023 年,全球 VLSI 市场预计价值 6622 亿美元。据市场分析师预测,到 2028 年,其价值将达到 9717.1 亿美元,复合年增长率 (CAGR) 为 8%。

在本文中,我们将探讨设计验证的概念、其重要性、涉及的过程、使用的语言和方法,以及超大规模集成电路设计发展中这一关键阶段的未来前景。

什么是设计验证及其重要性?

设计验证是一个系统化的过程,用于验证和确认设计满足其指定的要求并遵守设计指南。这是产品开发周期中至关重要的一步,旨在及早发现并纠正设计问题,以避免在开发后期阶段进行成本高昂且耗时的返工。设计验证可确保最终产品,无论是集成电路 (IC)、片上系统 (SoC) 还是任何电子系统,都能正确可靠地运行。 SoC 和 ASIC 验证在实现可靠和高性能集成电路方面发挥着关键作用。

VLSI设计验证涉及两种类型的验证:

功能验证

静态时序分析

这些验证步骤至关重要,需要在设计的各个阶段进行时执行,以确保最终产品满足预期要求并保持高质量。

功能验证:

它是 VLSI 设计的关键阶段,旨在确保在各种操作条件下使用的芯片的正确功能。它涉及测试设计以验证其行为是否符合预期规格和功能要求。这个验证阶段至关重要,因为超大规模集成电路设计变得越来越复杂,在开发过程中必然会出现人为错误或设计缺陷。 VLSI设计中的功能验证过程如下。

识别和准备:在此阶段,确定设计要求并准备验证计划。该计划概述了后续验证步骤的目的、目标和策略。

规划:验证计划准备好后,规划阶段涉及资源分配、设置测试环境以及创建测试用例和测试平台。

开发:开发阶段的重点是使用适当的语言和方法对测试平台和测试用例进行编码。此阶段还包括构建和集成模拟和仿真环境,以促进彻底的测试。

执行:在执行阶段,测试用例在设计上运行以验证其功能和性能。这通常涉及广泛的模拟和仿真器以涵盖所有可能的场景。

报告:最后,验证过程以生成详细报告结束,包括错误报告、覆盖率统计数据和总体验证状态。这些报告有助于确定需要改进的领域,并为未来的设计迭代提供有价值的见解。

静态时序分析(STA):

静态时序分析是 VLSI 设计中的另一个关键步骤,重点是验证设计的时序要求。在 VLSI 设计中,时序至关重要,因为它决定信号如何在芯片中传播并影响集成电路的整体性能和功能。该过程用于确定设计中最坏情况和最佳情况的信号传播延迟。它分析从源(输入)到目的地(输出)的时序路径,并确保信号在所需的时钟周期内到达预期目的地,而不违反任何时序约束。在 STA 期间,设计被划分为时间路径,以便可以执行时序分析。每个时间路径由以下因素组成。

起始点:时序路由的起始点是数据由时钟边沿启动或需要在特定时间准备就绪的位置。每个起始点必须有一个寄存器时钟引脚或输入端口。

组合逻辑网络:它包含没有内部存储器的部分。组合逻辑可以使用 AND、OR、XOR 和反相器元件,但不能使用触发器、锁存器、寄存器或 RAM。

端点:这是当时钟边沿捕获数据或必须在特定时间提供数据时时序路径结束的位置。每个端点必须有一个输出端口或一个用于寄存器数据输入的引脚。

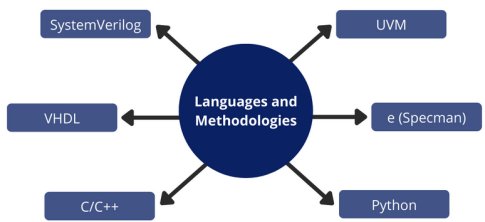

设计验证中使用的语言和方法

设计验证采用各种语言和方法来有效测试和验证 VLSI 设计。

SystemVerilog (SV) 验证:SV 提供了一组广泛的验证功能,包括面向对象编程、约束随机测试和功能覆盖。

通用验证方法 (UVM): UVM 是一种基于 SystemVerilog 构建的标准化方法,可实现可扩展和可重用的验证环境,从而提高设计验证的效率和灵活性。

VHDL(VHSIC硬件描述语言):VHDL广泛用于超大规模集成电路行业的设计输入和验证,为硬件建模、仿真和综合提供强有力的支持。

e(Specman) :e是Yoav Hollander为其Specman软件开发的验证语言,提供强大的验证功能,例如约束驱动的随机测试和事务级建模。后来更名为 Verisity,并被 Cadence Design Systems 收购。

C/C++ 和 Python:这些编程语言通常用于构建验证框架、测试平台和基于脚本的验证流程。

VLSI设计验证和方法

设计验证的优点

有效的设计验证为超大规模集成电路行业提供了众多优势。

它缩短了 VLSI 产品的上市时间

该过程确保符合设计规范

它增强了设计对不确定性的适应能力

验证可最大限度地降低与设计失败相关的风险

设计验证的未来

设计验证的未来看起来充满希望。人工智能和机器学习辅助验证的新方法正在出现,以有效解决验证挑战。采用先进的验证工具和方法将对提高验证过程的效率、有效性和覆盖范围发挥重要作用。此外,随着SoC、ASIC和低功耗设计的发展,对专业VLSI验证的需求将持续上升。

设计验证是产品开发过程中不可或缺的一部分,可确保可靠性、功能和性能。设计验证采用各种语言、方法和技术来解决复杂设计和新兴技术带来的挑战。随着技术格局的发展,设计验证将继续在提供创新且可靠的产品以满足不断变化的世界的需求方面发挥至关重要的作用。

审核编辑 黄宇

-

#硬声创作季 #VLSI VLSI设计基础-06.13 Memory的重要性及其分类-1水管工 2022-09-28

-

#硬声创作季 #VLSI VLSI设计基础-06.13 Memory的重要性及其分类-2水管工 2022-09-28

-

BGA焊接温度控制重要性2020-03-26 0

-

Syncer模块的重要性是什么?2020-05-18 0

-

代码规范的重要性是什么2020-05-19 0

-

使用ODDR原语的重要性是什么?2020-06-17 0

-

欠压保护的重要性2021-03-03 0

-

什么是网络拓扑,它的重要性是什么?2021-03-17 0

-

时钟系统的重要性2021-08-20 0

-

论调节阀的重要性2021-09-15 0

-

ATPG是什么?ATPG有何重要性2021-11-02 0

-

时钟服务器的重要性是什么?2021-11-08 0

-

UPS的重要性2021-11-16 0

-

arm汇编的重要性是什么?2021-11-30 0

-

POE浪涌保护的重要性是什么?2022-01-14 0

全部0条评论

快来发表一下你的评论吧 !