ESD器件的工作原理?CMOS I/O上的内部ESD保护实现

描述

ESD器件的工作原理

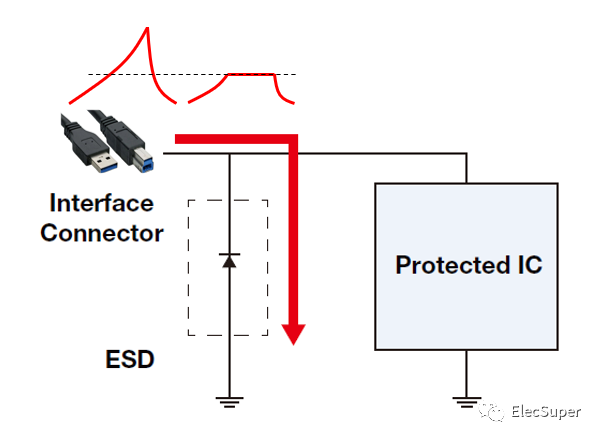

静电保护器件(ESD) 是由一个或多个 TVS 晶粒采用不同的电路拓扑制成具有特定功能的多路或单路 ESD 保护器件。ESD反向并联于电路中,当电路正常工作时,ESD处于截止状态(高阻态),不影响电路正常工作。

当电路出现异常过电压并达到 ESD 的击穿电压时,ESD迅速由高阻态变为低阻态,泄放由异常过电压导致的瞬时过电流到地,同时把异常过电压钳制在一个安全水平之内,从而保护后级电路免遭异常过电压的损坏。

图 ESD保护原理

ESD的电路符号和极性

ESD的电路符号和TVS可以画成一样的,因为用的最多的ESD都是硅材质的,电路符号如下:

单向TVS

双向TVS

ESD器件的参数说明

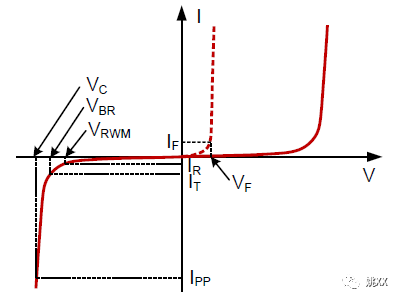

*VRWM(Reverse stand-off voltage):反向截止电压

即允许施加的最大工作电压,在该电压下ESD 处于截止状态,ESD 的漏电流很小,为几微安甚至更低。

*VBR(Reverse breakdown voltage):反向击穿电压

ESD 要开始动作(雪崩击穿)的电压,一般在规定的电流下测量,通常在大小为1mA 的电流下测量。

*IR(Reverse leakage current):反向漏电流

即在ESD 器件两端施加VRWM 电压下测得ESD 的漏电流。

*IPP(Peak pulse current):峰值脉冲电流

ESD 产品一般采用8/20μs 的波形测量。

*VC(Clamping voltage):钳位电压

在给定大小的IPP 下测得ESD 两端的电压。大部分ESD 产品VC 与VBR 及IPP 成正比关系,电流越大,钳位电压也越高。

*C j(Off state junction capacitance):结电容

结电容与芯片面积、工作电压有关系。相同电压下,芯片面积越大结电容越大。相同芯片面积下,工作电压越高结电容越低。

CMOS I/O上的内部ESD保护

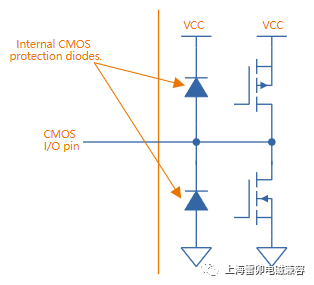

内置保护在CMOS I/O引脚上非常常见,这些引脚可能是器件的一部分(从简单的负载开关到中等复杂性的微控制器,再到高复杂性的FPGA)。它们通常为每个 I/O 引脚两个。一个连接在引脚和GND之间,一个连接在引脚和VCC之间。两者在正常工作条件下均为反向偏置(GND<=VI/O<=VCC)。

CMOS数字I/O引脚示意图,突出显示了许多设计中普遍存在的内部保护二极管(即使IC数据手册中没有提到它们)。

它们用于在引脚发生故障时保护敏感的CMOS逻辑。如果VI/O 上的电压高于 VCC(例如,正 ESD 电压尖峰),则顶部二极管导通,将引脚上的电压箝位至不超过VCC+Vf。同样,如果VI/O上的电压降至VGND以下(例如,负ESD电压尖峰),则底部二极管导通,将引脚上的电压箝位至不超过−Vf。

要小心,因为这些二极管通常具有相当低的最大电流。超过此最大电流将吹动ESD二极管,通常导致其开路,从而消除了敏感CMOS电路的保护,然后几乎瞬间被油炸。然后,您的 I/O 引脚将停止工作。如果幸运的话,它只会是一个受影响的引脚。如果没有,整个端口(如果适用),甚至整个设备都会被失效。

无论它们多么有用,它们也会在特定情况下产生设计挑战,因此在进行任何涉及CMOS I/O且存在ESD保护二极管的原理图设计时,都需要仔细考虑。导致问题的两种情况是:为具有多个电压轨的电路上电时。当VI/O上的电压在某些点上可能高于VCC时,由于输入信号的性质。在低功耗设计中,当您有选择地关断为这些IC供电的电压轨时。

常见ESD封装

ESD根据保护信号线的路数,又可以分为:单路保护ESD、两路保护ESD、四路保护ESD等,所以ESD的封装形式也有各种类型。

ESD器件选型考虑事项与步骤

考虑事项:

底层逻辑:在不影响要保护的电路平时正常工作的情况下,还能在异常的过压经过的时候,把电压降下来,达到保护后面的电路或者芯片的目的,同时保护器件本身还不能被打坏。

步骤:

1.计算接口信号幅值的范围来确定ESD器件的工作电压;

2.根据信号类型决定使用单向或者双向ESD器件;

3.根据信号速率决定该接口能承受的最大寄生电容;

4.根据电路系统的最大承受电压冲击,选择适合的钳位电压;

5.确保ESD器件可达到或超过IEC 61000-4-2 level4。

-

ESD保护基础知识#电子元器件 #ESD #保护器件 #技术分享 #电子产品学习电子知识 2023-05-07

-

新ESD技术减小芯片的I/O尺寸2012-12-11 0

-

ESD设计与综合2013-09-04 0

-

USB2.0数据接口ESD保护2013-12-27 0

-

ESD的工作原理是什么?ESD的特性参数有哪些?2014-03-18 0

-

浅析ESD 防护与ESD 防护器件2017-07-31 0

-

电子器件的ESD静电保护2018-01-16 0

-

ESD(静电放电)介绍及ESD保护电路的设计2018-10-11 0

-

板级ESD保护器件的关键属性2019-05-22 0

-

I/O接口ESD静电防护方案图2020-09-24 0

-

I/O接口ESD静电防护解决方案2020-10-29 0

-

在I/O电路中ESD保护结构的设计要求2021-04-02 0

-

静电放电(ESD)保护器件种类与特点2022-07-12 0

-

CMOS工艺中GG2NMOS结构ESD保护电路设计2009-11-20 593

-

常用的ESD保护器件及原理2023-12-07 837

全部0条评论

快来发表一下你的评论吧 !