通用阵列逻辑(GAL)电路结构设计分析

可编程逻辑

描述

通用阵列逻辑(GAL)是一种可编程逻辑器件,由Lattice公司在PAL(可编程阵列逻辑)的基础上设计出来。GAL采用可编程的输出逻辑宏单元OLMC(Output Logic Macro Cell)结构,使得电路的逻辑设计更加灵活。

GAL的优点包括:

具有电可擦除的功能,克服了熔丝型可编程器件的一次可编程问题,其可改写的次数超过100次。

由于采用了输出宏单元结构,用户可根据需要进行组态,一片GAL器件可以实现各种组态的PAL器件输出结构的逻辑功能,给电路设计带来极大的方便。

具有加密的功能,保护了知识产权。

在器件中开设了一个存储区域用来存放识别标志——即电子标签的功能。

GAL器件的发展方向是高密度、大容量、高速和低功耗。此外,人们还在研究下一代可编程逻辑器件,如CPLD(复杂可编程逻辑器件)和FPGA(现场可编程门阵列)等。这些器件在应用上与GAL有重叠,但它们具有更高的集成度和更丰富的功能,可以应用于更广泛的领域。

在架构方面,GAL类似于PAL,但区别在于可编程结构。PAL使用可一次性编程的PROM,而GAL使用可重新编程的EEPROM.

GAL的电路结构

现以常见的GAL16V8为例,介绍GAL器件的一般结构形式和工作原理。

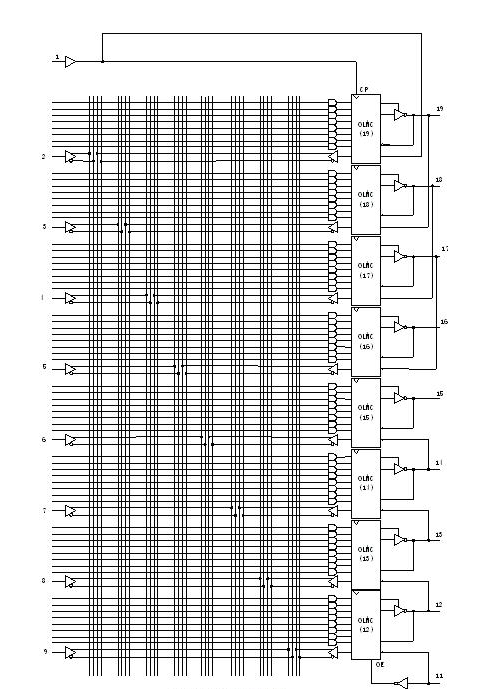

图是GAL16V8的电路结构图。它有一个32*64位的可编程与逻辑阵列,8个OLMC,10个输入缓冲器,8个三态输出缓冲器和8个反馈/输入缓冲器。

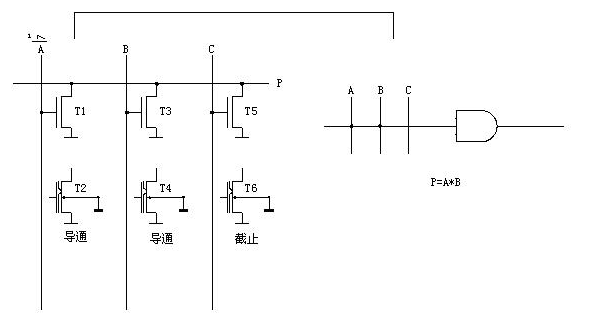

与逻辑阵列的每个交叉点上设有 编程电源。假定编程后T2、T4的浮置栅上没有带负电荷,而T6的浮置栅上存储了足够的负电荷,则T2、T4导通而T6截止。因此,A、B和P之间是编程连接,而C和P之间没有连接,于是得到P=A*B。

组成或逻辑阵列的8个或门分别包含于8个0LMC中,它们和与逻辑阵列的连接是固定的。

在GAL16V8中除了与逻辑阵列以外还有一些编程单元。编程单元的地址分误和功能划分情况如图所示。因为这并不是编程单元实际的空间布局图,所以又把图叫做地址映射图。

GAL的应用场景有哪些呢

GAL的应用场景主要包括以下几个方面:

数字逻辑设计:GAL可以用于实现各种数字逻辑功能,如计数器、寄存器、加法器等。由于其具有灵活的编程能力,可以方便地实现各种组合逻辑和时序逻辑电路。

可编程控制器:GAL可以用于实现可编程控制器的逻辑控制功能,如顺序控制、过程控制等。通过编程,可以实现各种复杂的控制算法和逻辑控制。

数字信号处理:GAL可以用于实现数字信号处理算法,如滤波器、频谱分析等。通过编程,可以实现各种数字信号处理功能,提高信号的精度和稳定性。

通信系统:GAL可以用于实现通信系统的逻辑控制功能,如调制解调器、加密解密器等。通过编程,可以实现各种通信协议和控制算法。

嵌入式系统:GAL可以用于实现嵌入式系统的逻辑控制功能,如微控制器、嵌入式处理器等。通过编程,可以实现各种嵌入式系统的功能和控制算法。

总的来说,GAL的应用场景非常广泛,可以在各种数字系统中实现灵活的逻辑控制和数字处理功能。

审核编辑:黄飞

-

可编程通用阵列逻辑GAL器件介绍pdf2009-09-29 0

-

操作系统结构设计2011-09-13 0

-

手机结构设计心得2012-11-07 0

-

招聘--结构设计师2015-09-25 0

-

浅谈产品结构设计特点2016-02-25 0

-

软件结构设计2016-09-26 0

-

通用阵列逻辑GAL实现基本门电路的设计2009-06-28 1890

-

轴系结构设计实验2009-03-13 56422

-

通用阵列逻辑GAL简介2012-10-12 5638

-

通用阵列逻辑GAL器件优缺点分析2012-10-12 4210

-

半替代护环的结构设计2017-01-07 682

-

惯性闭锁开关的结构设计与分析_许马会2017-03-19 652

-

GAL的基本结构_GAL的逻辑结构2019-10-11 16102

-

O型圈密封结构设计2022-02-10 884

-

PCB叠层结构设计详解2022-09-30 1972

全部0条评论

快来发表一下你的评论吧 !