减法器电路与原理 减法器电路图分享

描述

减法器电路与原理

减法器是一种电路,它可以实现二进制数字的减法运算。减法器的工作原理基于位运算和进位/借位机制。

常见的减法器有硬件实现的二进制减法器和软件实现的程序减法器。硬件实现的减法器通常是由一组异或门(XOR)、与门(AND)和或门(OR)组成,而软件实现的减法器则可以在计算机程序中实现。

在二进制减法中,如果第二个操作数是被减数,则第一个操作数是减数。减数和被减数的每一位分别被进行异或运算,然后再进行与运算,以确定是否需要进位/借位。通过这种方式,减法器可以实现二进制数的减法运算。

减法器是一种用于实现二进制数减法运算的电路,它通过使用异或门、与门和或门来实现二进制减法运算的进位/借位机制。

减法器电路图分享

通用减法器电路

图(a)电路输入输出关系为:V0=Vi2-Vi1图中放大器的输出信号电压极性通常与输入电压极性相同。如果要求反相输出,则采用图(b)所示电路。其输入输出关系为:Vo=Vi1-Vi2。

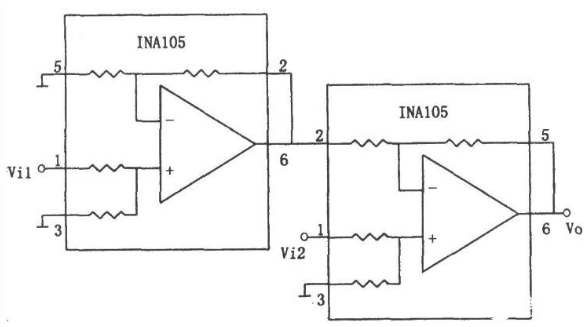

INA105构成的减法电路

如图所示为其他器件组成的减法电路(2)。该电路输入输出关系为:Vo=Vi2-Vi1。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

菜鸟请教一个运放减法器的问题2012-06-27 0

-

减法器设计异常2017-02-14 0

-

8位减法器求解?2013-10-08 0

-

减法器的4个电阻到底是什么关系呢?2017-02-25 0

-

哪一个是减法器?负反馈在减法器电路中的原理?2017-08-31 0

-

为什么LM358做的减法器输出不对?2019-07-15 0

-

二位BCD码减法器2019-09-18 0

-

如何用最简单的方法设计一个减法器?2020-04-27 0

-

本的二进制加法/减法器,本的二进制加法/减法器原理2010-04-13 5153

-

减法器电路2010-04-24 9574

-

8位加法器和减法器设计实习报告2013-09-04 2434

-

减法器电路设计方案汇总(五款模拟电路设计原理图详解)2018-01-17 87768

-

数字电路中加法器和减法器逻辑图分析2020-09-01 20932

-

基于OP07的减法器设计2023-05-15 310

-

如何设计一个16比特的减法器呢?2024-02-19 356

全部0条评论

快来发表一下你的评论吧 !