如何设计一个16比特的减法器呢?

描述

减法电路是基本集成运放电路的一种,算术运算电路主要包括数字加法器电路、数字减法器电路、数字乘法器电路和数字除法器电路。

由于基本的算术运算加法、减法、乘法、除法最终都可归结为加法或减法运算,因此,在算术运算电路中数字加法器电路与数字减法器电路是最基础的电路。一般是由集成运放外加反馈网络所构成的运算电路来实现。

Verilog设计

设计一个16比特的减法器

(1)基于全减器设计“行波借位减法器”,基础的全减器模块

行波借位减法器

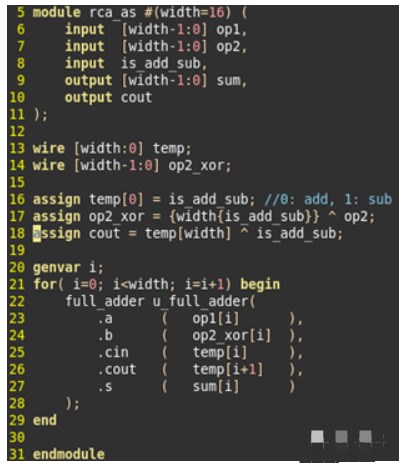

(2)根据行波进位加法器,通过控制信号,使其同时具有加法和减法的功能,注意进位。

加减法器

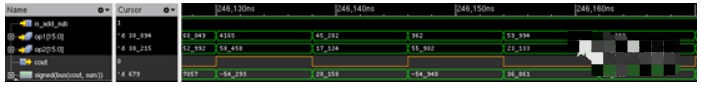

测试波形

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

菜鸟请教一个运放减法器的问题2012-06-27 0

-

减法器连接正确,为什么会不在线性区工作呢?2015-04-16 0

-

8位减法器求解?2013-10-08 0

-

减法器设计异常2017-02-14 0

-

减法器的4个电阻到底是什么关系呢?2017-02-25 0

-

哪一个是减法器?负反馈在减法器电路中的原理?2017-08-31 0

-

设计一个基于RS触发器余3码十进制减法器2017-11-28 0

-

二位BCD码减法器2019-09-18 0

-

如何用最简单的方法设计一个减法器?2020-04-27 0

-

本的二进制加法/减法器,本的二进制加法/减法器原理2010-04-13 5153

-

减法器电路2010-04-24 9574

-

8位加法器和减法器设计实习报告2013-09-04 2434

-

数字电路中加法器和减法器逻辑图分析2020-09-01 20931

-

基于OP07的减法器设计2023-05-15 310

-

减法器电路与原理 减法器电路图分享2024-02-19 1795

全部0条评论

快来发表一下你的评论吧 !