7.5 μm像元间距红外探测器三维电极的制备与应用案例

描述

随着各类小型化自动武器装备在战场上被高频使用,并获得了大量战果,此类装备的国防需求不断增长。同时红外探测器制造技术不断提高,低成本、小型化、低功耗(SWaP)已经成为第三代碲镉汞红外探测器的重要发展方向。目前国外部分产品已经进入市场,并逐渐成为主流SWaP产品。

据麦姆斯咨询报道,近期,华北光电技术研究所与中国电子科技集团公司第四十五研究所组成的科研团队在《红外》期刊上发表了以“7.5 μm像元间距红外探测器三维电极的制备与应用”为主题的文章。该文章第一作者和通讯作者为王格清助理工程师,主要从事红外探测器器件技术研究。

本工作采用现有读出电路电极生长设备和直写式光刻设备开发了三维电极的制备工艺。在制备过程中,首先在读出电路表面制备三维电极,在碲镉汞芯片端生长铟饼,然后通过倒装互连工艺可以实现7.5 μm像元间距的1 k×1 k碲镉汞芯片与读出电路的互连。可变参数包括金属生长角度、生长速率、生长厚度以及金属种类等。

技术难点

在探测器的研制过程中,由于碲镉汞光敏芯片表面起伏较大,倒装互连设备在调平过程中不可避免地存在一定的微小误差。另外,由于像元间距较小,设备对准误差的负面影响也无法被忽略。这些因素大幅提升了7.5 μm像元间距探测器的倒装互连工艺对铟凸点技术参数的要求。为了保证探测器倒装互连工艺的成品率,需要在7.5 μm像元间距读出电路的位点上制备出具有较大高度且高度均匀性好的铟凸点。这对读出电路铟凸点制备工艺提出了巨大的挑战。

受下列因素的制约,铟凸点阵列的高度及其均匀性很难提升:首先,为了将无用的金属铟完全剥离,需要光刻胶的厚度大于所生长的金属层厚度的2倍。其次,铟凸点在倒装互连过程中会因发生形变而宽度增加。为了避免相邻铟凸点发生连接,需要保证铟凸点间留有足够的间隙。然而,探测器的像元间距只有7.5 μm,因此可用于制备铟凸点的空间极为狭小。在上述条件的限制下,7.5 μm像元间距光刻图形的尺寸和光刻胶的厚度之间产生了不可调和的矛盾。

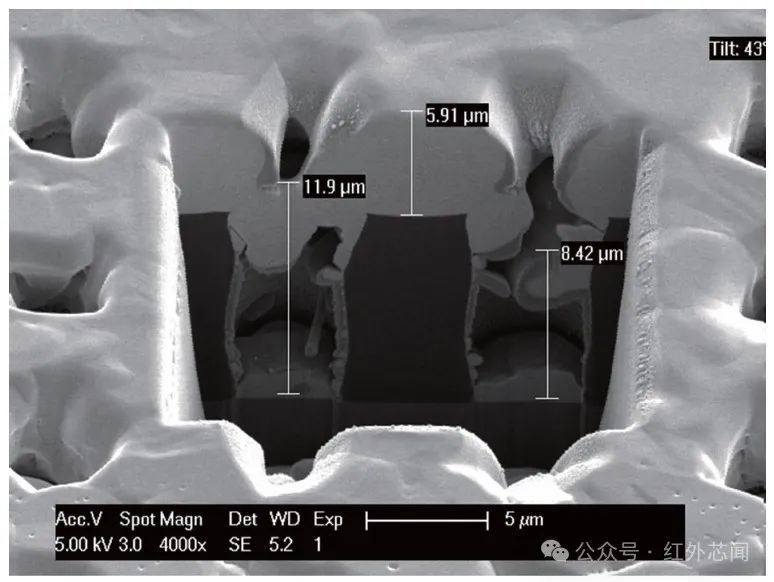

在10 μm像元间距条件下,虽然可以通过光刻制备出尺寸更大的铟凸点生长结构,但在金属铟生长过程中还是会发生少量生长结构堵塞现象,导致此处制备的铟凸点高度无法达到设计值,并且与周围铟凸点高度差异很大(见图1)。当像元间距降低至7.5 μm时,可制备的铟凸点生长结构尺寸更小,更易发生生长结构堵塞现象。因此制备出的铟凸点高度和高度均匀性均无法满足倒装互连工艺的要求。带有此类铟凸点的读出电路与碲镉汞芯片倒装互连后,会产生大量盲元,导致制备出的探测器性能无法满足应用需求。

图1 劣质铟凸点的扫描电镜图

为了增加铟凸点高度的均匀性,可以在铟凸点下制备直径小于铟凸点的圆形凸点下金属层(UBM),然后采用“起球工艺”将铟凸点回融成铟球,从而降低铟凸点高度差异。但是读出电路的像元接触孔多为2 μm×2 μm的方孔,其对角线长度为2.82 μm,几乎与UBM直径相同。因此留给光刻工艺的套刻误差余量极为有限,同时还需要保证UBM的一致性。当UBM不能完全覆盖电路像元接触孔时,探测器的性能稳定和长期可靠性会受到影响。UBM直径的差异会降低铟凸点的高度均匀性。过小的UBM会使铟凸点回融成球后不易粘附在读出电路表面,容易脱落,形成盲元。综上所述,7.5 μm像元间距的UBM制备工艺也存在诸多难点。

在满足上述条件后,铟凸点倒装互连的技术路线还要求倒装互连工艺全过程保持很高的调平、对准精度,否则微小的设备误差即会导致互连失败。其原因在于:当电路铟凸点高度不够时,一旦碲镉汞芯片平坦度稍差或者互连设备的误差使碲镉汞芯片与读出电路之间存在微小的角度,就会导致倒装互连失败,芯片出现大面积区域性盲元。而且铟凸点高度差异大,使得绝大部分像元与铟凸点完成连接后仍有部分像元由于铟凸点高度不足没有实现连通,导致盲元数量大幅增加。因此,如何在7.5 μm像元间距的读出电路上制备出高度合适且均匀性好的铟凸点,是 7.5 μm像元间距碲镉汞红外探测器研制的重要技术难题。此项技术的突破,可以大幅提升小间距碲镉汞红外探测器倒装互连工艺的成品率,进而提高探测器的整体良率。

三维电极的制备与应用

由于铟凸点技术路线存在诸多难点,很难实现读出电路与碲镉汞芯片互连。为了降低7.5 μm像元间距探测器的倒装互连工艺难度,提升探测器的良品率,需要开发三维电极互连技术路线。此技术路线如下:首先在7.5 μm像元间距的读出电路上制备三维电极,然后在碲镉汞芯片上制备小高宽比的铟饼,最后通过倒装互连工艺完成读出电路与碲镉汞芯片的互连导通。综合考虑制备工艺的难度和工艺稳定性,三维电极的设计高度可以达到4 μm,且直径为 2.5 μm~3.5 μm;铟饼的设计厚度为2.5 μm,尺寸为5 μm×5 μm。理论上,三维电极和铟饼的总高度可达6.5 μm左右。此高度足以弥补碲镉汞芯片表面起伏和互连设备的误差,完全满足7.5 μm像元间距探测器的倒装互连工艺需求。在倒装互连工艺过程中,三维电极不会因压力而发生膨胀。而且由于三维电极的侧壁厚度很小,其与铟饼互连时会插入铟饼,因此连通后不会使铟饼宽度增加,从而降低了工艺对互连设备调平、对准精度的要求。

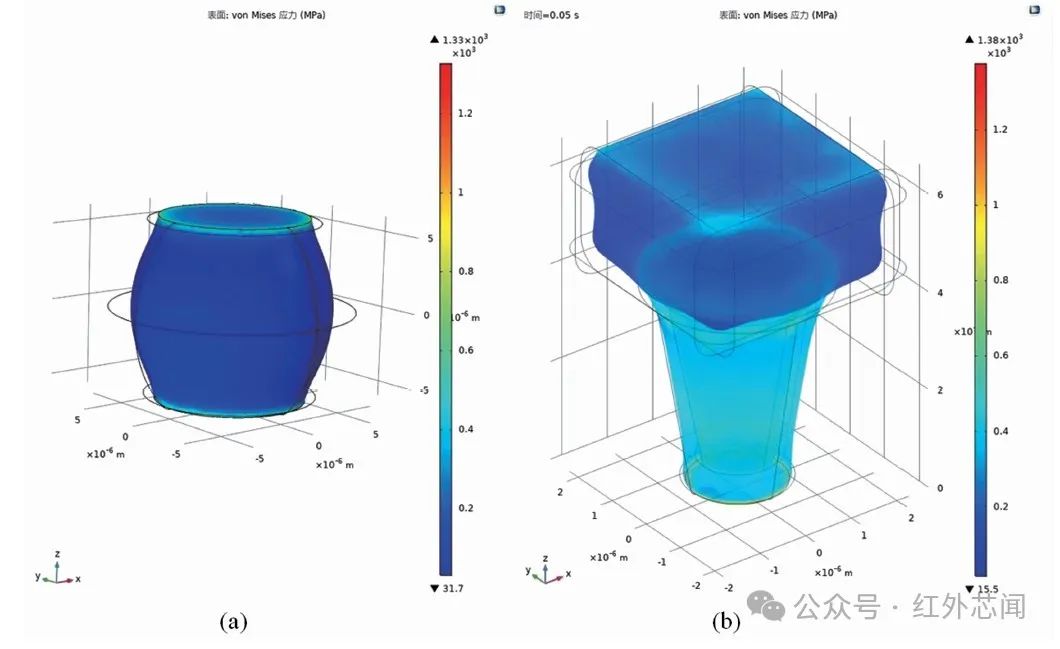

经过仿真计算,对铟凸点互连位点与三维电极互连位点的应力分布进行比较。计算结果表明,两种互连结构的温度从室温降低至77 K的过程中,产生的热应力极值相当,均为1300 MPa左右。但是铟凸点与碲镉汞芯片和读出电路接触的两端均存在高应力集中区域。而三维电极的高应力集中区域仅存在于读出电路端,如图2所示。因此可以推断三维电极互连技术路线使探测器的长期可靠性更高。

图2 应力仿真结果:(a)钢凸点互连位点;(b)三维电极互连位点

为了在读出电路表面制备出高质量的三维电极,首先需要在其表面完成高质量的大深宽比光刻图形转移,并且保证图形在后续金属生长过程中不会由于温度升高而发生形变,使最终金属电极的形貌符合初始设计。常规光刻工艺过程中,光刻胶曝光后烘烤的主要目的是光刻消除驻波效应,因此普遍时间设置较短。但为了提升光刻图形强度,需要适度延长曝光后的烘烤过程。这样不仅可以充分消除光刻图形的驻波效应,同时使光刻胶溶剂有效挥发,提升光刻胶的强度。

在光刻胶显影后光刻图形已经形成,此时再次进行长时间高温烘烤会导致光刻图形顶部与底部光刻胶溶剂的挥发速率不同,使光刻图形发生形变。因此需要特殊设计光刻胶曝光显影后的烘烤过程,均衡释放光刻图形各个部分的光刻胶溶剂,从而避免大深宽比光刻图形发生形变,同时提升光刻图形的坚固程度。所以可将长时间曝光显影后的烘烤过程分割成多个高温烘烤阶段,并加入多个不同温度的低温保持过程,进而释放由于光刻胶溶剂挥发导致的内部应力,防止发生龟裂和变形。最后待光刻图形自然降温至室温后,再进行后续工艺。

通过此方法制备的光刻图形具有深宽比大、侧壁陡直度高、图形在高温环境下不易变形的优点,可以保证在后续的金属生长和离子刻蚀工艺过程中光刻图形不发生形变,最终制备出几何尺寸与设计值相近的三维电极。

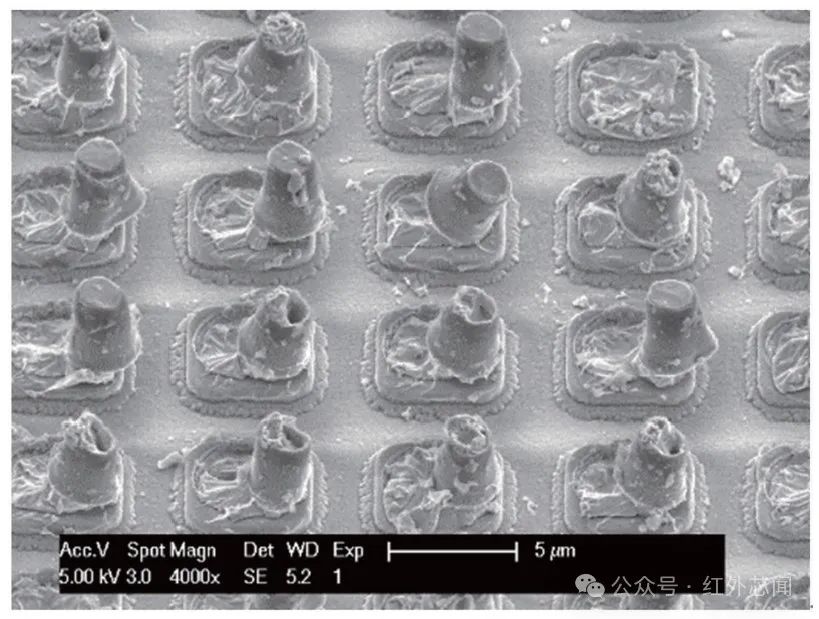

三维电极的具体制备过程如下:在待制备三维电极的读出电路表面使用上述优化的光刻工艺,制备出预先设计好的高深宽比三维电极图形;然后在光刻图形表面上,按照预先设计生长一定厚度的多种金属复合膜层;使用离子铣选取合适的刻蚀角度,对读出电路表面的复合金属膜层进行刻蚀,断开三维电极与表面多余金属的连接部分;最后将读出电路放入80℃的N-甲基吡咯烷酮(NMP)中浸泡,使用剥离工艺完成三维电极的制备(见图3)。上述所有工艺过程均需控制温度,全过程中读出电路表面的温度必须低于90℃。

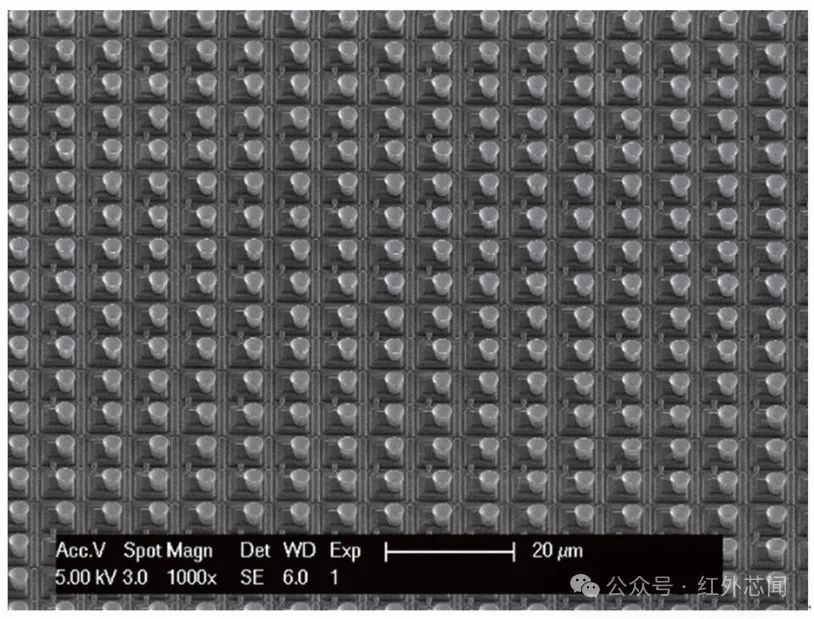

图3 三维电极阵列的扫描电镜图

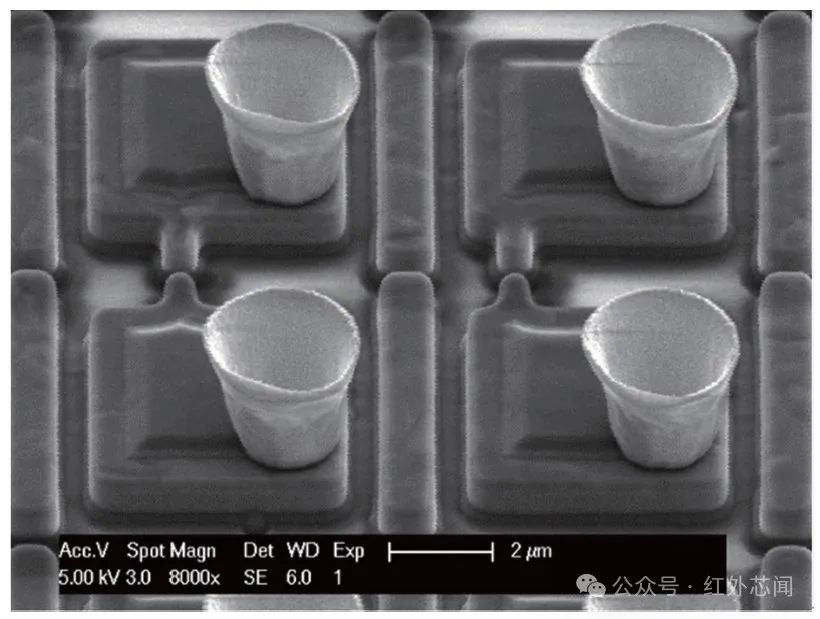

读出电路加工过程中经常使用的金属有Cu、Sn、Ag、Al等。这些金属所制备的结构与读出电路表面具有很高的粘附性,并且不会造成读出电路性能损伤。因此,为了兼顾三维电极在读出电路上的牢固程度和强度,可以选取Cu、Sn、Ag、Al等多种金属组合成复合膜层来制备三维电极。根据三维电极组成金属的不同,适当调整离子刻蚀工艺参数。最终制备出的三维电极高度可达到3.8 μm(见图4),高度非均匀性小于3%。与碲镉汞芯片表面铟饼互连后,可形成高度约为5 μm的结构(见图5)。

图4 油Cu、Sn、Ag、Al组成的三维电极的扫描电镜图

图5 多金属层三维电极互连效果

倒装互连完成后,将样品切片。使用扫描电镜(SEM)观察发现,将带有三维电极的读出电路与碲镉汞芯片进行互连的过程中,由于仅三维电极的顶部边缘与铟饼表面接触,并且三维电极的强度远大于铟饼,因此随着互连压力的增加,三维电极会插入铟饼体内(见图5),实现高强度连通。三维电极与铟饼的接触面积远小于铟凸点技术路线,相同的互连压力可以产生更大的压强,因此探测器完成互连所需的压力大幅下降。互连压力的降低,有利于对碲镉汞芯片的保护,降低其在互连工艺过程中被损坏的概率。

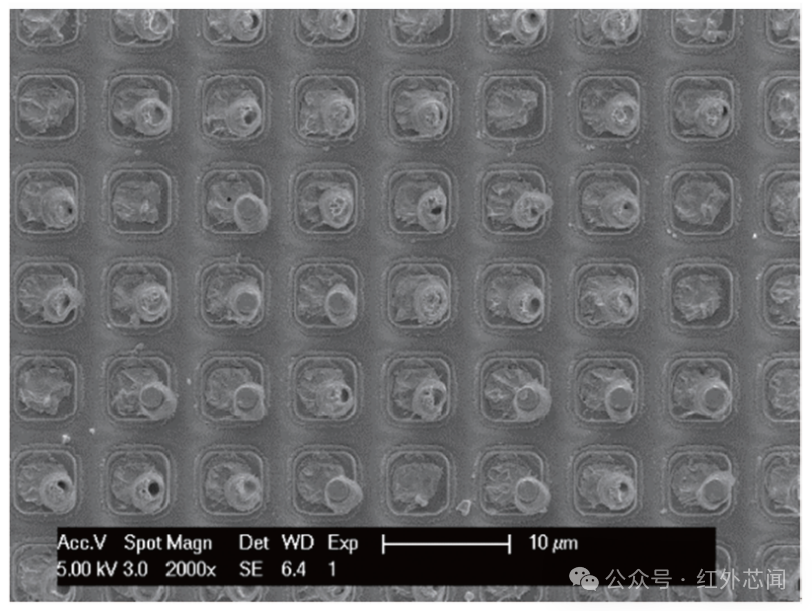

样品倒装互连完成后,经过高温回流,使互连位点的金属铟和三维电极形成互融,互连位点进一步得到了加固。此后,为了便于观察互连工艺的实际效果,使用物理方法将碲镉汞芯片与读出电路分离。通过SEM观察发现,读出电路和碲镉汞芯片表面上的三维电极仍能保持完整。经计算可得,单个三维电极在经受7.6×10⁻⁵ N的压力并对铟饼产生约 2.64×10⁷ Pa的压强后,仍然能保持形态完整。这充分说明多金属层三维电极具有很高的强度,经过互连回流工艺后不会形变(见图6)。

图6 与芯片分离后的读出电路

与此同时,有些三维电极受限于互连设备的精度,并未与碲镉汞芯片的铟饼中心对准,但是三维电极与铟饼连接的牢固程度没有受到影响。而且像元位置仍然实现了连通,相邻像元之间也没有发生连接,因此整体像元连通率并没有受到影响。这表明三维电极互连技术路线可以弥补互连设备误差对芯片连通造成的负面影响,降低倒装互连工艺对精度的需求,提升探测器互连工艺的稳定性和成品率(见图7)。

图7 三维电极与铟并未对准

结束语

综上所述,利用三维电极互连技术路线可以制备出高度和高度均匀性均满足倒装互连工艺需求的7.5 μm像元间距互连位点。碲镉汞芯片与读出电路完成倒装互连后,互连位点的强度满足需求。对比铟凸点互连技术路线,三维电极互连技术路线需要的互连工艺精度、实现难度大幅降低,可以保证实现较高的工艺成品率和工艺稳定性。通过仿真模型可以看出,三维电极互连技术路线减少了互连位点在降温过程中的高应力集中区域,有利于提高7.5 μm像元间距红外探测器的性能稳定性和长期可靠性。三维电极的上述优势,使得此技术路线可以继续向5 μm像元间距发展,为更小像元间距探测器的研制提供了技术基础。其在小间距、超大面阵、垂直集成等多类型碲镉汞红外探测器的研制过程中广泛应用,可以大幅降低此类探测器的倒装互连工艺难度,进而提升探测器的成品率。

审核编辑:刘清

-

位置敏感探测器测量电路噪声分析2010-04-22 0

-

【testo 红外热像仪申请】被动红外探测器2015-12-11 0

-

红外辐射探测器2017-12-27 0

-

honeywell火焰探测器2018-04-27 0

-

红外探测器2019-04-16 0

-

三波段红外火焰探测器参考设计2020-07-09 0

-

CAD中如何布置火灾探测器?消防探测器范围计算2021-04-28 0

-

红外探测器的硬件部分该如何去设计呢2022-01-27 0

-

主动红外探测器和被动红外探测器的主要不同2020-02-25 12776

-

二类超晶格制冷红外焦平面探测器2022-10-31 1247

-

红外探测器——热探测器详解2022-11-08 1809

-

短波红外单光子探测器的发展2023-06-28 593

-

红外探测器的分类2023-07-11 1354

-

红外探测器:热探测器与光子探测器2023-07-19 1384

-

红外探测器有几种?如何划分?2023-08-02 1212

全部0条评论

快来发表一下你的评论吧 !