影响电源噪声测试准确性的因素

测量仪表

描述

1 日益发展的技术对芯片电压测试的挑战

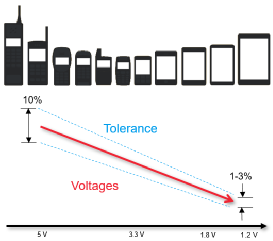

随着5G、车联网等技术的飞速发展,信号的传输速度越来越快,集成电路芯片的供电电压随之越来越小。早期芯片的供电通常是5V和3.3V,而现在高速IC的供电电压已经到了2.5V、1.8V或1.5V,有的芯片的核电压甚至到了1V。芯片的供电电压越小,电压波动的容忍度也变得越苛刻。对于这类供电电压较小的高速芯片的电压测试用电源噪声表示,测求要求从±5%到 ±-1.5%,乃至更低。

如上图1,日益发展的技术对芯片电压测试的挑战。 如果芯片的电源噪声没有达到规范要求,就会影响产品的性能,乃至整机可靠性。因此工程师需要准确地测量现代电路产品中的芯片电压的电源噪声。

2 芯片电源噪声的特点

2.1 更小幅度,更高频率

以往电源噪声的要求维持在几十mV的量级,而随着芯片电压的降低,很多芯片的电源噪声已经到了mV的量级,某些电源敏感的芯片要求甚至到了百uV的量级。直流电源上的噪声是数字系统中时钟和数据抖动的主要来源。处理器、内存等芯片对直流电源的动态负载随着各自时钟频率而发生,并可能在直流电源上耦合高速瞬态变化和噪声,它们包含了1 GHz以上的频率成分。

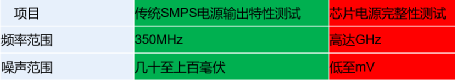

因此与传统的电源相比,芯片电源的噪声具有频率高/幅度小等特点,这就为了工程师准确地测得芯片的电源噪声带来了挑战。

如上表1,传统电源和芯片电源频率和噪声范围。

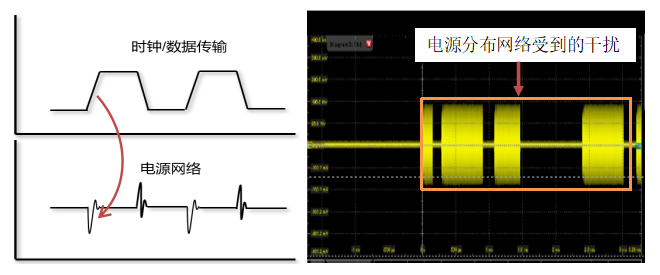

2.2 电源分布网络(PDN)引入的噪声干扰

为了保证电路上各个芯片的供电,电源分布网络(PDN)遍布整个PCB。如果电源分布网络靠近时钟或者数据的PCB走线,那么时钟/数据的变化会耦合到电源分布网络上,也会成为电源噪声的来源。在这种情况下,工程师还需要定位电源噪声的来源,以便后续调整PCB的布局和布线,减少PDN网络受到的干扰。

上图2,时钟/数据传输线耦合到电源分布网络的干扰。

3 影响电源噪声测试准确性的因素

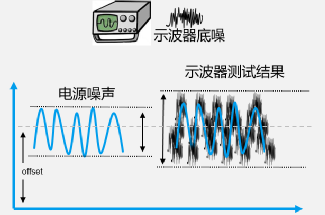

示波器是电源噪声测试的重要仪器。为了能够准确地测量GHz带宽内mV级别的电源噪声,并定位干扰电源分布网络的噪声来源,需要考虑如下因素:示波器的底噪,探头的衰减比,示波器的偏置补偿能力,探头的探接方式,以及示波器的FFT能力等等。 3.1 示波器底噪

示波器本身是有噪声的。当示波器测试电源噪声时,其底噪会附加到被测的电源噪声上,进而影响电源噪声的测试结果。

如上图3,示波器底噪对电源噪声测试结果的影响。

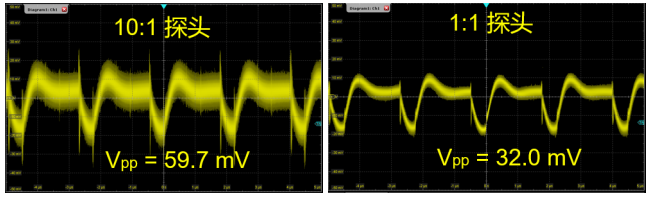

3.2 探头的衰减比

目前最常用的500MHz带宽的无源探头的衰减比为10:1,其会放大示波器的底噪,影响电源噪声测试的不确定性。

如果用传统的衰减比为1:1的无源探头,可以避免放大示波器的底噪。但是这种探头的带宽一般在38MHz,无法测到更高频率的电源噪声。同样会影响电源噪声测试的不确定性。

所以,为了准确测量电源噪声,需要一款衰减比为1:1,带宽到GHz的探头。

如上图4,探头的衰减比对电源噪声测试的影响。

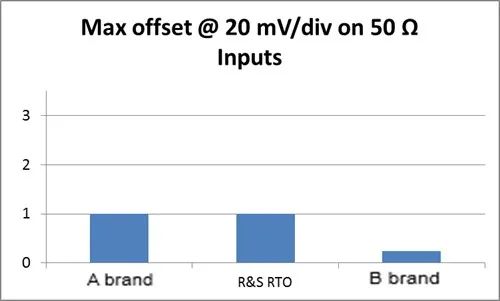

3.3 示波器的偏置补偿能力

电源噪声是叠加在芯片直流电压上的噪声,为此需要将示波器的偏置电压设到与直流电压相等的水平,再测量电源的噪声。例如某芯片的供电电压是3.3V,首先将示波器的偏置电压调到3.3V,然后再测试3.3V直流电源上的噪声波动,但是示波器在该偏置电压的垂直挡位会受限,一般只能到20mV/div,用来测试mV级别的电源噪声,会带来很大的误差。

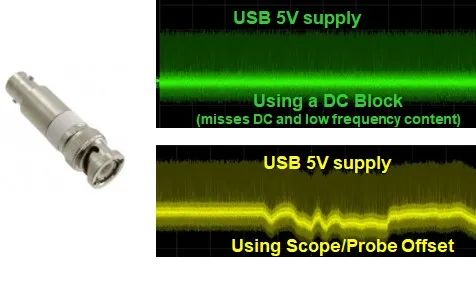

为了解决类似问题,有的工程师使用隔直电容去除直流,但会导致直流电源压缩和丢失低频漂移信息。如果电容值选取不当,还会影响高频能量。

如上图5,示波器的偏置补偿能力受限。

如上图6,隔直电容影响低频信息。

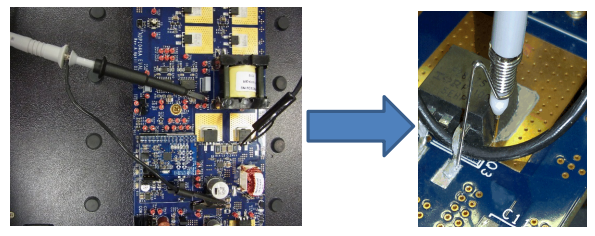

3.4 探头的探接方式 电路形态各异,需要有更灵活的方法来进行信号的探接。探接的稳定性和寄生参数对被测电源电路的影响不可忽视,所以需要尽量贴近芯片的管脚,并使用短地线。

如上图7 贴近芯片管脚,使用短地线。

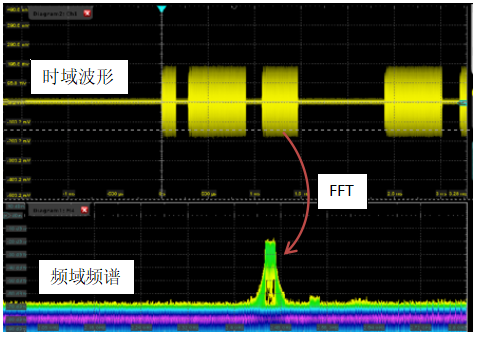

3.5 示波器的FFT能力

由于电源分布网络PDN会受到干扰噪声的来源,因此需要示波器具有强大的FFT分析能力,以便分析的干扰噪声的频率,进而排查噪声的源头。

如上图8所示,FFT分析电源噪声的频谱。

审核编辑:黄飞

-

系统快速性、稳定性和准确性之间的权衡2013-07-28 0

-

如何降低测试中的噪声?2015-09-17 0

-

如何提高工程预算的准确性2016-07-25 0

-

影响电源噪声结果准确性的因素知多少?2019-01-02 0

-

电子书:电源噪声应对措施2019-02-26 0

-

NI公司u***-4065的准确性和速度问题2020-11-24 0

-

如何测试运算放大器噪声模型的准确性?2021-04-12 0

-

如何确认延时函数时间的准确性?2022-01-27 0

-

简谈影响气密性防水测试仪准确性的因素2020-05-19 680

-

了解电源监视器的准确性2021-04-18 497

-

IEEE 802.11ax站点上行链路准确性测试方案2022-03-04 2449

-

如何准确测试出电源纹波噪声值2022-09-25 1482

-

三步准确测试出你的电源纹波噪声值2022-09-27 2876

-

电源纹波噪声测试方式哪种更准确2023-12-19 615

-

影响电源噪声测试准确性的因素?如何准确测量电源噪声?2024-04-10 491

全部0条评论

快来发表一下你的评论吧 !