深维科技-北京大学合作团队在FPGA'24布线加速竞赛中夺得佳绩!

描述

获 奖 情 况

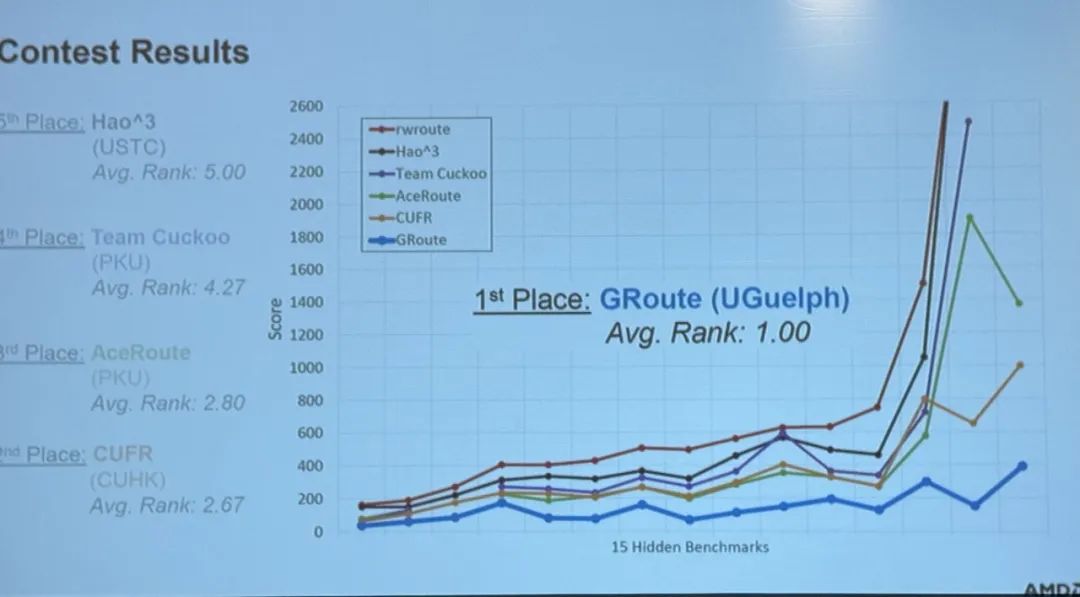

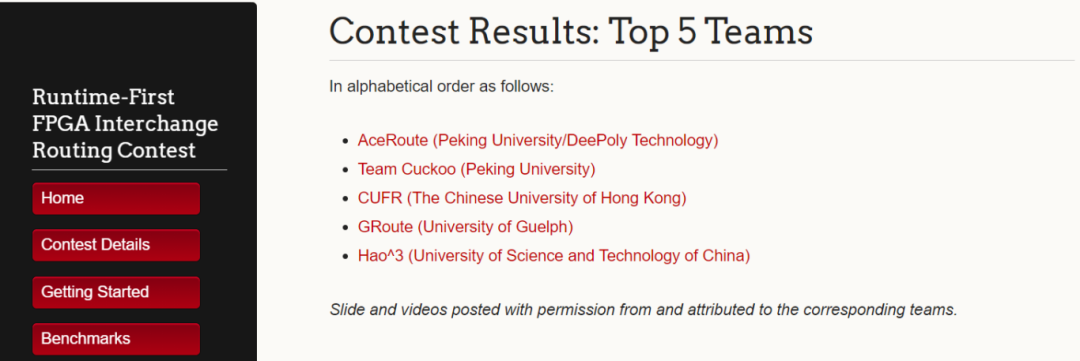

美国西部时间2024年3月4日,我司与北大合作团队在FPGA'24布线加速竞赛中获得优异的成绩。此次比赛由AMD公司组织并在美国加州举办,共历时3个月,来自北京大学、香港中文大学、中国科学技术大学、加拿大奎尔夫大学等40支队伍、遍布15个国家和地区、超过150名选手报名参赛。

赛事现场

经过激烈的角逐,最终有十支队伍成功入围决赛。决赛通过15个隐藏用例的评比,计算出各个队伍的平均分数,并根据最终得分进行排名。AceRoute以优异的成绩获得了该次比赛的第三名。

AceRoute介绍

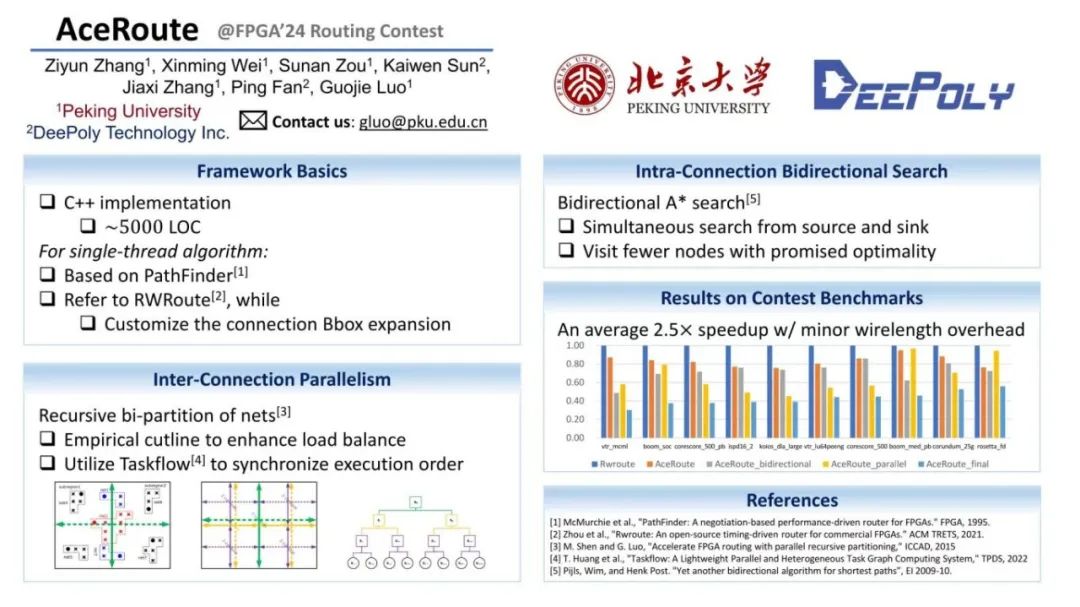

AceRoute基于PathFinder协商布线算法,采用迭代方法消除拥塞并优化其关键路径,参考RWRoute的拥塞代价管理策略,实现高效的C++布线引擎。同时提出自定义的扩展连接边界框的方法,以更好的管理连接并优化布线结果。这些方法的综合应用有助于提高电路性能和可靠性。

Aceroute采用递归网表分割,将网表分割成3到n个平衡子集。根据源和汇位置设计切割线,每次迭代地划分子集,利用任务流确保执行顺序并避免冲突。后期迭代中,动态重新分区以保持负载平衡。

Aceroute在处理内部连接问题时,采用了双向A*算法。这种算法同时从源节点(正向)和汇节点(反向)开始搜索,以寻找最佳路径。这种双向搜索方法在内部连接问题中非常有效,因为它能够减少搜索过程中访问的节点数量,并且能够保证找到的路径是最优的,从而提高了内部连接问题的解决效率。

在竞赛基准测试中,对比AMD/Xilinx研究实验室和比利时根特大学联合研发的高质量布线器RWRoute平均速度提升了2.5倍,而且实现了相同的布线质量。AceRoute同时也成功超越了商业工具Vivado布线器的性能。

审核编辑:刘清

-

嵌入式开发讲义(北京大学)2012-08-14 0

-

北京大学verilog课件2012-10-26 0

-

Verilog超详细教程-北京大学于敦山2017-09-30 0

-

在找一本 硬件十万个为什么(无源器件篇)》是北京大学出版社出版图书。谁有请提供,必有奖励,2022-09-30 0

-

北京大学量子力学课件2008-11-25 719

-

北京大学计算概论(C语言)经典课件—C语言基础2016-08-16 496

-

北京大学将在昌平建人工智能新校区2018-11-14 3728

-

华为任正非带队访问北京大学2020-09-29 2073

-

人工智能顶级学者担任北京大学人工智能院长2020-10-09 2420

-

Imagination和北京大学宣布建立奖学金合作项目2021-04-12 2275

-

概伦电子与北京大学合作 推动EDA领域前沿技术发展2022-05-11 1551

-

概伦电子与北京大学签署合作协议2022-05-11 914

-

歌尔股份与北京大学经济学院举行合作深化校企合作2022-08-09 293

-

北京大学深圳研究生院&知存科技联合实验室揭牌,共谋存算一体化研究2023-06-07 755

-

北京大学高性能计算综合能力竞赛圆满结束2024-04-14 133

全部0条评论

快来发表一下你的评论吧 !