分享一种大型SOC设计中功能ECO加速的解决方案

电子说

1.2w人已加入

描述

大型SOC项目的综合非常耗时间,常常花费好几天。当需要做功能ECO时,代码的改动限定在某些子模块里,设计人员并不想重跑一次完整的综合,这种方法缩短了一轮ECO的时间,保证了项目进度。

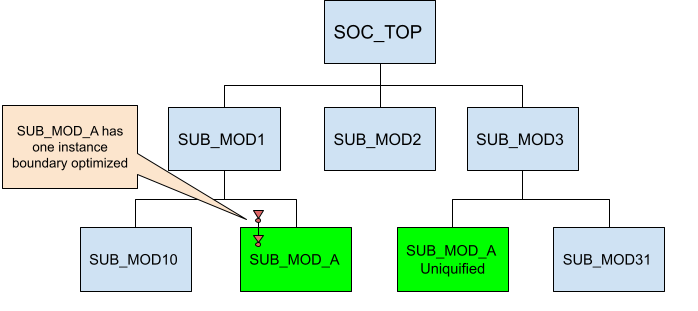

然而,设计时这些子模块经过了物理综合、DFT、后端工具等各种优化。模块例化好几次时,在这些优化后,每一个实例都会出现很多不同的边界优化。下图中,SUB_MOD_A有后端优化,如端口反相。

因此,自动ECO工具必须能够识别和处理这些各种各种的后端优化,处理好每一个模块的特有的复杂情况,并精确修理。

面对这种挑战,GOF中读入了prelayout网表(综合+DFT)来更好地处理边界优化。这其实是可以实现的,我们知道prelayout网表,在做ECO之前,应该与综合网表等价。

在ECO时,为了提取出子模块的边界优化,我们用prelayout网表与老APR网表来做对比。因为ECO作用于各个子模块,相应的边界优化信息又被反标到网表上,这保证了ECO的精度和准确性,又能保证顶层设计的逻辑等价PASS。

read_design命令的-ori_syn参数用来加载prelayout网表。下面一段脚本,先用SUB_MOD_A作参考fix SUB_MOD_A_0,再接着修理SUB_MOD_A_1。最后把顶层设置到SOC_TOP,写出ECO网表。

read_design('-ref', "new_sub_mode_a.gv"); # New synthesized sub-module-A

read_design('-imp', "post_layout.gv"); # Full post layout netlist

read_design('-ori_syn', "pre_layout.gv"); # Full prelayout, equal to post_layout.gv

# Apply ECO to the first instance

set_top_ref("SUB_MOD_A"); # Must set REF scope

set_top("SUB_MOD_A_0"); # Uniquified name for the first instance

fix_design;

# Apply ECO to the second instance

set_top_ref("SUB_MOD_A"); # Must set REF scope

set_top("SUB_MOD_A_1"); # Uniquified name for the second instance

fix_design;

set_top("SOC_TOP");

report_eco();

write_verilog("post_layout.eco.gv"); # Full post layout netlist after ECO

可以处理完整网表的ECO,但不需要对整个设计重新综合,这就会格外地节省时间。由于GOF提取出了边界信息,ECO的结果就会有更高的准确程度。

审核编辑:刘清

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

介绍一种汽车无线接入技术的解决方案2021-05-12 0

-

求一种基于ZigBee的驾驶辅助系统解决方案2021-05-14 0

-

介绍一种基于融合SoC处理器的平台软件解决方案2021-05-17 0

-

分享一种实用的WiFi语音解决方案2021-05-19 0

-

分享一种实用的NFC电子钱包解决方案2021-05-19 0

-

求一种射频开关的解决方案2021-05-21 0

-

分享一种实用的Compuware-Emulex解决方案2021-05-24 0

-

分享一种WLAN射频优化的解决方案2021-05-24 0

-

分享一种高性能的FM内置天线解决方案2021-05-26 0

-

分享一种低延迟SGTLCODEC解决方案2021-06-01 0

-

分享一种针对串流媒体音频的多功能解决方案2021-06-02 0

-

分享一种不错的Xilinx Smarter Vision解决方案2021-06-03 0

-

一种基于FPGA的图神经网络加速器解决方案2021-09-25 0

-

一种高效的UPS电源解决方案2021-11-16 0

-

求一种LCD和LED冲突的解决方案2022-01-25 0

全部0条评论

快来发表一下你的评论吧 !