如何实现高功率密度三相全桥SiC功率模块设计与开发呢?

描述

摘要

为满足快速发展的电动汽车行业对高功率密度 SiC 功率模块的需求,进行了 1 200 V/500 A 高功率密度三相 全桥 SiC 功率模块设计与开发,提出了一种基于多叠层直接键合铜单元的功率模块封装方法来并联更多的芯片。利用互感对消效应减小寄生电感,导电面积增加了 1 倍,因此可以减小功率模块的总面积。在电磁学与热力学仿 真分析的基础上,进行了实物制作与性能测试。仿真与实验结果表明:与传统的封装方法相比,该封装方法减少 了 34.9%的尺寸,并减少了 74.8%的寄生电感使得门极具有更高的稳定性,且当直流 300 A 电流时,单相最高结温 为 158 ℃。

如今,三相全桥功率模块广泛应用于电动汽车 与工业驱动领域,并对功率密度提出了越来越高的 要求。为了实现更高的功率密度,须提高功率模块 的开关频率,降低杂散电感,还要增强散热能力。随着宽禁带功率器件的不断发展,碳化硅(silicon carbide,SiC)由于其更高的击穿电压,更高的工作温 度,更低的开关损耗,显示出取代硅基功率器件的 巨大潜力。然而由于封装限制,这些突出的优点目 前还无法在同尺寸的功率模块中得到有效证明。

二维引线键合封装结构工艺已经相对成熟且简 单,因此在商用 SiC 功率模块设计中得到广泛应用。但是这种二维的功率模块封装结构通常具有较大的寄生电感,这很大程度上限制了SiC 器件的开关速 度。这种寄生电感的存在还会导致造成门极的不稳 定振荡,阻碍了功率密度的进一步提高。Chen 等提出了一种改进的线键结构,用于 1200 V/60 A SiC 功率模块,在二维模块中采用叠层引线框架, 增强开尔文源极对称性来降低寄生电感。Huber 等提出了一种多直接键合铜(direct bonding copper, DBC)的 600 V/200 A 单相全桥 SiC 功率模块,采用 两层 DBC 实现了低寄生电感,功率器件焊接在双层 DBC 的顶层。Luo 等基于叠层 DBC 开发了 1200 V120 A 的半桥 SiC 功率模块。然而,对大功率下三相全桥的叠层 DBC 功率模块的研究相对较少,特别 是在面对更大电流和更高功率的情境下,对于叠层 DBC 功率模块芯片热稳定问题的深入研究尚需进 一步展开。

基于上述分析,本研究提出了一种多叠层 DBC 单元的封装结构,并研制了 1 200 V/500 A 三相全桥功率模块,该模块利用 pinfin 散热器进行水冷散热, 并进行了电气性能与散热性能仿真与实验。

1 功率模块设计和仿真

1.1 叠层 DBC 单元设计

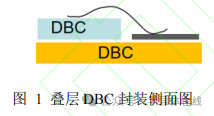

叠层 DBC 封装结构侧面图如图 1 所示,底部 DBC 和顶部 DBC 分别传导电流,SiC MOSFET 芯 片的漏极焊接在底层 DBC 上,门极与源极通过键合 线与顶层 DBC 相连接。

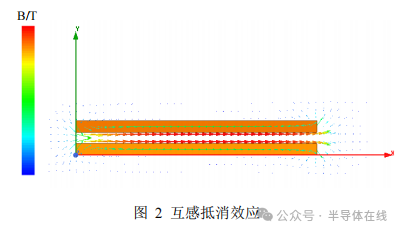

互感抵消效应如图 2 所示,叠层 DBC 的电流 路径重叠且方向相反,该设计采用了互感抵消效应, 通过使电流在相邻层之间反向流动,显著降低寄生 电感,这一技术在叠层母排设计中已经得到广泛应 用。相相对于传统的二维封装结构,这种方法可以 有效降低杂散参数,从而改善功率模块的整体性能。

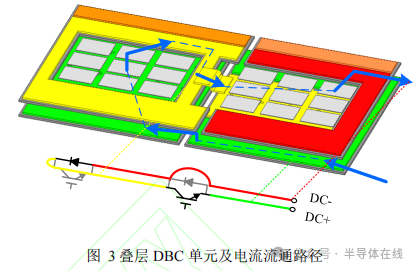

叠层 DBC 单元及电流流通路径如图 3 所示, 尺寸为 59 mm × 32 mm。通过在 Ansys Q3D 中提取 寄生电感,该功率模块的总寄生电感仅为 4.74 nH。相较之下,具有相同额定功率和尺寸为 64 mm×44 mm 的传统二维布局模块的寄生电感值为 18.84 nH。

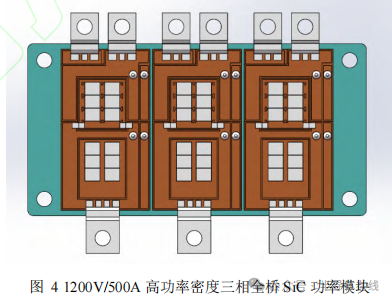

由于电流路径增加了 1 倍,因此在相同的封装 面积下,叠层 DBC 单元允许更多的芯片并联,从而 显著增加了 SiC 功率模块的功率密度。这种方法工 艺相对简单,有望降低生产成本,提高生产率。如 图 4 所示,最终设计的 1200 V/500 A 高功率密度三 相全桥 SiC 功率模块的尺寸与 EconoDUAL 封装的 商用单相全桥模块一致。

1.2 散热设计

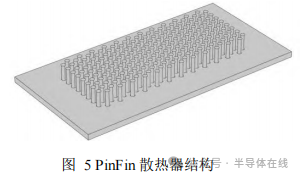

冷却系统在电力电子系统的总质量和总体积 中占据相当大的比例。为了实现更高的功率密度, 功率模块通常采用 PinFin 散热器来提升散热性能。本研究所采用的 PinFin 散热器结构图 5 所示,这种 结构在相对较小的空间内提供了更大的散热表面积, 使其与周围环境更有效地交换热量,从而提高了整 体散热性能。

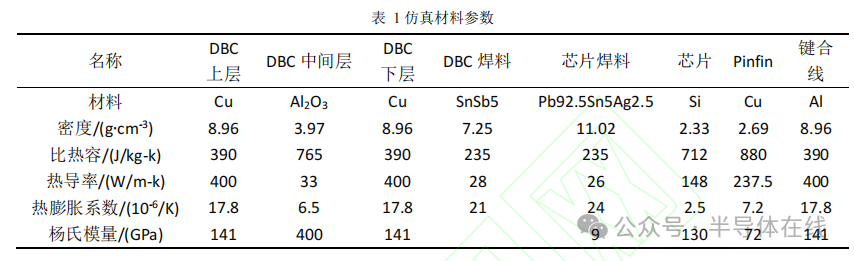

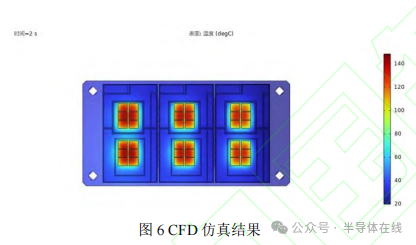

计算流体力学(computational fluid dynamics, CFD)仿真模型根据所需工况设置每颗芯片功率 150 W,三相模块总热耗率为 5 400 W。入口水流速 为 0.52 m/s,水温 25 ℃,出口压力为静压,本研究 设计的功率模块各部分材料参数如表 1 所示。仿真 结果如图 6 所示,根据仿真结果分析,芯片最高结 温 148.42 ℃,芯片平均结温 123.24 ℃。最高结温和 平均结温的数据有助于评估功率模块散热设计的性 能,验证提出叠层 DBC 单元封装结构的可行性。

2 实验验证

2.1 模块制作

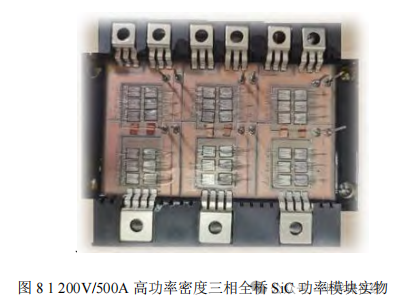

功率模块封装工艺制作流程如图 7 所示,首先 是芯片出厂检测与功率模块封装的设计,之后进行 芯片溅射、真空焊接、超声波焊接和模块真空灌封, 最后进行模块的检测。在制作流程中,芯片的出厂 检测和功率模块的封装设计确保了所使用的芯片质 量可靠且符合设计要求。芯片溅射、真空焊接、超 声波焊接等工艺步骤用于将芯片按照电路拓扑连接 到封装结构中。模块真空灌封则有助于提高封装的 密封性,确保内部芯片在恶劣环境中的可靠运行。图 8 展示了设计的 1 200 V/500 A 高功率密度三相 全桥 SiC 功率模块的实物。

2.2 电气性能测试

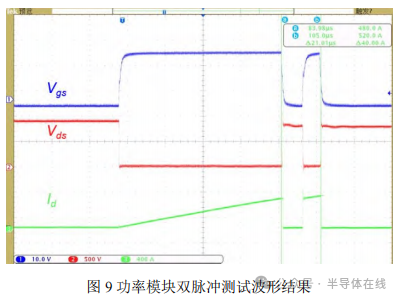

开关器件的动态电气性能可以通过双脉冲电路 获得,下管用作被测器件。栅极-源极电压 Vgs 与漏极-源极电压 Vds 使用高压隔离差分探头测量,漏极 电流 Id 使用罗氏线圈电流探头测量。上管的栅极承 受负电压,因此上管关闭,只有续流二极管在工作, 由图 9 所示的测试结果波形可以看出,制作的功率 模块通过了 800 V/500 A 的双脉冲测试,证明了所 提出的功率模块在高电压和大电流条件下具有可靠 的动态电气性能,符合设计和规格要求。

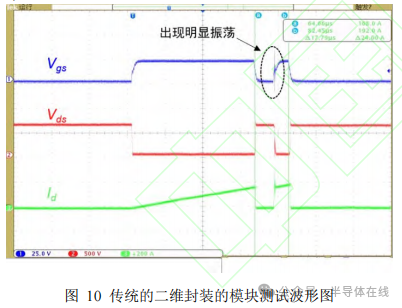

传统的二维封装结构由于杂散电感更高,在电 流为 200 A 时门极已经出现了明显振荡,如图 10 所 示。

门极振荡可能导致不稳定的工作状态,与之相 比,本研究使用的叠层 DBC 封装结构通过减小杂散 电感,提高了功率模块的动态性能。

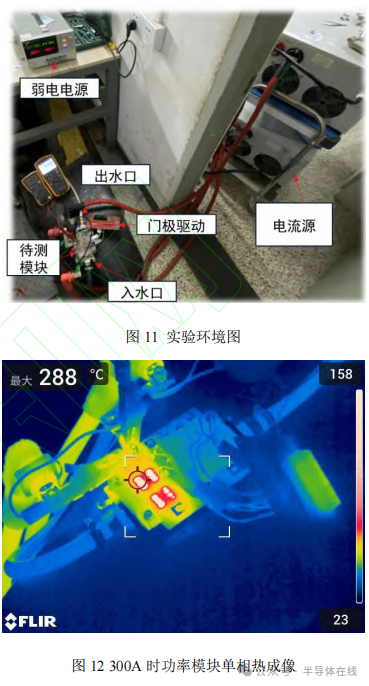

2.3 散热性能测试

为了更全面地评估功率模块的散热能力,采用 功率模块单相全桥直通的方式,通过红外热成像仪 对功率模块进行观察,以获取功率模块的最高结温。测试实验环境如图 11 所示,其中弱电电源为门极驱 动供电,电流源提供大电流。最终测试功率模块直 通电流值为 300 A。图 12 为 300 A 时功率模块热分 布结果图,根据结果可知,在这种条件下,功率模块单相最高结温约为 158 ℃左右。这一实验结果提 供了对功率模块在大电流通流情况下的实际工作状 态的直观了解,为优化散热设计和确保功率模块的 可靠性提供了参考,证明了大功率下本研究提出的 叠层 DBC 功率模块设计的可行性。

3 结论

本研究针对电动汽车与工业驱动领域,设计并 开发了一款 1 200 V/500 A 高功率密度三相全桥 SiC 功率模块。提出的采用多叠层 DBC 单元的设计方 法,简化了制造流程,降低了成本,可以提高生产 效率。基于仿真结果进行了实物的设计与制作,并 进行了电气和散热性能测试。结果表明:相较于传 统封装方法,提出的封装方法在尺寸上减小了 34.9%,寄生电感减少了 74.8%,使得门极具有更高 的稳定性。在直流 300 A 电流通流的情况下,单相 最高结温为 158 ℃。本研究提出的三相全桥 SiC 功 率模块设计方法有助于推动电动汽车电机驱动系统 功率密度的提高。

审核编辑:刘清

-

beilin001

03-29

0 回复 举报中科院电工所宁老师组的成果 收起回复

beilin001

03-29

0 回复 举报中科院电工所宁老师组的成果 收起回复

-

如何在高功率密度模块电源中实现低损耗设计2016-01-25 0

-

【论文】基于1.2kV全SiC功率模块的轻型辅助电源2017-05-10 0

-

10kW三相3级并网逆变器参考设计包括BOM及层图2018-10-29 0

-

全SiC功率模块的开关损耗2018-11-27 0

-

全SiC功率模块介绍2018-11-27 0

-

权衡功率密度与效率的方法2020-10-27 0

-

如何实现功率密度非常高的紧凑型电源设计?2020-11-24 0

-

什么是功率密度?如何实现高功率密度?2021-03-11 0

-

什么是功率密度?限制功率密度的因素有哪些?2021-03-11 0

-

高功率密度的解决方案2022-11-07 0

-

如何使用SiC功率模块改进DC/DC转换器设计?2023-02-20 0

-

用于汽车应用的碳化硅MOSFET功率模块2023-02-20 0

-

三相全桥逆变器的并联均流设计方案2023-09-19 0

-

解决方案丨三相全桥PRCP开发套件实验系统方案2023-11-16 0

-

三菱电机成功开发6.5kV全SiC功率模块 实现世界最高功率密度额定输出功率2018-02-03 8644

全部0条评论

快来发表一下你的评论吧 !