24位高性能模数转换器ME9620应用经验与总结

模拟技术

描述

ME9620是微盟电子推出的一款适合宽带宽应用的24位、144kSPS的8通道同步采样工业Δ-Σ ADC。

传统的具有较高漂移性能的工业Δ-Σ ADC采用导通带宽下降幅度很大的数字滤波器,来尽可能满足DC测量需求的有限信号带宽。而针对音频应用的高分辨率ADC虽能够提供更大的可用带宽,但偏移与漂移指标远低于工业ADC的需求。ME9620将两种类型的转换器相结合,实现优良的DC与AC规范的高精度工业测量。

ME9620内部集成有多个独立的高阶斩波稳定调制器和FIR数字滤波器,可实现4/8通道同步采样,支持高速、高精度、低功耗、低速4种工作模式。ME9620可通过设置相应的输入/输出引脚选择工作模式,无需寄存器的编程,其数据输出可选串行SPI或FRAME-SYNC接口,便于连接至DSP、FPGA及微控制器。每个接口均支持菊花链,可满足要求严格的多通道信号采集应用,如振动分析、医疗监控、声学系统、动态应变测量及压力测量设备等。

01

供电电源

ME9620需要3个供电电源:

模拟电源电压AVDD: 4.5~5.5V

数字电源电压DVDD: 1.65~1.95V

I/O供电电压IOVDD: 2.7V~3.6V

建议每个电源引脚处均需放置一个10uF钽电容和0.1uF陶瓷电容。ME9620严格要求电源稳定,不可与其它易造成电源不稳定的器件共用电源。

02

模拟信号与参考电压输入

ME9620的8个ADC通道支持差分信号输入。为了不发生溢出,请保证差分输入范围不大于参考电压范围。输入信号的共模理论上支持从0到AVDD电平的范围,但为了尽可能发挥ADC的性能,同时可以提高信号幅度,建议将输入共模配置在AVDD/2附近的电平。

芯片输出的VCOM信号作为ADC内部工作的共模电平,需要外置稳压电容保证其电压稳定,可在片外连接一个缓冲器后的输出作为ME9620输入差分信号的共模电平使用,以保证芯片内外信号电路共模的一致性。

为了简化应用,建议VREFN连接到AGND。为了保证ADC性能不受参考源的影响,应用时需要在片外通过一个高精度低噪声稳压参考源产生VREFP电压,并在VREFP与VREFN管脚两端挂接1uF以上量级的稳压陶瓷电容。

03

工作模式设置

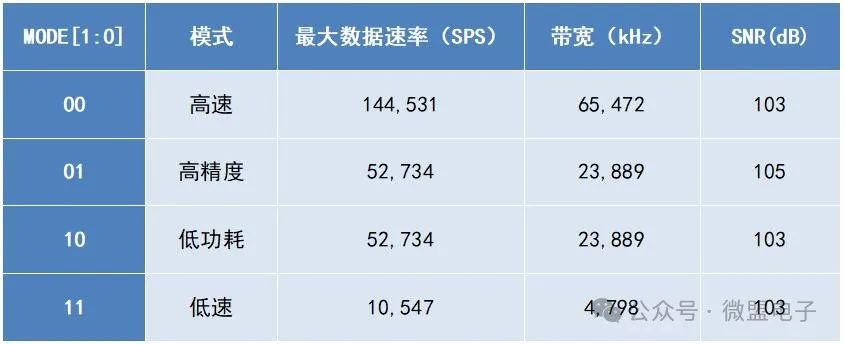

ME9620共有4种工作模式供选择,由MODE[1:0]引脚控制决定。

04

时钟输入

ME9620必须有时钟输入才能运行。外部时钟频率(fCLK)的选择不会影响其分辨率。

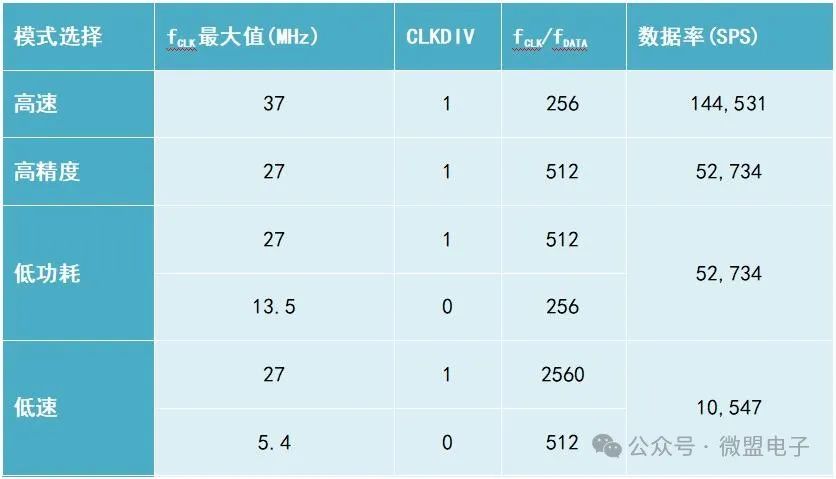

当为高速模式时,fCLK最大可为37MHz,其他三种模式时,最大输入时钟为27MHz。且当fCLK>27MHz时,只能采用FRAME-SYNC方式读取数据。

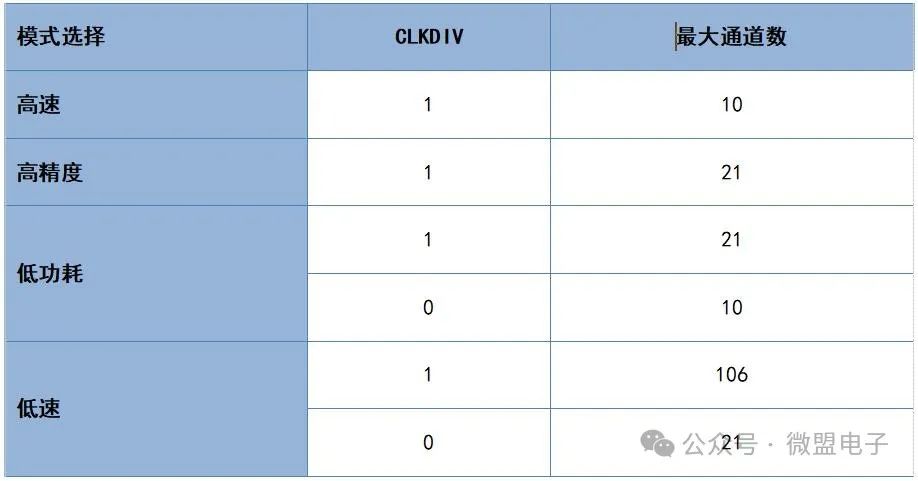

ME9620的数据输出率与fCLK具有固定的比例关系,且低功耗、低速模式下,CLKDIV能够对fCLK分频。另外两种模式下,CLKDIV必须为1,具体关系如下表所示:

05

输出方式设置

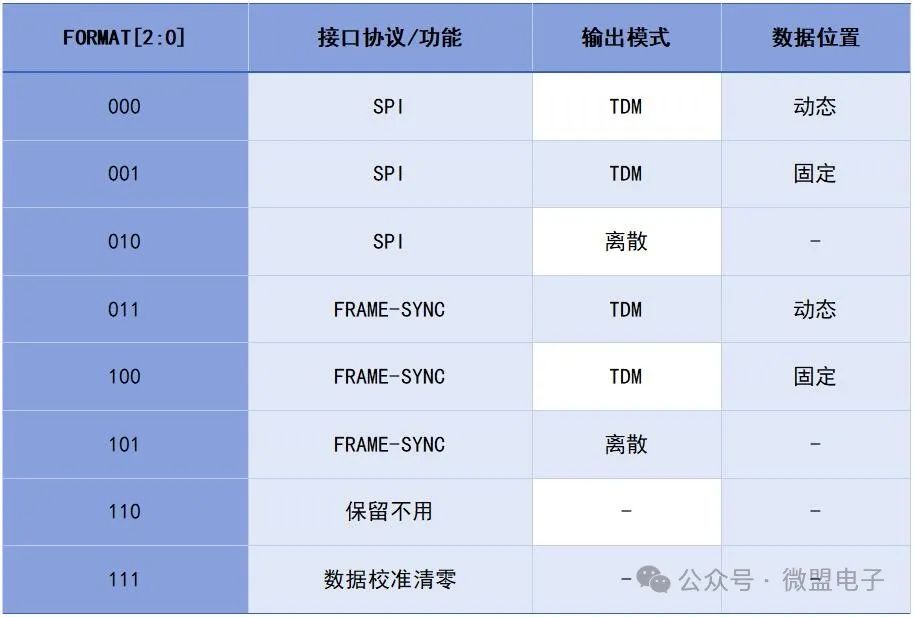

转换后的数据输出采用串行接口,可采用两种接口协议:SPI协议或FRAME-SYNC协议,同时也可选择不同的数据输出格式(TDM/离散、固定/动态数据位置)。协议和数据输出格式的选择是由引脚FORFMAT[2:0]控制,如下表所示:

数据对应SPI和FRAME-SYNC接口协议,或者通过各自的通道DOUT引脚以并行数据格式(离散模式)移位输出,或者所有通道的数据以串行格式通过公共引脚DOUT1(TDM 模式)移位输出。

TDM表示8个通道数据全部由DUOT1输出,CH1在前,CH8在后。此时若数据位置为“动态”则表示:若某通道关闭,则该通道仍然输出,输出数据为0;若数据位置为“固定”,则如果某通道关闭,该通道不输出,直接输出下一通道数据。

06

数据格式

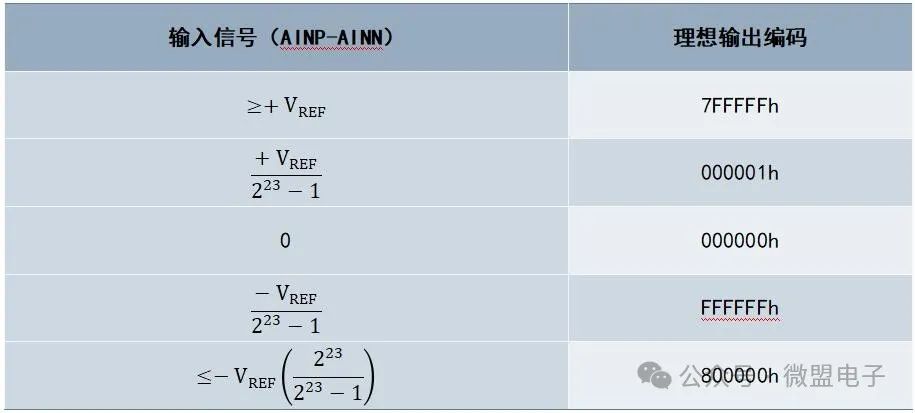

ME9620输出数据位宽为24位,正满量程为7FFFFFh,负满量程为800000h,理想输出码与输入信号关系如下表所示:

07

同步

ME9620可以通过将 引脚拉低后,再将引脚返回高电平来实现同步。当引脚变为低电平时,转换过程停止。当

引脚拉低后,再将引脚返回高电平来实现同步。当引脚变为低电平时,转换过程停止。当 引脚返回高电平时,转换过程重新开始。由于ME9620转换器以相同的主时钟并行运行并使用相同的

引脚返回高电平时,转换过程重新开始。由于ME9620转换器以相同的主时钟并行运行并使用相同的 输入控制,因此它们始终相互同步。但是,多个器件的同步有些不同。在器件上电时,器件之间内部复位的变化可能会导致转换时序的不确定性。

输入控制,因此它们始终相互同步。但是,多个器件的同步有些不同。在器件上电时,器件之间内部复位的变化可能会导致转换时序的不确定性。

无论接口协议是SPI还是FRAME-SYNC,建议使用来同步所有器件。

08

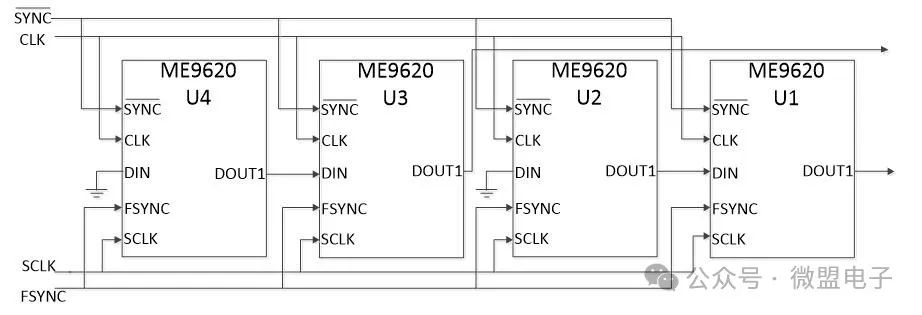

菊花链

多个ME9620可以以菊花链方式连接在一起,以在单个引脚上输出数据。一个器件的DOUT1 数据输出引脚连接到下一个器件的DIN,如下图所示。

以这种方式进行菊花链连接的最大通道数受fSCLK频率、模式选择和CLKDIV的限制。fSCLK的频率必须足够高,以能够在一个fDATA周期内将数据从所有通道中完全移出。下表列出了fSCLK = fCLK时菊花链通道的最大数量。

09

电路设计注意事项

进行ME9620设计时,请注意下列事项:

1)AGND和DGND可以使用同一个地平面。

2)数字输入脚需要串接50Ω电阻,并放置在数字驱动源末端(靠近ME9620)。

3)模拟电路(输入脚)走线必须远离数字电路(输入脚)并防止产生走线交叉。

4)模拟信号参考端接10uF和0.1uF电容。

5)模拟信号输入端必须接驱动,PCB走线短而直,且远离数字信号线。AINP和AINN之间需接1~10nF电容。

6)电源、模拟输入、参考输入的去耦电容必须尽可能的靠近ME9620。

7)时钟线越短越好,且末端接50Ω电阻。要求晶振必须稳定。

审核编辑:黄飞

-

数模和模数转换器2009-09-16 0

-

AD9446BSVZ-100模数转换器2018-10-31 0

-

AD9238BCPZ-65模数转换器2018-11-02 0

-

SAR模数转换器AD7989-1和AD7989-52018-11-29 0

-

6位高性能DS模数转换器LTC24332020-03-11 0

-

带有I2C接口的16位高性能DS模数转换器2020-05-01 0

-

具有2ppm线性度的24位高性能DS模数转换器2020-05-04 0

-

LTC2460:一款带有SPI接口的16位高性能DS模数转换器2020-05-05 0

-

DC1384A-A,演示电路采用带有SPI接口的16位高性能差分模数转换器LTC24522020-05-05 0

-

LTC2471:一款带有I2C接口的16位高性能DS模数转换器2020-05-05 0

-

双通道差分输入微功耗24位无延迟模数转换器2020-06-16 0

-

5962-9581501HXA高端AD模数转换器2020-07-15 0

-

WM8738立体声模数转换器相关资料下载2021-04-26 0

-

24位模数转换器AD7713及其应用2009-03-14 1453

-

ME9620—8通道同步采样24位高精度ADC介绍2023-09-14 2116

全部0条评论

快来发表一下你的评论吧 !