PCB布局丨SMD贴装件和DIP插装件要尽量远离

PCB布局丨SMD贴装件和DIP插装件要尽量远离

描述

在浩瀚的电子世界海洋中,我,小彭,一名PCB layout工程师,每日与无数电子元件共舞,以精密无比的线路为航迹,在设计的无垠海域中破浪前行。然而,今日,我却遇到了一个来自波峰焊的工艺难题。

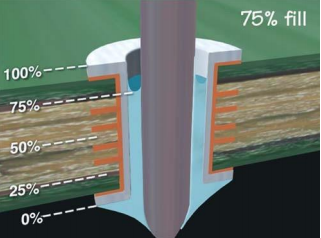

事情是这样的,我日夜精心设计的作品,却在波峰焊后出现了虚焊现象,孔内爬锡高度严重不足,根本无法满足IPC的二级标准。大家都知道,IPC二级标准对于焊接的要求是非常严格的,焊锡必须垂直填充至少75%,且只允许有最多25%的下陷。

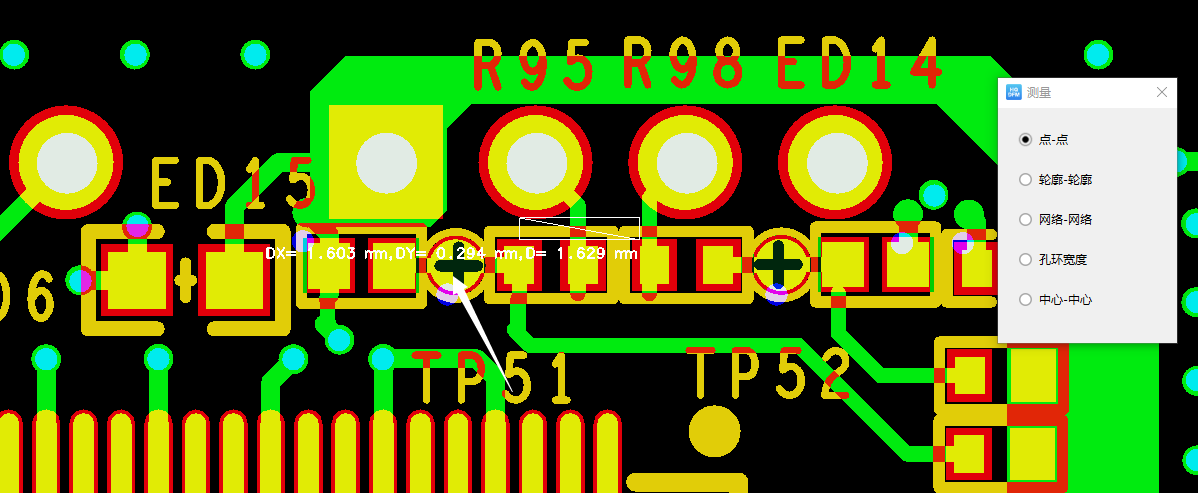

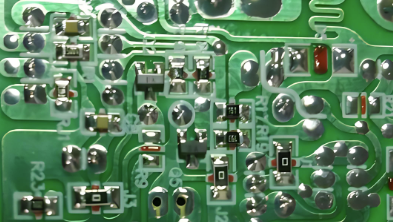

我凝视着虚焊的地方,心中充满了疑惑与不解。为什么DIP插装器件与SMD贴片器件相隔0.2mm这么近,以至于波峰焊无法完美填充?我重新打开设计文件,仔细查看那些元器件的布局,想要找到问题的根源。

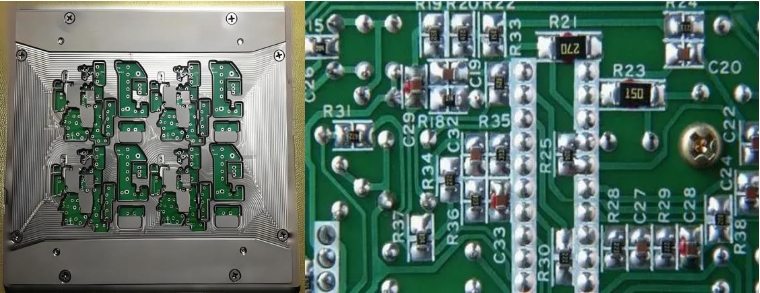

然而,随着我深入查找原因,却发现问题的复杂情况远超我的预计。原来,这些器件的布局不仅受到波峰焊工艺的限制,还受到载具开制阴影效应的影响。器件越高、间距越近,阴影效应就越明显,焊接的难度也就越大。

那要怎么办?SMT工厂的专业人员给出建议:背面DIP Pin脚与SMD零件的距离至少保持3mm以上,且SMD器件越高,与DIP插件焊接面的安全距离就要越大,至少得5mm。这就像是给设计师们划了一条红线,告诉我们在设计电路板的时候,一定要留出足够的空间。

这事也让我陷入深深自责,毕竟作为一个有不少经验的PCB layout工程师,原本应该提前规避这些问题的,但是这次竟然没有发现!我不禁开始怀疑自己的能力……

不过,就在我怀疑人生的时候,一个技术大牛推荐给我了一个工具,说可以帮助我查漏补缺设计问题和提前规避生产隐患,毕竟谁也不能保证自己永远不出错。

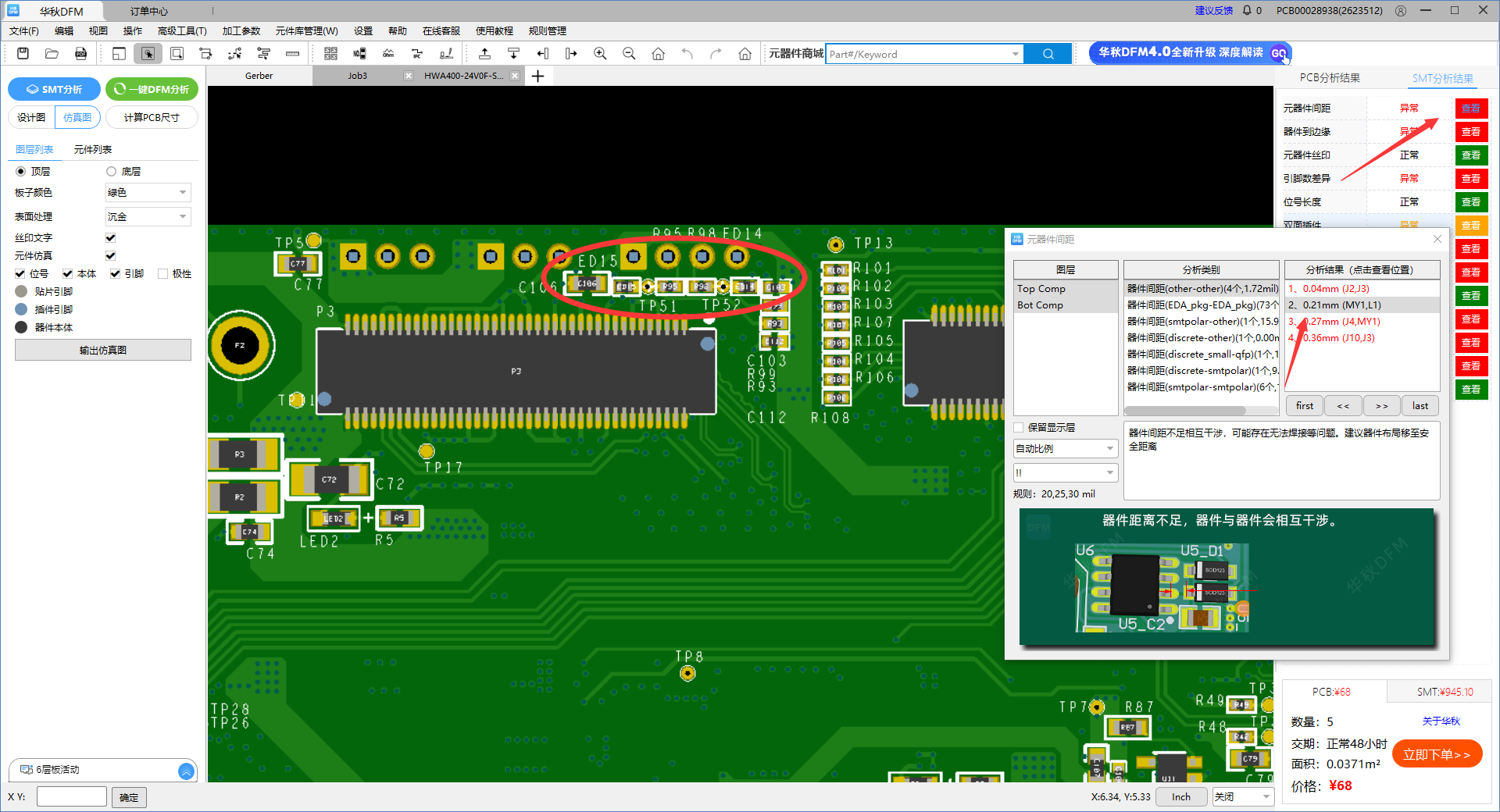

因此我抱着试试的心态,下载了华秋DFM软件,并将设计文件导入其中。软件快速为我分析了元器件布局的间距问题,并指出了潜在的焊接风险。于是在软件的指引下,我开始重新调整元器件的布局。

我增大了DIP Pin脚与SMD零件之间的距离,确保它们之间的安全裕量符合标准。同时,我还考虑了器件的高度和调试的方便性,对布局进行了进一步的优化。每一次调整,都仿佛是在为我的设计注入新的生命力。

经过华秋DFM的指引和我不懈的努力,我终于完成了新的设计,便再次将PCB板送入工厂进行波峰焊,果然焊接效果非常完美,我知道,这款工具我用对了!

同时,我也深刻意识到品质与设计之间的密切关系。一个好的设计不仅能够提高产品的性能和质量,还能够降低生产成本和减少工艺难度。而华秋DFM软件正是我们实现这一目标的得力助手,它能够帮助我们检查元器件布局的间距问题,避免波峰焊连锡和阴影效应的发生,从而确保产品的品质和可靠性。

华秋DFM软件是国内首款免费PCB可制造性和装配分析软件,拥有500万+元件库,可轻松高效完成装配分析。其PCB裸板的分析功能,开发了19大项,52细项检查规则,PCBA组装的分析功能,开发了10大项,234细项检查规则。

基本可涵盖所有可能发生的制造性问题,能帮助设计工程师在生产前检查出可制造性问题,且能够满足工程师需要的多种场景,将产品研制的迭代次数降到最低,减少成本。

华秋DFM软件下载地址(复制到电脑浏览器打开):

审核编辑 黄宇全部0条评论

快来发表一下你的评论吧 !