FPGA和CPLD差异分析(FPGA结构图)

描述

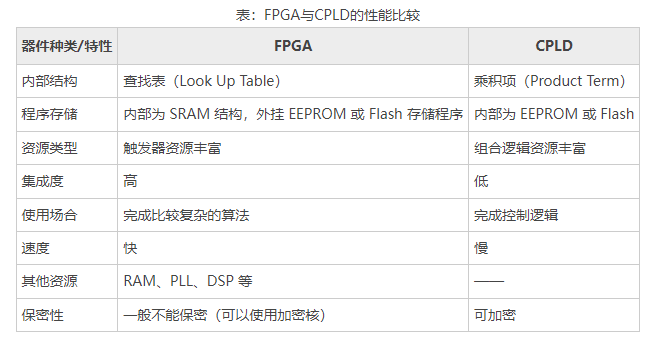

FPGA和CPLD差异分析

FPGA 是一种以数字电路为主的集成芯片,于 1985 年由 Xilinx 创始人之一 Ross Freeman 发明,属于可编程逻辑器件(Programmable Logic Device,PLD)的一种。

FPGA 比 CPLD 早几年问世,与 CPLD 并称为高密度可编程逻辑器件,但它们有着本质的区别。FPGA 芯片的内部架构并没有沿用类似 PLA 的结构,而是采用了逻辑单元阵列(Logic Cell Array,LCA)这样一个概念,改变了以往 PLD 器件大量使用与门、非门的思想,主要使用查找表和寄存器。

除此之外,FPGA 和 CPLD 在资源类型、速度等方面也存在差异,如下表所示。

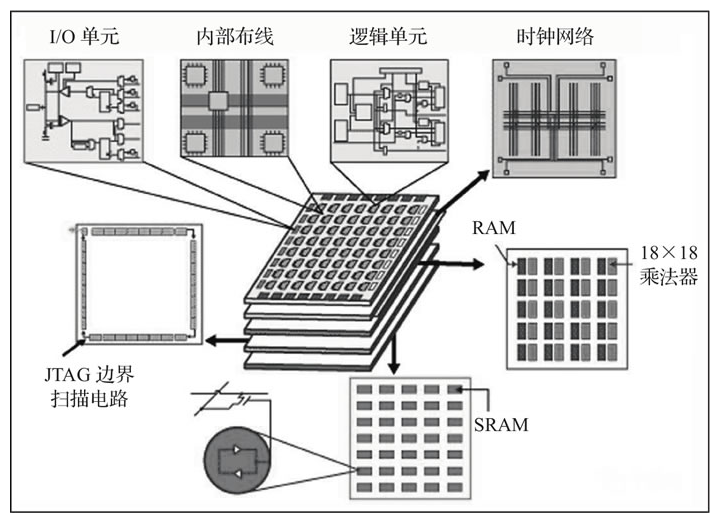

FPGA 的类型从内部实现机理来讲,可以分为基于 SRAM 技术、基于反熔丝技术、基于 EEPROM/Flash 技术。就电路结构来讲,FPGA 可编程是指三个方面的可编程:可编程逻辑块、可编程 I/O、可编程布线资源。可编程逻辑块是 FPGA 可编程的核心,我们上面提到的三种技术也是针对可编程逻辑块的技术。

FPGA 的结构图如图 所示。

FPGA(Field-Programmable Gate Array,现场可编程门阵列)是一种可编程逻辑器件,具有灵活性和可重构性,通常用于数字电路设计和实现。FPGA的基本结构包括以下几个主要部分:

1. 逻辑单元(Logic Blocks):逻辑单元是 FPGA 中的基本逻辑单元,用于实现各种逻辑功能。逻辑单元通常包括查找表(Look-Up Table,LUT)、寄存器、加法器等,可以根据需要配置不同的逻辑功能。

2. 可编程互联网络(Programmable Interconnect):可编程互联网络连接了逻辑单元之间的信号传输路径。通过配置互联网络,可以实现逻辑单元之间的灵活连接,实现各种复杂逻辑功能。

3. 输入/输出模块(IO Blocks):输入/输出模块用于与外部系统进行通信,包括输入输出引脚、时钟管理单元等。IO Blocks 提供了 FPGA 与外部系统进行数据交换的接口。

4. 时钟管理单元(Clock Management):时钟管理单元用于生成各种时钟信号,并对时钟信号进行分频、延迟、对齐等操作,以确保设计的稳定性和性能满足要求。

5. 存储单元(Memory Blocks):存储单元包括片上存储器等,用于存储配置信息、中间结果数据和其他需要的存储内容,提供了额外的存储资源。

6. 配置存储器(Configuration Memory):配置存储器用于存储 FPGA 的配置位流(Configuration Bitstream),即描述 FPGA 逻辑功能和互联的配置信息,通过加载配置位流实现对 FPGA 的编程和配置。

7. 全局时钟网络(Global Clock Network):全局时钟网络为 FPGA 提供整体的时钟分配和管理功能,确保设计中的时序要求得到满足。

fpga主要性能指标

FPGA 的性能指标主要包括以下几个方面:

1. 逻辑容量(Logic Capacity):逻辑容量指的是 FPGA 中可用于实现逻辑功能的逻辑单元数量。它决定了 FPGA 可以实现的复杂度和规模,通常以逻辑单元数或等效门数(Equivalent Logic Cells)来衡量。

2. 时钟频率(Clock Frequency):时钟频率表示 FPGA 设备能够支持的最高工作时钟频率,决定了 FPGA 设备在工作时能够达到的最高速度。时钟频率通常以赫兹(Hz)为单位。

3. 资源利用率(Resource Utilization):资源利用率表示 FPGA 中逻辑单元、存储单元等资源的使用情况,包括逻辑单元使用率、存储块利用率等,用于评估设计在 FPGA 中的资源占用情况。

4. 时序性能(Timing Performance):时序性能包括各种时序相关的指标,如最长组合逻辑延迟、时序收敛等,决定了 FPGA 设备能够满足的时序约束和稳定工作的能力。

5. 功耗(Power Consumption):功耗是衡量 FPGA 设备能耗的重要指标,通常分为静态功耗和动态功耗两部分,影响 FPGA 在实际应用场景中的能耗和热管理需求。

6. 输入/输出资源(IO Resources):输入/输出资源包括 FPGA 设备提供的输入输出引脚数目、支持的通信协议和标准、不同类型的输入输出模式等,影响 FPGA 在与外部系统、芯片或器件连接时的灵活性和适用性。

7. 可编程性(Programmability):可编程性指的是 FPGA 设备在配置、重配置和部署时的灵活性和便利性,包括配置速度、配置接口、支持的配置技术(如SRAM、FLASH等)等。

8. 硬核功能(Hard IP):硬核功能是 FPGA 芯片内置的专用功能模块,如硬核处理器、乘法器、DSP单元等,用于特定应用场景或性能需求,对于特定领域的应用具有重要意义。

审核编辑:黄飞

-

摄像管靶结构图2009-08-02 1313

-

中断结构图2017-03-19 0

-

FPGA与CPLD怎么区分2019-07-01 0

-

控制系统的结构图2021-06-30 0

-

FPGA资料2023-05-30 0

-

化学电源的结构图2009-11-02 607

-

二极管结构图2009-11-11 944

-

机油滤结构图2008-04-12 3688

-

汽车变速箱结构图2008-05-29 19852

-

滚齿机的结构图2009-03-18 7280

-

万能外圆磨床结构图2009-03-18 9943

-

MOS管结构图2009-04-06 4576

-

Tadiran 电池的结构图2009-10-30 1657

-

自控控制:结构图2016-12-30 1362

-

CPLD和FPGA的区别是什么2023-07-03 7054

全部0条评论

快来发表一下你的评论吧 !