平稳地远程传送高速模拟/数字转换数据

模拟技术

描述

在模拟/数字转换中,最理想的是能够利用最少导线便可将数字数据进行下传。有时可以采用输出串行数据的模拟/数字转换器,这当然是解决这个问题的一个办法。但这个解决方案本身存在问题需要解决。可以输出串行数据的模拟/数字转换器往往受制于传统串行总线的内部结构,以至传输速度受到一定的限制。由于这类串行总线经常进行单端信号传输,因此很易产生电磁干扰,影响邻近电路的稳定性。邻近电路产生的共模噪音也会影响串行总线的稳定性,令数据传输出现误码。

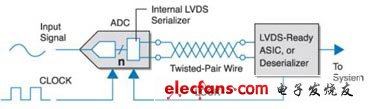

克服这些问题的其中一个办法是采用低电压差分信号 (LVDS) 数据总线。图 1 是其中一种模拟/数字转换器的结构框图,带有LVDS 输出信号,驱动专用集成电路或解串器。

图 1:结构框图

图中的模拟/数字转换器按照 LVDS 信号格式输出串行数据流。接收端则利用可支持 LVDS 的专用集成电路或解串器将 n 位的输出复原。

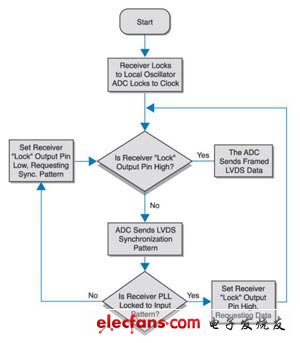

通电启动时,模拟/数字转换器与接收器会进入一个两步骤的启动过程。这个启动过程是指确保每一芯片内不同锁相环路都能实现同步操作的过程。首先,接收器根据振荡器提供的脉冲频率自行锁定。模拟/数字转换器的锁相环路根据 CLKIN 自行锁定。然後,模拟/数字转换器输出一列数据,这列数据的排列方式称为 SYNC 模式,其排列模式如下:任何数目的 "1"之后必定有相同数目的 "0",并按数据输出速度计时。接收器内的锁相环路按照这个 SYNC 模式锁定,并将 "LOCK"信号传送回模拟/数字转换器,通知模拟/数字转换器接收器已锁定,并随时准备接收任何传来的数据。输出数据由以下三个部分组成:数值永远是 "1"的 "起始位"、n 位的数据、以及数值永远是 "0"的 "终止位"。图 2 显示数据传送的大概流程。

图 2:流程

因此这个帧是由 n+2 位的数据所组成,而数据流频率则是 (n+2) x fsample。接收器的锁相环路只要一直处于锁定状态,便可连续接收数据。若锁相环路滑出锁定范围之外,LOCK 线路便会设定为低态,而模拟/数字转换器又会再次收到提供同步操作模式的请求。

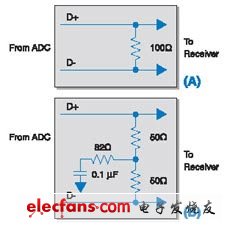

模拟/数字转换器的输出驱动器可提供恒流源,驱动 100W 终端的双绞线、印刷电路上带状线或微带线。图 3 是两种典型置于接收器附近的终端电路。

图3:典型的终端电路

图3 A 是一幅简单的终端配置。模拟/数字转换器的线路终端设有电阻,有助减低任何可能产生的反射。这个电阻也是恒流源电流产生输出信号所需的负载。图 3B 是另一简单的终端配置,依据需要使用共模电阻,以减低电缆上的共模。这个方法较为少用。只要采用差分信号格式,模拟/数字转换器及解串器之间的导线数便可减至最少,并确保产生的磁场紧密局限在传输线路的附近。这样可减低这些线路的电磁干扰,以免影响邻近的电路。

美国国家半导体推出可提供 LVDS 输出的模拟/数字转换器,方便精简系统设计,满足数据总线的严格要求。

-

模拟数字转换器输入接口的设计考虑2010-04-22 0

-

模拟数字转换的数据传输2019-07-12 0

-

采用LVDS的高速模拟数字转换数据2019-07-12 0

-

AD转换模拟信号远程监控系统应用2019-07-16 0

-

如何平稳地远程传送高速模拟/数字转换数据?2021-04-23 0

-

平稳地远程传送高速模拟/数字转换数据,不看肯定后悔2021-06-07 0

-

用单片机实现远程数据传送?2009-05-18 788

-

高速ADC(模拟数字转换器)结构设计技术2011-03-30 695

-

模拟信号AD和DA转换在远程控制中的应用2016-11-16 1046

-

模拟设备高速转换器2022-07-18 225

-

高速数据转换的应用报告2017-05-31 524

-

信号 A/D(模拟转数字)转换及远程传输技术的介绍2017-09-28 843

-

远程高速数据采集及处理系统的设计2017-10-29 725

-

数据通信与网络:数字数据,模拟数据和数字信号间的转换2018-10-21 11034

-

数字转模拟转换以及还原监控技术的应用2020-01-20 2784

全部0条评论

快来发表一下你的评论吧 !