Buck电路EMI高风险区域揭秘

EMC/EMI设计

描述

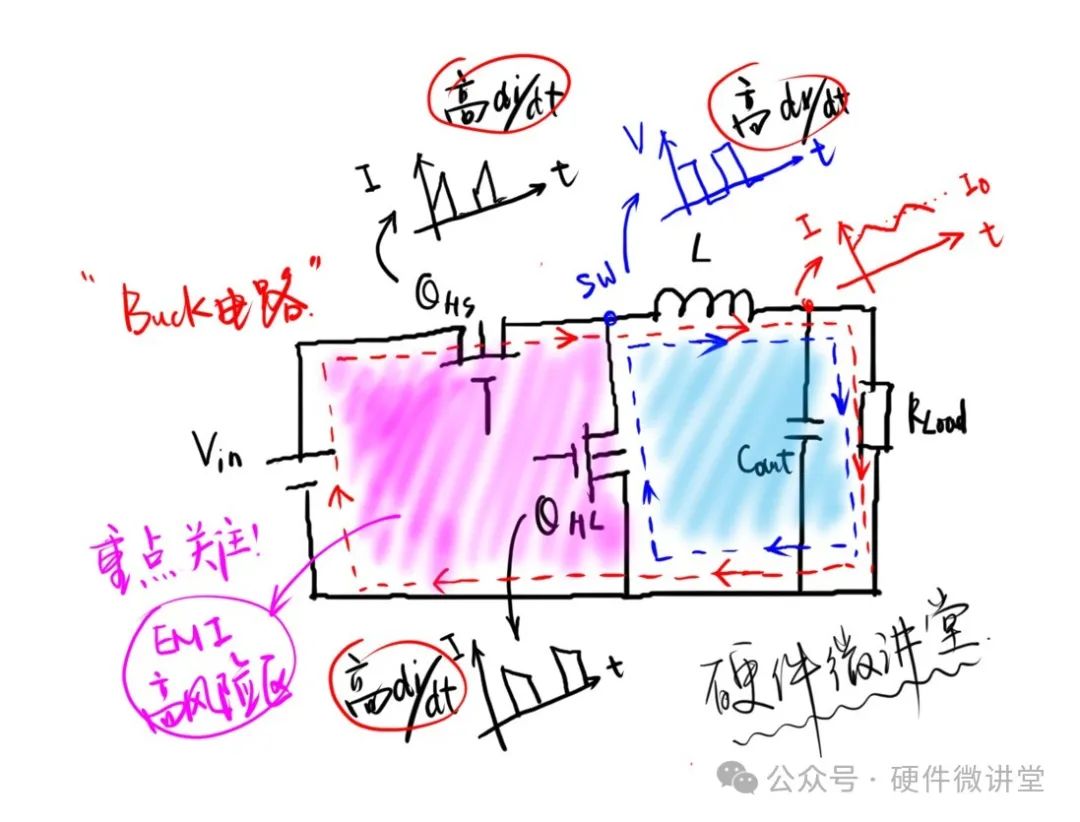

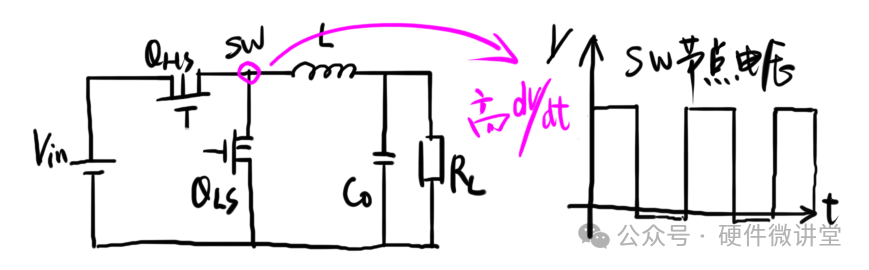

昨天在公众号发了一张关于“Buck电路的EMI高风险区”的手绘图,有小伙伴就私信我让讲讲为啥是高风险区,说明这位同学确实在思考,才有自己的疑惑。既然如此,那我们今天就聊一聊这个问题。

一道问题

照例,先抛出来一道问题:如上图Buck电路所示,同属于Buck电路的电流回路,为什么蓝色区域不是的EMI高风险区?

要搞清楚这个问题,重点在于弄清楚背后的逻辑。在硬件岗位的面试过程中,这个问题大概率是遇不到的,但是这对我们硬件设计和EMC调试却是至关重要。所以,我们有必要细聊一下。

两个电流环

我们重温下到Buck电路的电流环路。

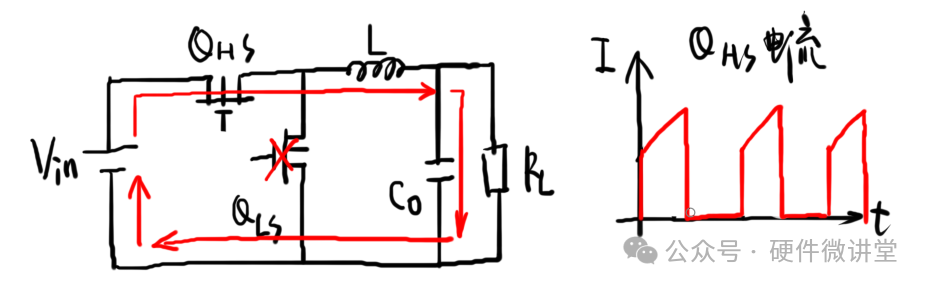

①当上管Q-HS导通,下管Q-LS关断时,电流环路为从Vin正极-->Q-HS-->L-->Cout/Rload-->Vin负极。此时的Q-HS中的电流波形为:

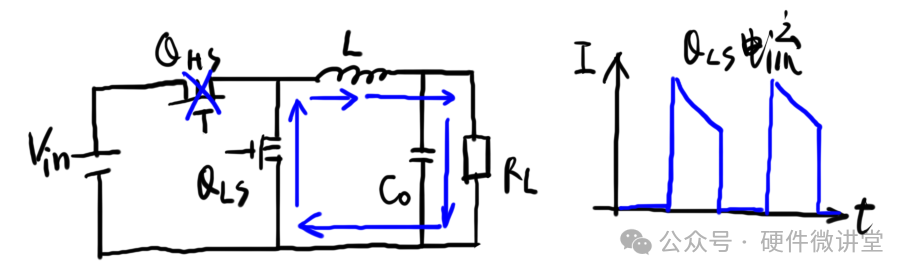

②当上管Q-HS关断,下管Q-LS导通时,电流环路为L-->Cout/Rload-->Q-LS-->L。此时的Q-LS中的电流波形为:

上述两个环路中,Q-HS和Q-LS电流都是不连续的,都存在电流激增和骤降的过程,具有很高的di/dt。波形的上升沿时间Tr越短,变化率越大,蕴含的高次谐波分量就越多。高di/dt,就会产生高次谐波分量。

前方高能!

这些高频分量,结合器件和PCB的寄生电容和分布电感在恰当的时机发生谐振,能量被妥妥地放大Q倍(品质因数),再利用寄生电容提供的传输通路,高频噪声就这样被LISN或其他设备接收到,测试就这样fail了。

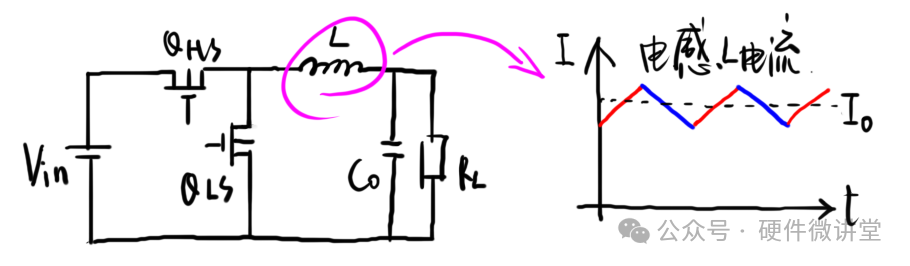

上面说的是紫色区域,我们再看下蓝色区域。由于两个环路都流经了电感L和负载Cout/Rload,电感L中的电流是两个电流环重叠部分的累加,波形为:

从波形上看,电感L中的电流是连续的。虽然电流一直在波动,但是没有出现激增和骤降的突变点,没有高di/dt,则高频分量就少很多。

一个开关节点

上节说了两个电流环中存在高di/dt部分,会存在高频分量。这里再说下电压部分,在紫色区域同样存在高dv/dt。

我们看下SW节点波形,如下图所示:

标准的矩形波,电压波形跳变具有明显的激增和骤降,存在高dv/dt,高频分量饱和程度也是拉满。结合上节提到的寄生电容和分布电感,给共模噪声的产生做了巨大贡献。SW节点电压跳变所产生的高dv/dt就是共模噪声的源头。

上述两点都是在紫色区域发生,而不是在蓝色区域。所以紫色区域至关重要。

你以为这样就结束了?当然不是!

这才是今天要聊的4点中的前2点。这两点在EMC设计中时常被提及的,但是还有两点,也要需要重点考虑,却经常被人遗忘。如果考虑不周,轻则修改电路参数,重则PCB直接要改版。

审核编辑:黄飞

-

手机隐藏着历史上最大单专利侵权诉讼--LDS工艺还具高风险2015-01-05 0

-

BUCK电路2021-07-13 0

-

基于多因素融合的电网高风险设备评估方法2018-02-28 768

-

美国DARPA支持研发微型机器人,用于救灾或在高风险环境执行任务2018-08-30 4560

-

RAIL:风险厌恶模仿学习算法方案2018-11-12 2080

-

高维机器学习防控筛查模型,精准筛查高风险易感人群2020-02-12 2643

-

欧洲态度谨慎 严格监管高风险人工智能技术2020-02-21 407

-

欧洲议员诬称华为中兴“高风险”2020-10-16 1408

-

高风险区域的电线积冰舞动数值模拟研究2021-04-30 386

-

机器视觉检测解决方案:高风险区域防闯检测2024-01-25 263

-

芯盾时代中标山西银行!反欺诈中心精准防控高风险事件2024-04-23 540

全部0条评论

快来发表一下你的评论吧 !