3DES算法的动态加密系统设计原理

描述

引言

目前,应用在工业控制领域的加密算法多以CRC加密或者校验和CHECKSUM加密算法为主,但是此类普通加密算法如果每次发送的控制指令相同,计算出的加密结果也是一样的[1],具有控制数据被破解的风险,增加通信的不安全性,这在一些医疗、金融和汽车电子等特殊领域是不允许的。

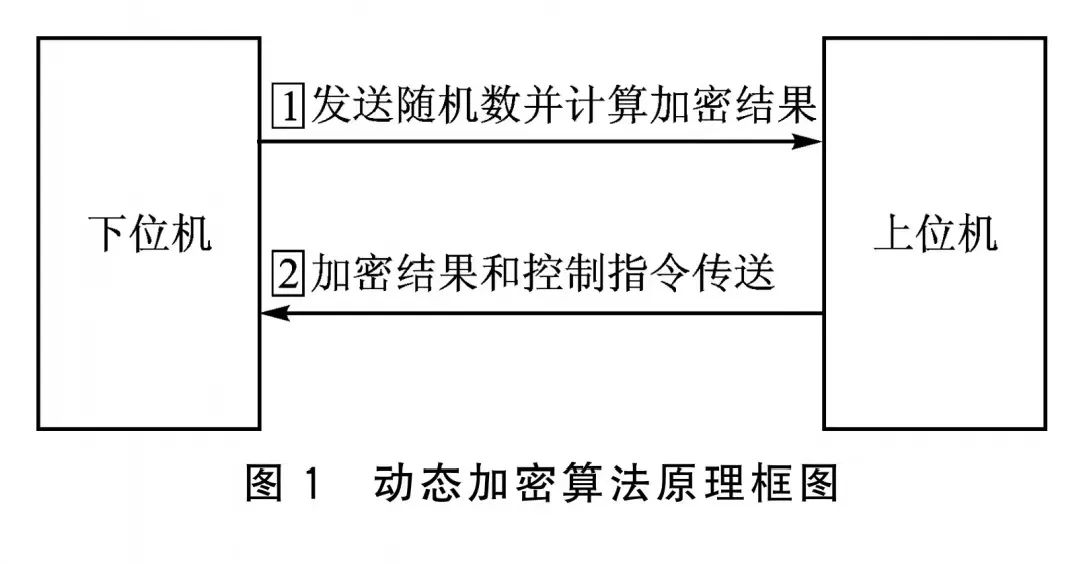

1 动态加密系统原理

本文提出的动态加密系统包括上位机和下位机两部分。图1所示为动态加密算法原理,在工作过程中,首先由下位机周期性发送一包随机种子数据(每次发送数据均变化),并按约定的加密算法进行计算加密,结果记为A,然后上位机接收到此随机种子后按同样的加密算法进行加密,然后将控制指令和加密结果记为B的数据整合为一帧数据后传送给下位机,下位机接收到此控制指令后进行数据解析,若A=B,则执行相应控制指令功能,依此通信过程进行循环。

2 动态加密系统硬件设计

2.1 主控芯片 STM32F103RCT6

本设计中上下位机使用的主控芯片均为STM32F103RCT6,这是一款32位微控制器,最大系统时钟速度可达72 MHz,为快速实时处理复杂加密算法提供了可能性,片内集成FLASH 容量为256 KB,RAM容量为48 KB,具有 UART 及 CAN通信等模块[2],STM32F103RCT6集成的丰富片上外设资源大大简化了设计成本及开发周期。

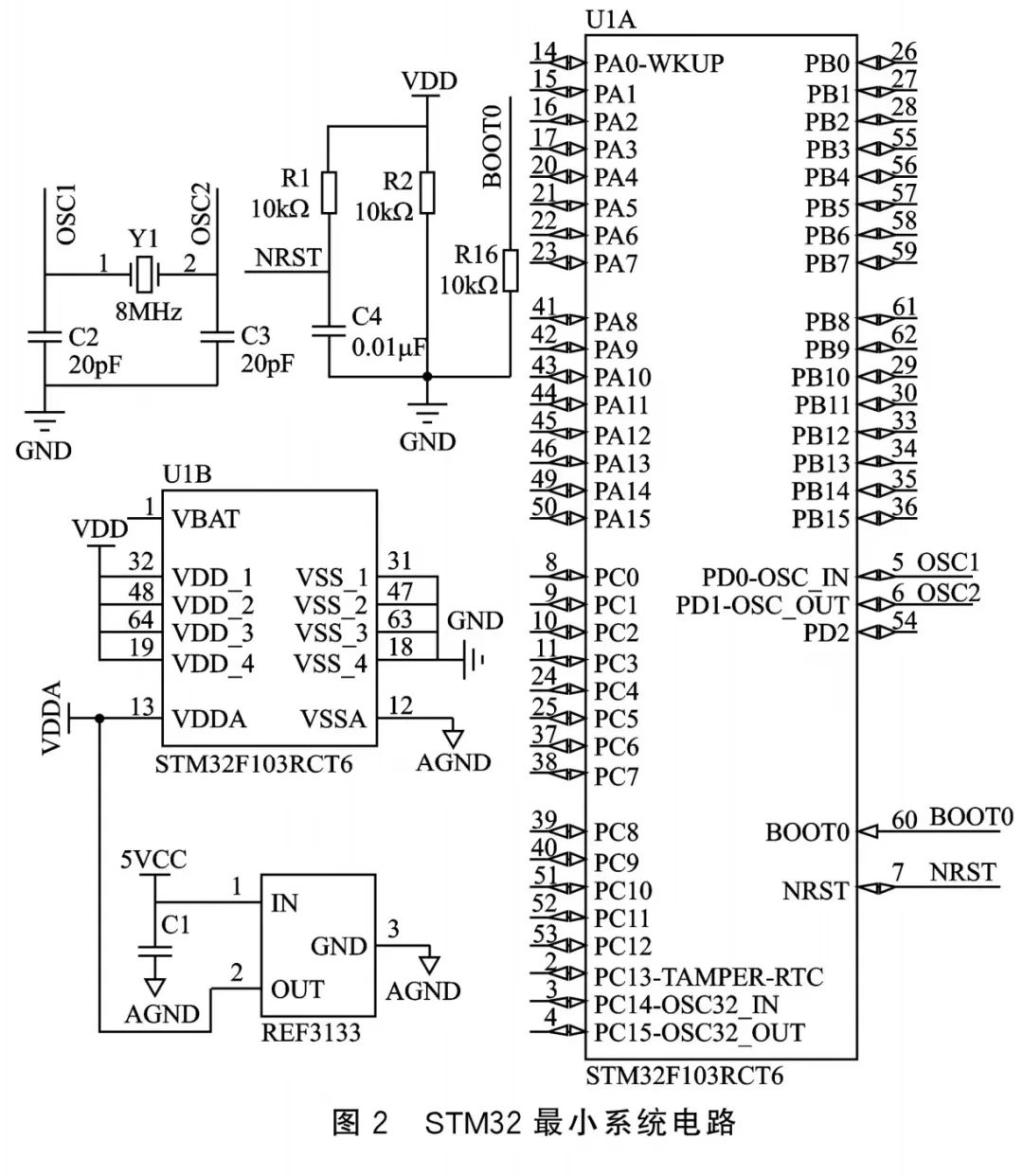

2.2 STM32 最小系统电路设计

STM32 最小系统可以直观地理解为让单片机正常工作的最小电路,图2所示为STM32最小系统构成,包括电源电路、晶振电路、复位电路和启动模式配置等[3]。电源电路经稳压芯片 REF3133将5V电压转换为3.3V提供给 MCU。外部晶振电路类似于"心脏"的功能,为单片机提供精准的时钟频率以保证正常工作。复位电路为单片机提供上电复位功能,利用电容充电不能瞬间突变的特性,即可完成一次单片机上电复位。BOOTO 引脚配置为低电平,以使MCU从用户FLASH存储区启动。

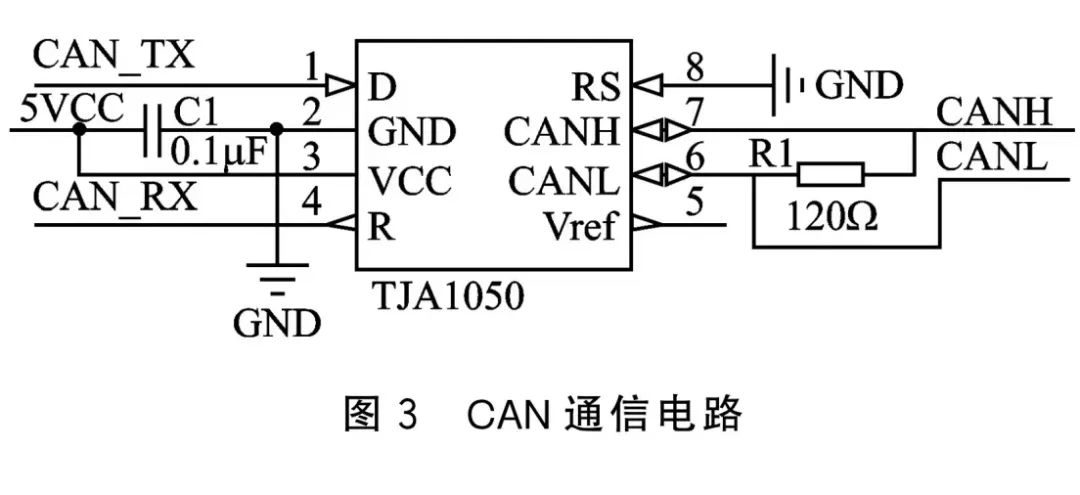

2.3 CAN通信电路设计

使用 Philips 半导体公司的 TJA1050 进行 CAN 通信电路设计,TJA1050是一款高速CAN收发集成芯片,可以提供差分传输总线和差分接收能力,并且全兼容ISO11898 标准[4]。CAN通信电路设计如图3所示,其中控制引脚RS接为低电平以配置为正常高速模式。

3 动态加密系统软件设计

3.1 动态加密算法数据包格式定义

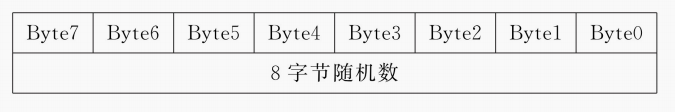

出于通信稳定性考虑,本设计采用CAN通信方式,CAN是Controller Area Network的缩写,是ISO国际标准化的差分传输串口通信协议,具有通信速度快、通信距离远和可靠性高等优点[5],8字节下位机发送数据包格式定义如下:

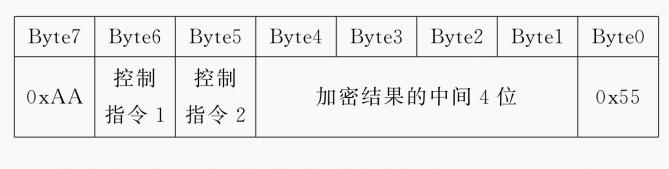

上位机发送8字节数据包格式定义如下:

其中包头和包尾数据分别定义为0xAA和0x55,Byte4~Bytel为应用3DES加密算法计算结果(8字节)的中间4位,并采用小端方式存储,Byte5和Byte6为控制指令模式位,用于控制下位机的工作模式。

3.2 动态加密算法软件设计

DES全称为 Data Encryption Standard,即数据加密标准,是一种使密钥加密的块算法,属于对称加密算法的一种[6]。由于计算机的计算能力不断增强,DES算法的密钥变得较容易被破解,3DES即是在DES算法基础上,通过增加密钥长度对每个数据块应用三次DES加密算法,使得其安全性得到提高[7],若以EK()、DK()分别表示DES的加密和解密函数,P代表明文,C代表密文,则3DES加密算法可以用以下公式表示:

C=EK3(DK2(EK1(P)))

式中,K1、K2、K3表示总密钥(24字节)中的8字节密钥。

本系统为基于3DES算法的动态加密设计,上下位机共同约定的密钥取为24字节的十六进制数:0x2B201E00270401C491EFBD27047002236E710B513460A460。T位机传送8字节随机数种子,其中8字节随机数由C语言自带的srand和rand标准库函数配合使用而产生[8]。上位机在接收到下位机传送来的8字节数据后进行3DES加密算法加密,然后按照数据包的格式回传数据至下位机,下位机接收到此数据后进行数据解析并执行相关指令功能,具体软件设计过程如下:

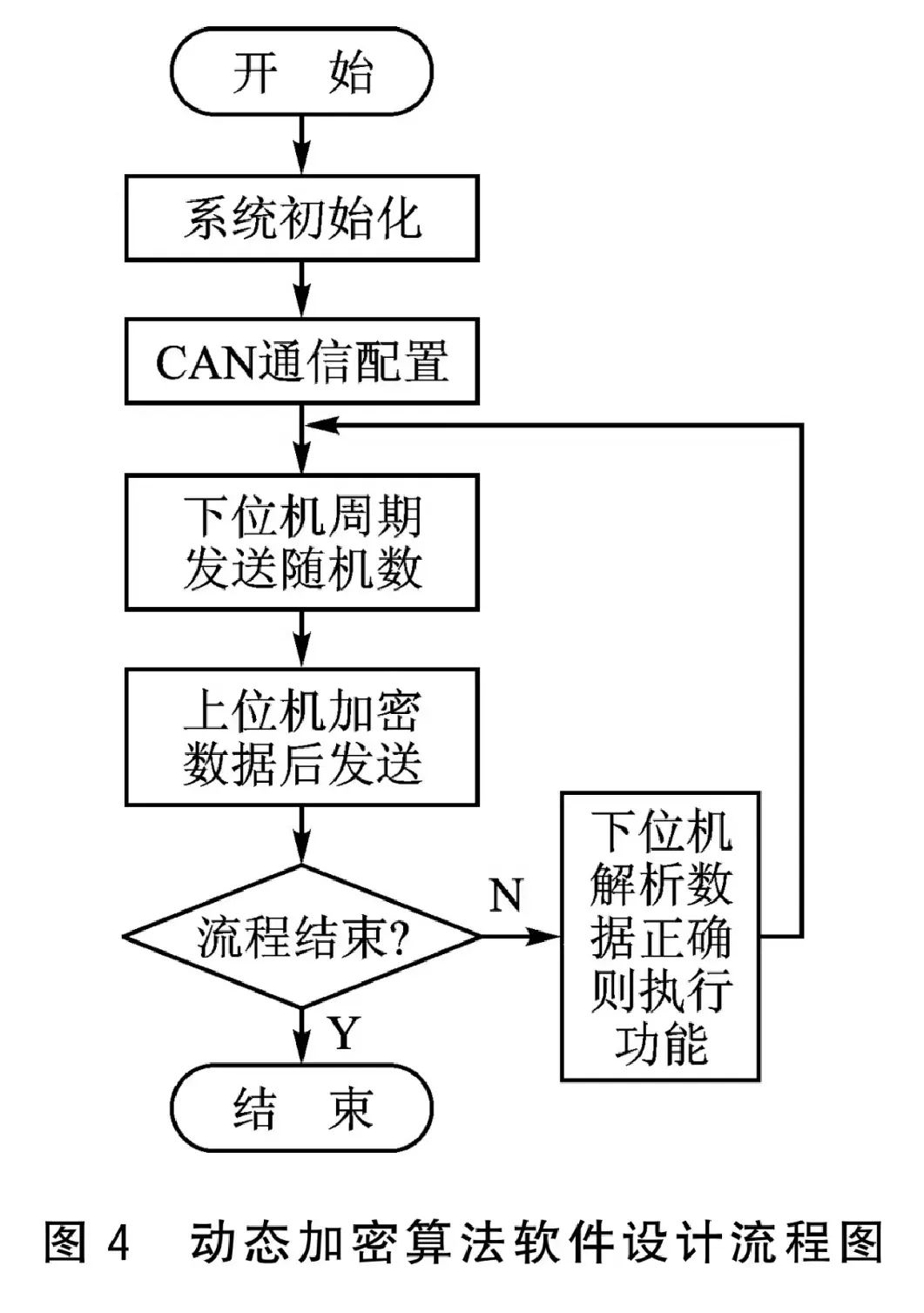

①对MCU系统初始化配置(包括配置系统时钟等),并进行CAN通信正常收发模式和波特率等参数设置。

②由下位机周期性向上位机传送字节随机数,并依据3DES加密算法在同一密钥下计算8字节随机数加密结果,取加密结果的中间4位存入数组中。

③上位机接收到8字节随机数后,按照与下位机同样的计算方法计算此随机数加密结果,并按照数据格式整合数据,然后将此数据发送给下位机。

④下位机接收到上位机传送来的数据后,进行解析并对比上传的加密数据是否与保存在本地的加密数据一致,一致则执行相关控制指令,不一致则不执行相关功能。

⑤按照步骤②~④周期循环执行通信流程。

具体软件设计流程图如图4所示。

结语

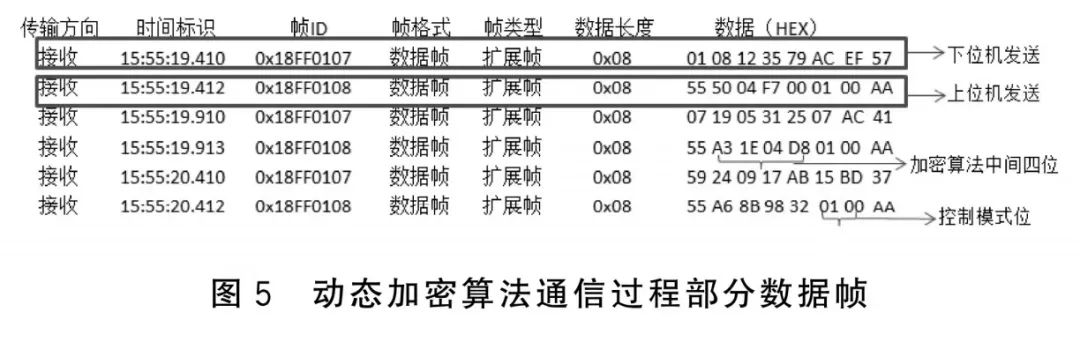

将此通信设计方案应用在某汽车电子产品中,针对此应用系统,设定通信波特率为500 kbps,下位机CAN通信ID设为0x18FF 0107,上位机CAN通信ID设为0x18FF 0108。为了保证通信安全,避免通信内容被破解,需要使下位机周期发送随机数种子时间尽量短暂,本设计定为500 ms。图5所示为上下位机通信过程中应用通信监控软件监控到的部分通信数据帧。

分析图5可知,在足够短的通信周期内,尽管控制模式固定不变,下发与上传的通信数据每次都发生变化,这样就提高了数据通信的安全性,减小了通信数据帧被第三方破解的概率,使得本设计方案具有一定的实用价值。

参考文献

[1]王根义.CRC校验算法的研究与实现[J].电子设计工程,2012(9):1674-6236.

[2]意法半导体公司.STM32F103xC芯片数据手册,2015.

[3]李彬,王朝阳,卜涛,等.基于MSP430F149的最小系统设计[J].国外电子测量技术,2009(12).

[4]郭宽明.CAN总线原理和应用系统设计[M].北京:北京航空航天大学出版社,1996.

[5]徐争颖.CAN总线及其网络系统的实现[J].自动化与仪表,2005(5).

[6]李联.信息安全中的DES加密算法[J].现代电子技术,2005(9).

[7]刘建华,赵小强,李晶.基于ARM的3DES加密算法实现

[J].现代电子技术,2009,32(18):37-39.

[8]王瑞胡,计算机中伪随机数生成及其在VISUAL C++中的实现[J].计算机与信息技术,2005(9):79-80,84

(作者单位:南京先进激光技术研究院,南京210038)

审核编辑:黄飞

-

LKT4201 32位高性能RSA算法加密芯片2014-01-28 0

-

3DES的算法是什么?2019-10-23 0

-

如何去实现DES加密算法?2021-04-26 0

-

如何设计一个基于FPGA的DES加密算法系统2021-04-30 0

-

DES加密算法是什么2021-07-22 0

-

3DES算法密钥长度说明2021-07-22 0

-

基于蔡氏电路和DES的图像加密算法2010-01-07 1007

-

基于状态机和流水线技术的3DES加密算法及其FPGA设计2009-06-20 1073

-

基于FPGA的DES、3DES硬件加密技术2009-07-26 1370

-

一种密钥可配置的DES加密算法的FPGA2009-09-19 962

-

3DES加密算法的原理及FPGA设计实现2017-11-06 978

-

des加密解密算法详解及源码分享2017-12-09 17522

-

3des加密解密详细解释2017-12-09 29941

-

软件加密算法都有哪些,这些算法在哪些方面得到了应用?2018-12-24 7285

-

3DES数据加密算法的原理和使用FPGA设计的详细说明2020-01-16 937

全部0条评论

快来发表一下你的评论吧 !