探索BJT、CMOS、DMOS等半导体工艺技术

模拟技术

描述

随着半导体制程工艺不断取得突破,行业流传着一个被称为“摩尔定律”的著名论断。它是英特尔创始人之一戈登·摩尔在1965年提出的,其核心内容为:集成电路上可以容纳的晶体管数目在大约每经过18个月到24个月便会增加一倍。这一定律不仅仅是对行业发展趋势的一种分析预测,同时也成了半导体制程发展的动力——一切都是为了做出更小尺寸且性能稳定的晶体管。从上世纪五十年代至今大约70年的时间,一共发展出了BJT、MOSFET、CMOS、DMOS以及混合型的BiCMOS和BCD等制程工艺技术。 1. BJT

双极性结型晶体管(bipolar junction transistor, BJT),俗称三极管。晶体管中的电荷流动主要是由于载流子在PN结处的扩散作用和漂移运动,由于同时涉及到电子和空穴两种载流子的流动,因此它被称为双极性器件。

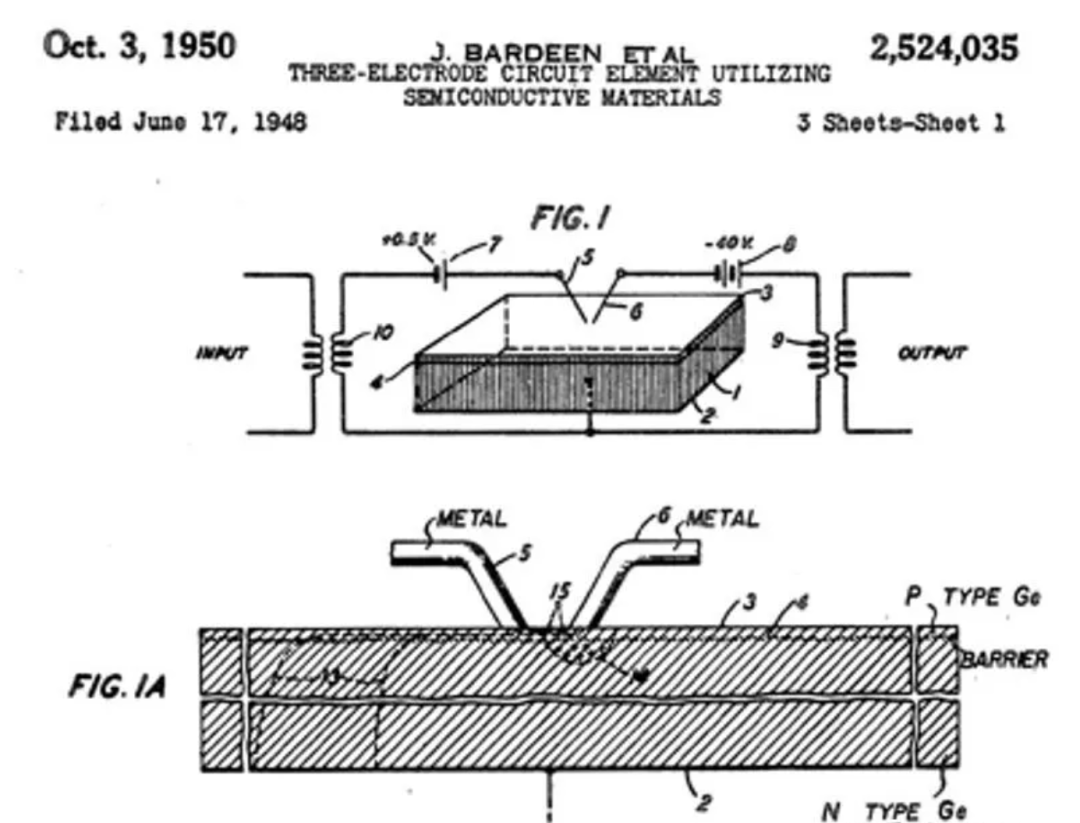

回溯它诞生的历史。由于存在着用固体放大器代替真空三极管这一想法,1945年夏,Shockley提出开展半导体基础研究的建议,1945年下半年,贝尔实验室成立了以Shockley为组长的固体物理学研究小组。在这小组里,不仅有物理学家,也有电路工程师和化学家,包括作为理论物理学家的Bardeen和实验物理学家Brattain。1947年12月,一件被后世认为是里程碑式的事件璀璨地发生了——Bardeen和Brattain成功发明了世界上第一个具有电流放大作用的锗点接触晶体管。

Bardeen和Brattain的第一个点接触式晶体管

而在此后不久,Shockley于1948年发明了双极结型晶体管。他提出了晶体管可以由两个pn结构成,一个正向偏置、另一个反向偏置,并于1948年6月取得了专利。在1949年他把结型晶体管工作的详细理论发表了出来。两年多后贝尔实验室的科学家和工程师开发出流程来实现结型晶体管的量产(1951里程碑),开启了电子技术的新纪元。而为了表彰在晶体管发明上的贡献,肖克利、巴丁和布拉顿共同获得了1956 年诺贝尔物理学奖。

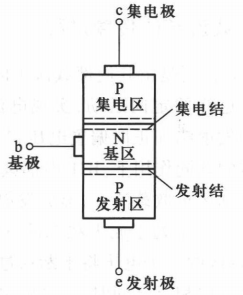

NPN双极结型晶体管的简单结构示意图

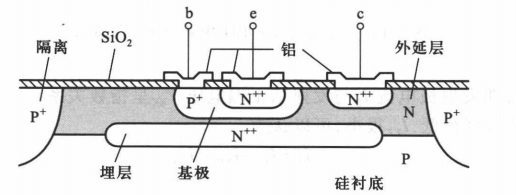

关于双极结型晶体管的结构,常见的BJT有NPN型和PNP型。详细内部结构如下图所示。发射极对应的杂质半导体区域为发射区,该区域掺杂浓度较高;基极对应的杂质半导体区域为基区,该区域宽度很薄,掺杂浓度很低;集电极对应的杂质半导体区域为集电区,该区域面积大,掺杂浓度很低。

BJT技术的优点是高响应速度、高跨导(输入电压变化对应输出电流变化大)、低噪声、高模拟精度、强电流驱动能力;缺点是集成度低(纵向深度无法随横向尺寸缩小)、功耗高。

2. MOS

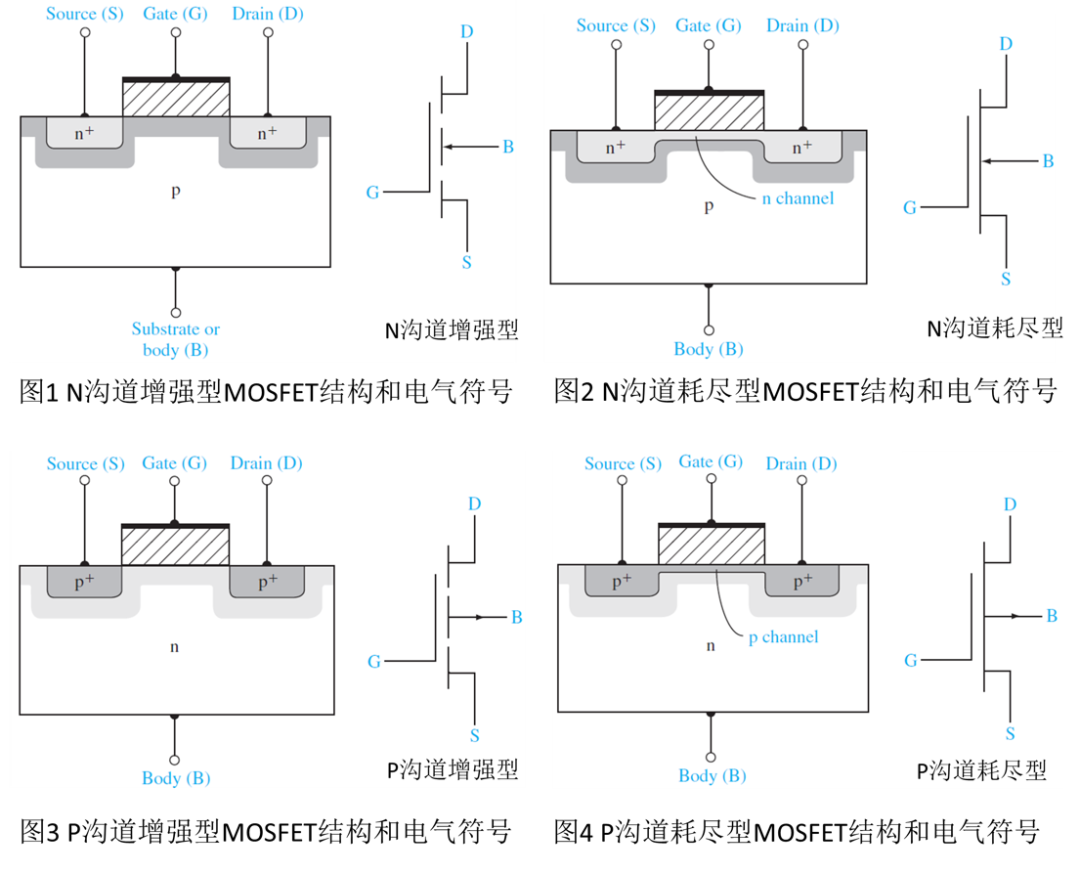

金属氧化物半导体场效应管(Metal Oxide Semiconductor FET),即通过给金属层(M-金属铝)的栅极和隔着氧化层(O-绝缘层SiO2)的源极施加电压,产生电场的效应来控制半导体(S)导电沟道开关的场效应晶体管。由于栅极与源极、栅极与漏极之间均采用SiO2绝缘层隔离,MOSFET因此又被称为绝缘栅型场效应管。1962年由贝尔实验室正式宣布成功开发,这成为半导体发展史上最重要的里程碑之一,为半导体存储器的问世直接奠定了技术基础。 MOSFET按导电沟道类型可分为P沟道和N沟道。按栅极电压幅值可分为:耗尽型-当栅极电压为零时漏源极之间就存在导电沟道;增强型-对于N(P)沟道器件,栅极电压大于(小于)零时才存在导电沟道,功率MOSFET主要是N沟道增强型。  MOS与三极管的主要区别包括但不限于以下几点:

MOS与三极管的主要区别包括但不限于以下几点:

三极管多子和少子同时参与导电,属于双极型器件;而MOS仅靠半导体中的多数载流子导电,又称为单极型晶体管。

三极管属于电流控制型器件,功耗比较高;而MOSFET属于电压控制型器件,功耗小。

三极管导通电阻大,MOS管导通电阻小,只有几百毫欧姆。在现在的用电器件上,一般都用MOS管做开关来用,主要是因为相对于三极管MOS的效率是比较高的。

成本上三极管就比较占优势,mos管相对价格较高。

现在大部分场景下都是用MOS管取代三极管了,只有在一些小功率或者对功耗不敏感的场景下,考虑到价格优势我们才会使用三极管。

3. CMOS

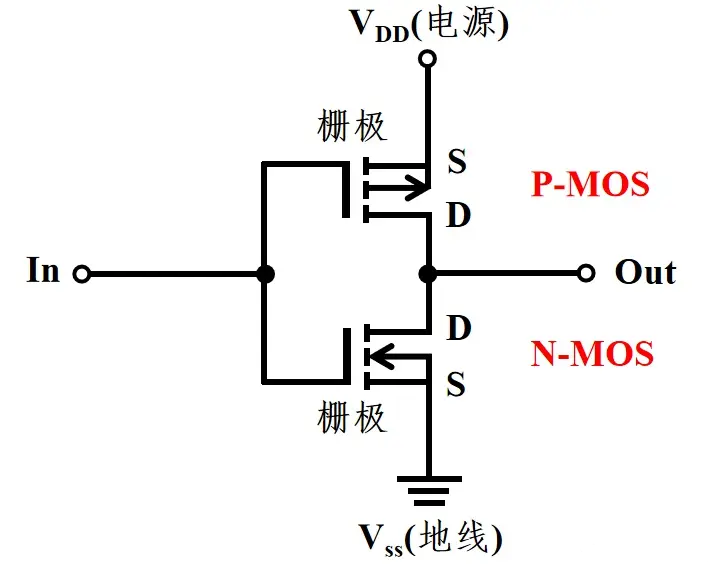

互补型金属氧化物半导体(Complementary Metal Oxide Semiconductor):CMOS技术采用了互补的p型和n型金属氧化物半导体晶体管(MOSFET)来构建电子器件和逻辑电路。下图所示为常见的CMOS反相器,用于“1→0”或“0→1”的转换。

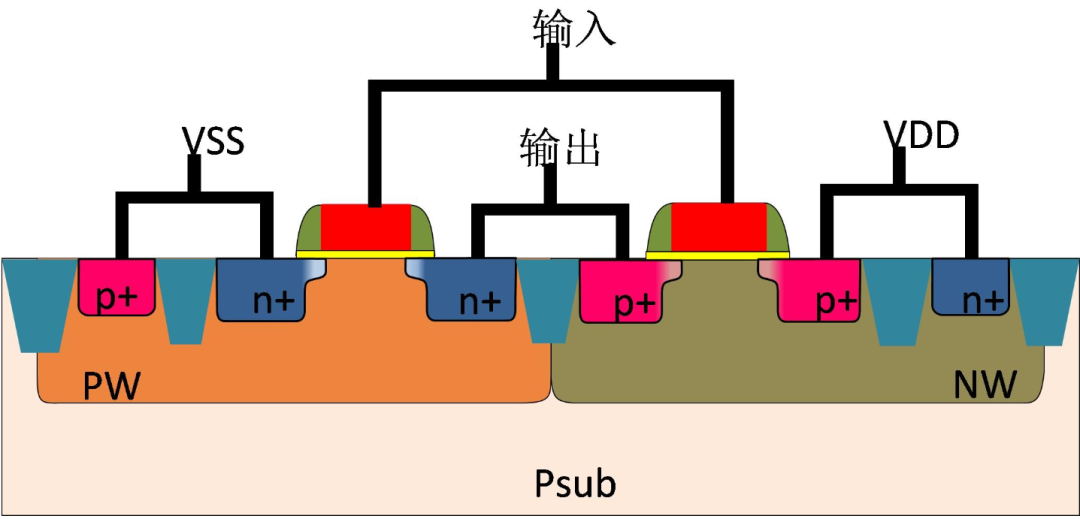

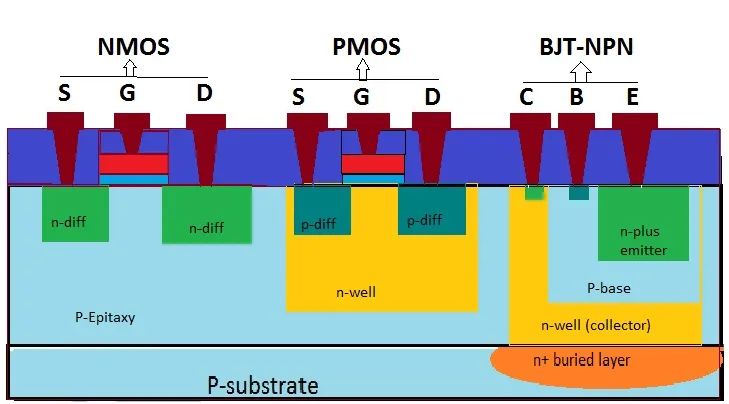

下图为典型的CMOS剖面图。左边是NMS,右边是PMOS,两个MOS的G极连在一起为共连栅极输入,D极连在一起为共连漏极输出。VDD接PMOS的源极,VSS接NMOS的源极。

1963年,仙童半导体公司的Wanlass和Sah发明了CMOS电路。1968年,美国无线电公司(RCA)研发出第一个CMOS集成电路产品,此后CMOS电路获得了巨大的发展。它的优点是功耗低、高集成度(STI/LOCOS工艺可进一步提升集成度);缺点是存在锁效应(MOS管间采用PN结反偏作为隔离,受干扰易形成增强回路烧毁电路)。

4. DMOS

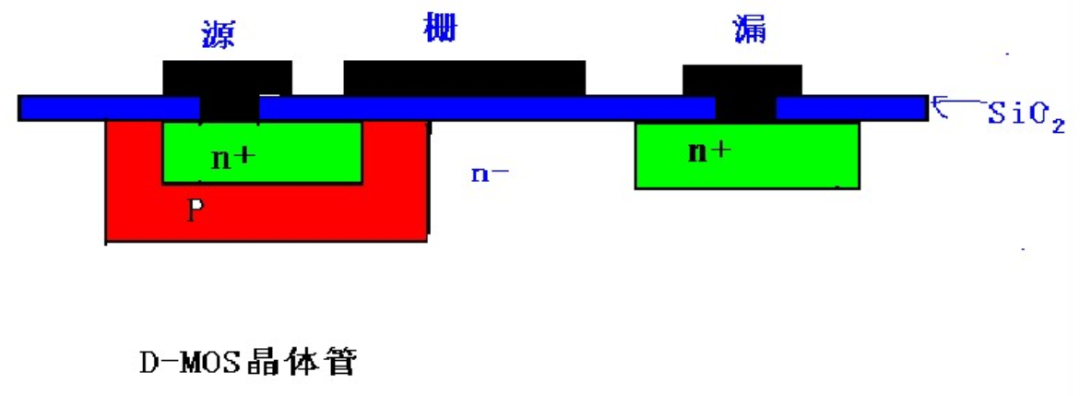

双扩散金属氧化物半导体(Double-Diffused Metal Oxide Semiconductor):与普通MOSFET器件结构类似,也有源、漏、栅等电极,但是漏端击穿电压高。采用了双扩散工艺。

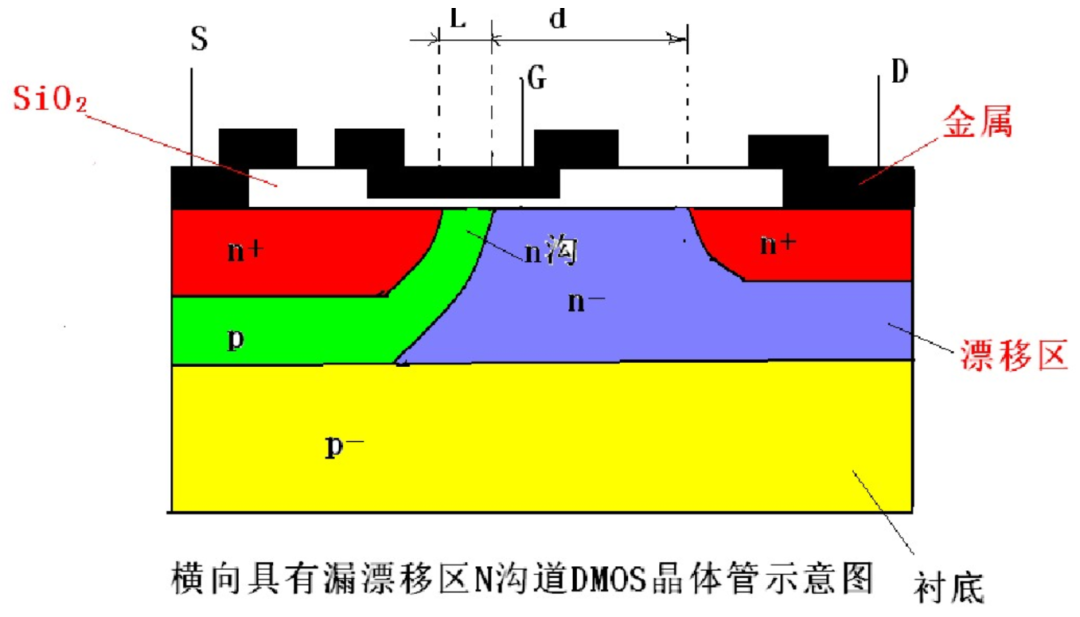

下图展示了标准N沟道DMOS的剖面图,这种类型的DMOS器件通常用于低侧开关应用,其中MOSFET的源极连接到地。此外还有P沟道DMOS,这种类型的DMOS器件通常用于高侧开关应用,其中MOSFET的源极连接到正电压。类似于CMOS,互补DMOS器件在同一芯片上使用N沟道和P沟道MOSFET来提供互补的开关功能。

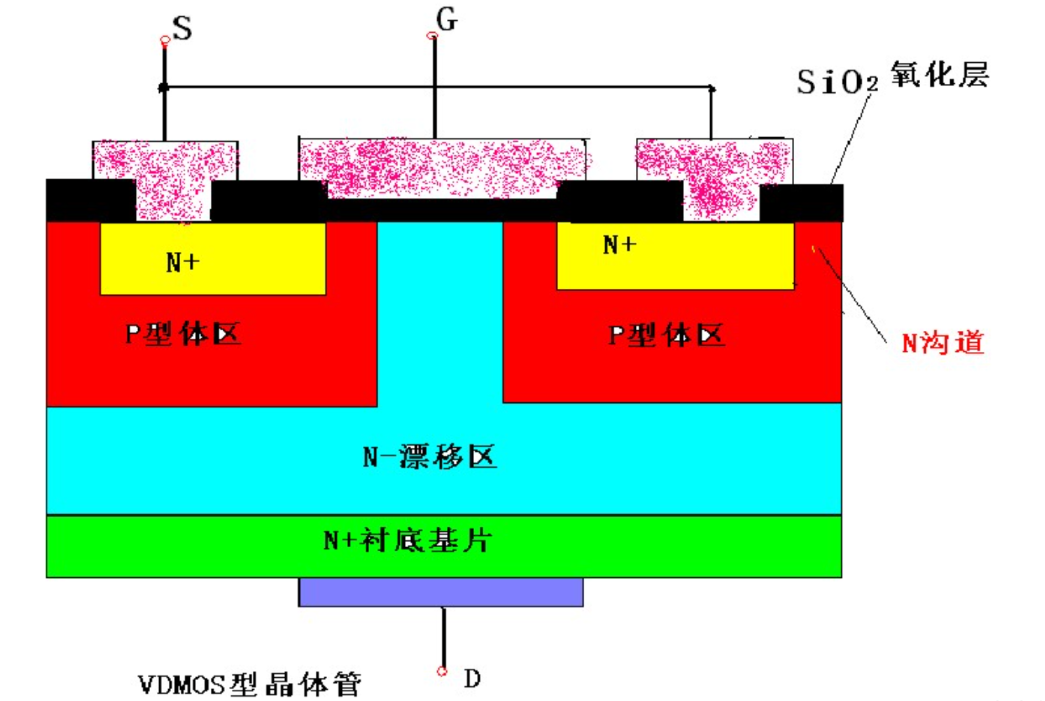

根据沟道的方向,DMOS可以分为两种类型,即垂直双扩散金属氧化物半导体场效应管VDMOS(Vertical Double-Diffused MOSFET)和横向双扩散金属氧化物半导体场效应管LDMOS(Lateral Double-Diffused MOSFET)。

VDMOS器件设计有垂直沟道,与横向DMOS器件相比它具有更高的击穿电压和电流处理能力,但是导通电阻仍然比较大。

LDMOS器件设计有横向沟道,是非对称功率MOSFET器件。与垂直DMOS器件相比,它允许更低的导通电阻和更快的开关速度。

与传统MOSFET相比,DMOS具有更高的导通能力和更低的电阻,因此被广泛应用于高功率电子器件中,例如电源开关、电动工具和电动汽车驱动器等。 5. BiCMOS

Bipolar CMOS, 是CMOS和双极器件同时集成在同一块芯片上的技术,其基本思想是以CMOS器件为主要单元电路,而在要求驱动大电容负载之处加入双极器件或电路。因此BiCMOS电路既具有CMOS电路高集成度、低功耗的优点,又获得了BJT电路高速、强电流驱动能力的优势。

意法半导体的BiCMOS SiGe(硅锗)技术将射频、模拟和数字部分集成在单颗芯片上,能够大幅减少外部元器件的数量,同时优化功耗。

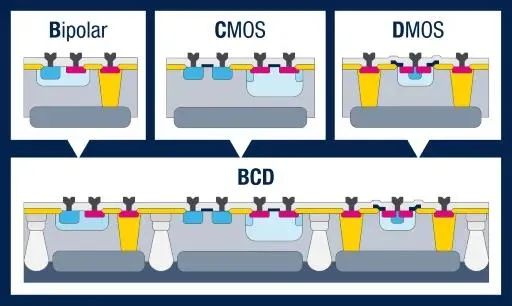

6. BCD

Bipolar-CMOS-DMOS, 这种技术能够在同一芯片上制作双极管Bipolar,CMOS和DMOS器件,称为BCD工艺,1986年由意法半导体(ST)率先研制成功。

Bipolar适用于模拟电路 ,CMOS适用于数字和逻辑电路,DMOS适用于功率和高压器件。BCD则结合了三者的优点。经过持续改进,BCD广泛应用于电源管理、模拟数据采集和功率执行器等领域的产品。从ST官网来目前目前对于BCD来说成熟的工艺还在100nm左右,90nm尚在原型设计中,40nmBCD技术属于其正在开发中的下一代产品。

审核编辑:黄飞

-

有关半导体工艺的问题2009-09-16 0

-

Sic mesfet工艺技术研究与器件研究2009-10-06 0

-

6英寸半导体工艺代工服务2015-01-07 0

-

常见的射频半导体工艺,你知道几种?2016-09-15 0

-

安森美半导体CMOS图像传感器方案2018-11-05 0

-

半导体工艺技术的发展趋势2019-07-05 0

-

为什么说移动终端发展引领了半导体工艺新方向?2019-08-02 0

-

半导体工艺技术的发展趋势是什么?2019-08-20 0

-

2020年半导体制造工艺技术前瞻2020-07-07 0

-

《炬丰科技-半导体工艺》CMOS 单元工艺2021-07-06 0

-

0.16微米CMOS工艺技术2009-12-14 659

-

半导体工艺技术2016-05-26 1014

-

蜂窝趋势引领半导体工艺技术发展方向2017-11-25 483

-

CMOS工艺下的BJT你了解多少?2023-02-02 7068

-

什么是BCD工艺?BCD工艺与CMOS工艺对比2024-03-18 1291

全部0条评论

快来发表一下你的评论吧 !