浅析扇出封装和SiP的RDL改进与工艺流程

描述

如今,再分布层(RDL)在高级封装方案中得到了广泛应用,包括扇出封装、扇出芯片对基板方法、扇出封装对封装、硅光子学和2.5D/3D集成方法。该行业正在接受各种扇出封装,尤其是因为它们提供了设计灵活性、占用空间非常小以及使用RDL与众多I/O进行经济高效的电气连接。

ASE的工程和技术营销高级总监Mark Gerber表示:“目前,人们对利用先进RDL结构的芯片进行异构集成非常感兴趣,这种结构涉及在具有铜柱的基板上进行2.5D扇出。ASE的FOCoS方法就是如此。这种方法的I/O要求从几千到十万以上。”

特别在高性能计算、数据服务器、AI和5G,应用程序鼓励开发将基板与扇出以及嵌入式桥接技术相结合的封装平台,其中大多数过程集成在OSAT中。例如,最近Tech Search International对AMD的高架扇出桥(EFB)和GPU封装(一种衬底上扇出的方法)进行了分析,强调了OSAT在高性能封装中的强大作用。

随着高级封装在OSAT、IDM和晶圆厂进行,高级封装的竞争日趋激烈。对于多芯片集成封装,RDL可以从10µm的线和空间范围扩展到最先进的2µm线和空间(L/S)级别。为了管理复杂的相互作用,先进的建模、材料工程和晶圆工艺正在投入使用,以确保可靠的RDL制造。

高级扇出和异构封装中的问题包括die移位、die翘曲、die间应力以及RDL痕迹断裂的风险。RDL工艺涉及在有机聚酰亚胺(PI)或聚苯并恶唑(PBO)薄膜的窄迹线内电镀铜。新工艺旨在提高RDL附着力,同时减少热循环期间的机械和热应力。

OSAT(包括ASE、Amkor和JCET)提供了许多具有高级RDL流程的封装类型。

Amkor高级封装和技术集成副总裁Mike Kelly表示,4层RDL已经成熟,产量已达到99%。“HBM数据总线需要四层RDL,我们估计在未来几年内,大约85%的封装需求可以通过四层RDL来满足。”

高级封装方向

由于摩尔定律在14nm左右的减速满足了SOC上更大功能的需求,各种先进的封装已经脱颖而出。从那时起,异构集成包变得越来越流行,满足了个人计算应用程序在深度学习、联网和CPU/GPU方面的应用需求。例如,ASE的VIPack平台有六个基于RDL的产品系列,用于满足特定的应用需求,包括扇出式衬底芯片(FOCoS)、FOPoP和FOSiP。

事实上,在最近的IEEE ECTC上,许多芯片制造商展示了新的扇出封装设计。特别是,将已知良好的芯片放置位置保留在工艺后期的芯片封装集成方案正在获得发展势头,这些工艺从载体上的RDL形成开始。

芯片上升

临时键合和释放层,例如Brewer 键合材料,可以在载体上进行RDL处理,然后进行激光释放步骤。这也称为芯片后扇出流程,可实现高产量和低总体成本,同时确保在已知良好的RDL上放置已知良好的die。

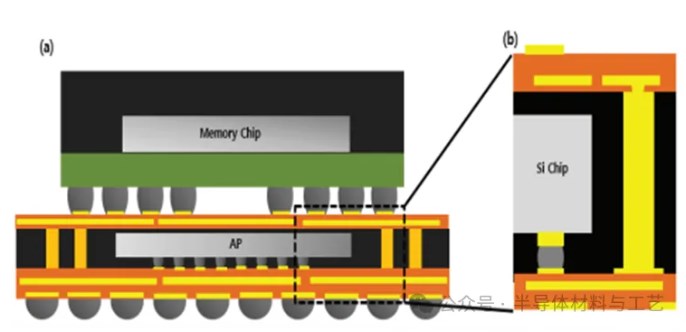

三星的Taewon Yoo及其同事在ECTC上提出了一种芯片级FOWLP方案,并将结果直接与等效的基板倒装芯片BGA和插入器封装方法进行了比较。FOWLP工艺使用逻辑器件配置上的内存,实现了良好的电气和热性能,“当RDL直接在I/O焊盘上形成时,厚度通常是基板尺寸的一半。”三星指出,该设计比FCBGA中的电路信号路径更短,最终封装厚度为0.26mm。

图1:相对于FCBGA和PoP架构,芯片最后扇出WLP将封装厚度减少了50%。资料来源:三星

在三星的设计中(见图1),RDL构建在一个玻璃晶圆载体上。这种方法还利用了连接正面和背面RDL的穿模铜柱。RDL的特点是在7µm聚酰亚胺空间中有8µm的电镀铜线。三星电子的Taewon Yoo表示:“这种RDL的厚度通常是基板尺寸的一半,并且形成于I/O焊盘的顶部。” 在这种情况下,扇出方法也比PoP方法更有效地散热。工程师们通过修改顶部钝化层下的RDL设计,缓解了集中在焊球下方的应力。

放置精度和die移动是多芯片封装中众所周知的问题。RDL第一个扇出方法可能会有所帮助。正如ECTC演讲中所强调的那样,“对于改进die移位、精细间距要求、工艺优化和已知良好die(KGD)成品率管理的战略,芯片后扇出流程是有效降低成本的候选方案。”ASE的Jen Hsien Wong和同事为50 x 35mm FO die中的8个芯片优化了芯片封装策略,该die由环氧树脂模塑化合物和具有不同轨迹布局的FOCoS包围。热机械建模将所有材料(硅die、RDL、散热片)的CTE视为温度的函数,以及材料模量。有限元模型计算了CTE失配倾向较高的die间隙区域的应力。热分散器提供散热,但也有助于最小化包装翘曲。最终优化将die间隙区域下的微量应力降低34%,并产生了最佳布局。

该研究强调,模拟室温和高温(260°C)之间的封装翘曲行为,可以实现卓越的散热片设计。该方法为使用芯片封装FOCoS的多芯片封装的翘曲控制和未来热机械优化提供了指导。

RDL工艺流程

EV集团业务发展总监托马斯·乌尔曼(Thomas Uhrmann)表示,使FOWLP走在前列的一项关键技术是低温可成像聚酰亚胺的配方,例如富士胶片的LTC系列。其他聚酰亚胺制造商包括Asahi和Hitachi Dupont。最新的工艺是使用聚酰亚胺(PI)或聚苯并恶唑(PBO)薄膜的真空固化,以提供优异的介电薄膜性能,同时加快大批量生产的固化时间。

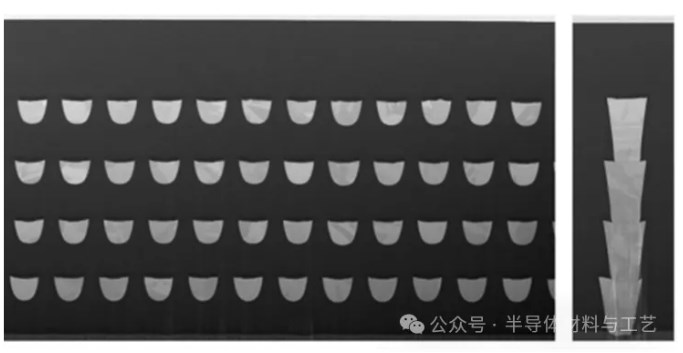

RDL流程通常涉及半加性工艺,包括介电沉积、湿法或干法蚀刻、阻挡层和籽晶层沉积以及镀铜。扇出WLP,但对于高密度RDL,双镶嵌工艺越来越具有吸引力,以避免与半加性工艺相关的种子层咬边和侧壁蚀刻漏洞问题。通过在无刻蚀步骤的介质层中嵌入迹线,并采用双镶嵌工艺,消除了铜崩溃风险,新的RDL提高了互连可靠性。在新工艺中,使用一个光刻曝光步骤在有机介质中形成通孔和RDL图案。新的4层RDL(见图2)具有2/1µm的线条/空间。为改善介质厚度均匀性而进行的工艺改进能够减少晶圆边缘残留的厚铜引起的短路。

图2 2/1µm L/S和2µm经堆栈的4层RDL 来源:Amkor

结论

RDL过程相对简单,但一旦与涉及多个芯片的复杂过程集成,就需要进行重大优化,以管理这些封装系统中的CTE不匹配、电气、热和机械行为。

审核编辑:刘清

-

封装工艺流程--芯片互连技术2022-12-05 1788

-

PCB工艺流程详解2013-05-22 0

-

板上芯片封装的焊接方法及工艺流程简述2012-08-20 0

-

SMT贴装基本工艺流程2018-08-31 0

-

晶体管管芯的工艺流程?2019-05-26 0

-

样板贴片的工艺流程是什么2021-04-26 0

-

芯片封装工艺流程-芯片封装工艺流程图2008-05-26 7450

-

ic封装工艺流程2010-07-18 3015

-

LAMP-LED封装工艺流程图2010-03-29 3577

-

IC封装测试工艺流程2020-10-10 7731

-

集成电路芯片封装工艺流程2021-07-28 12272

-

芯片封装工艺流程是什么2021-08-09 65807

-

扇出式封装的工艺流程2021-10-12 10396

-

扇出型圆片级封装工艺流程与技术2023-05-08 1362

-

先进高性能计算芯片中的扇出式封装2023-05-19 872

全部0条评论

快来发表一下你的评论吧 !