美成功破解下一代多核微处理器储存瓶颈

嵌入式新闻

描述

直写高速缓存(direct-write cache memories)是今日微处理器的支柱,因为它们能以一种对应用程序透明化的模式降低存储延迟。不过,先进处理器的设计工程师正致力于针对下一代多核处理器,转向采用软件管理缓存(software-managed scratchpad)与信息传递(message-passing)技术,例如由IBM、Toshiba与Sony所开发、应用于PlayStation 3游戏机的Cell宽频引擎架构(Broadband Engine Architecture,CBEA)。

遗憾的是,软件管理暂存器与信息传递技术对应用程序设计师来说是额外负担,并因此意味着微处理器演进过程中的退步。而日前美国半导体技术研发联盟机构Semiconductor Research Corp(SRC)声称,该机构已经解决了新一代处理器的高速缓存扩充问题,可让处理器最多拥有512颗核心;SRC是利用分级硬件一致性(hierarchical hardware coherence)方案,让今日的多层级缓存在自然演变的同时,又保有对应用程序的透明度。

“设计工程师一直对未来多核微处理器的储存问题感到忧心,并致力于透过缓存与信息传递技术来达成软件的一致性;”参与上述研究专案的美国杜克大学(Duke University)教授Dan Sorin表示:“但这种方法需要程序设计师进行数据移动管理,这并不是产业界应该走的方向。”Sorin参与的SRC赞助研究,是与美国宾州大学(University of Pennsylvania)教授Milo Martin与威斯康辛大学(University of Wisconsin)教授Mark Hill合作进行。

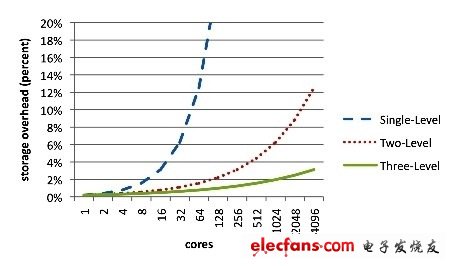

蓝色线所代表的单阶层平行目录缓存,在处理器核心扩充到超过32颗的时候会发生无法接受储存的现象,但具备分级目录的双层(红色线)与三层(绿色线)缓存则能扩充支持到512颗核心,而且仅须增加2~4%的储存空间

研究人员提出一种分级硬件一致性技术,声称可让处理器闪存以其核心数量的平方根(square root)进行扩充,而且仅需为处理器添加2%的储存空间,就可支持最多512颗核心。也就是说,尽管核心数量增加,数据流量、储存空间与功耗的增加幅度缓慢,让未来的处理器能继续使用具备硬件一致性、对应用程序透明化的直写高速缓存。

“这样的结果将藉由对设计工程师保证缓存一致性不会遭遇限制,而改变电脑架构的发展方向;”SRC的IC与系统科学部门总监David Yeh表示:“我们现在知道,还有方法可以绕过限制,因此设计工程师可以不用再担心。而且所有的技术都是现成的,不需要新发明的方法,只要聪明地运用那些现有技术就可以。”

值得一提的是,目前的直写硬件一致性架构,能藉由以分级目录增强的共享缓存与明确的快取清除通知(cache eviction notifications)之协同组合而进化,在处理器核心数量增加的同时保持流量、储存、延迟与功耗能在控制之下。SRC指出,未来的大量并行多核处理器发展蓝图将因此而清晰且畅通无阻。

-

[3.10.1]--3.10微处理器概述学习电子知识 2023-02-17

-

Supermicro将在 CES上发布下一代单路平台2011-01-05 0

-

多核处理器设计九大要素2011-04-13 0

-

下一代定位与导航系统2012-08-18 0

-

多核处理器的优点2019-06-20 0

-

为什么说射频前端的一体化设计决定下一代移动设备?2019-08-01 0

-

如何建设下一代蜂窝网络?2019-08-19 0

-

下一代SONET SDH设备2019-09-05 0

-

测试下一代核心路由器性能2019-09-19 0

-

单片光学实现下一代设计2019-09-20 0

-

ARM9E系列微处理器处理高速数字信号处理效果如何?2019-09-26 0

-

ARM10E系列微处理器主要可以应用在哪些领域?2019-09-26 0

-

STM32MP1多核微处理器有哪些性能呢2021-12-15 0

-

在 TI 高性能的 DSP中,多核适应下一代处理器领域的研究和探索2018-06-13 3730

-

研究和探索下一代处理器领域的多核技术2018-06-12 3435

全部0条评论

快来发表一下你的评论吧 !