PFC频繁炸机的驱动电路原理分析

电源/新能源

描述

为了进一步降低成本,H桥PFC由原来的光耦隔离驱动电路改为采用高压浮驱芯片的电路,频繁出现PFC炸机的情况,对此,对这个驱动电路进行分析,同时寻找解决措施。

1. 问题的现象描述:

为了进一步降低成本,H桥PFC由原来的光耦隔离驱动电路改为采用高压浮驱芯片的电路。

1. 用IRS21850浮驱芯片,在起机的过程中会出现异常的高电平,有一定概率导致PFC炸机。

2. 用FAN73711浮驱芯片,在起机时没有发现异常的高电平现象,基本能够正常工作,但是在更加恶劣的工作状态下会发生炸机,比如在源跳变时会发生PFC炸机。

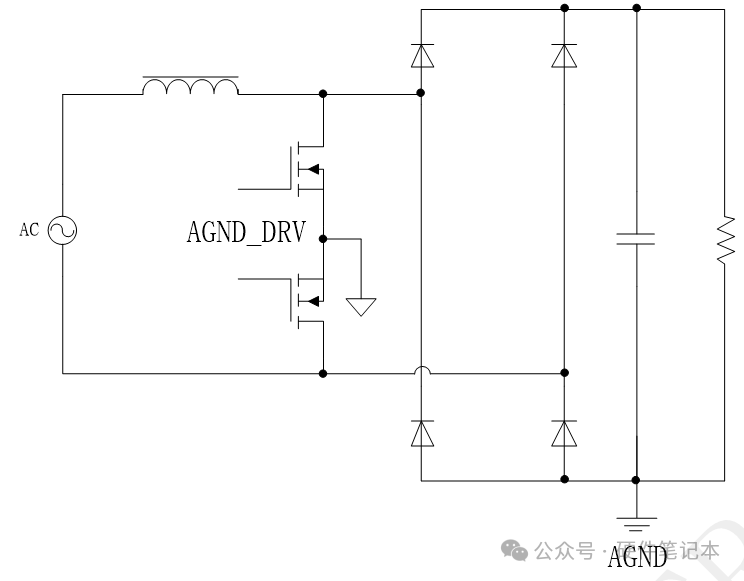

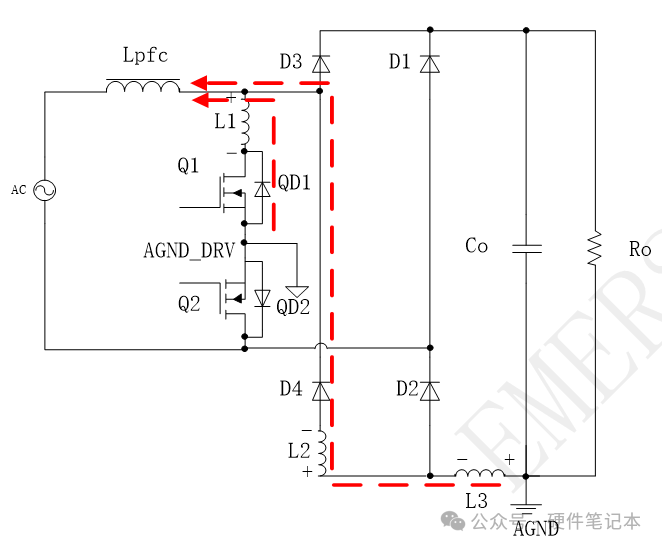

图1 PFC主电路图

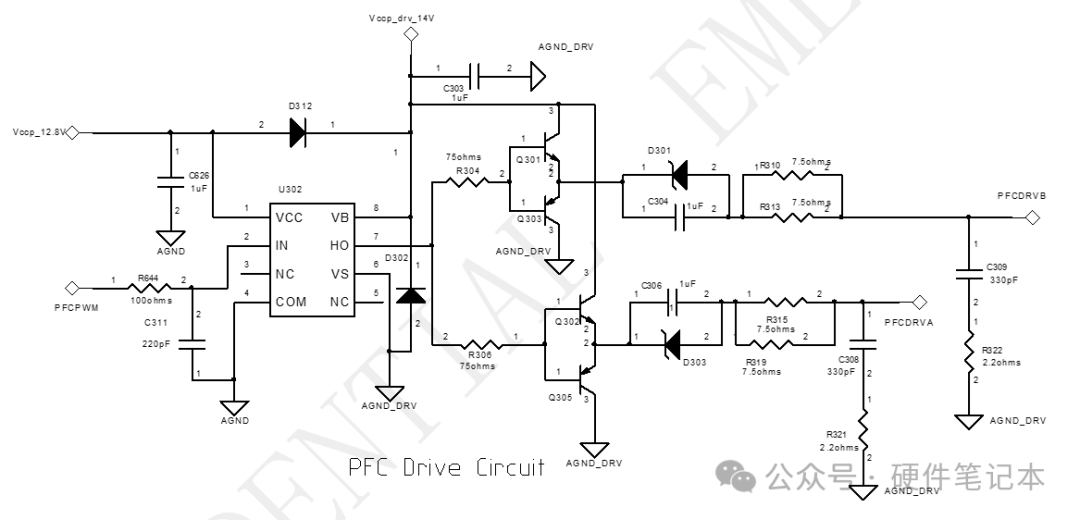

图2 PFC驱动电路

1.1. 问题1原因分析

采用IRS21850浮驱芯片,起机时出现异常高电平现象。

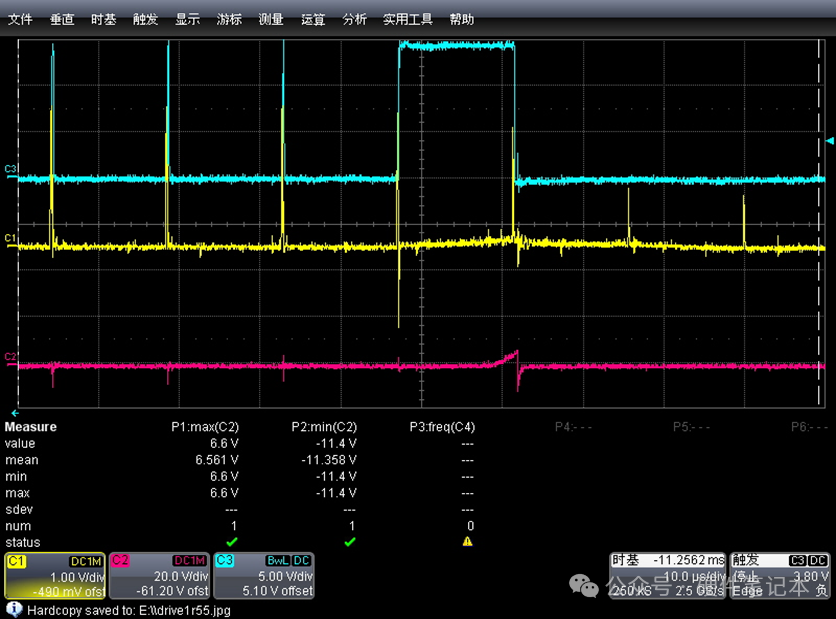

图3 通道1 为驱动芯片输入(PIN2)波形,通道2为VS-COM的电压波形,通道3为驱动芯片输出(PIN7)的电压波形。

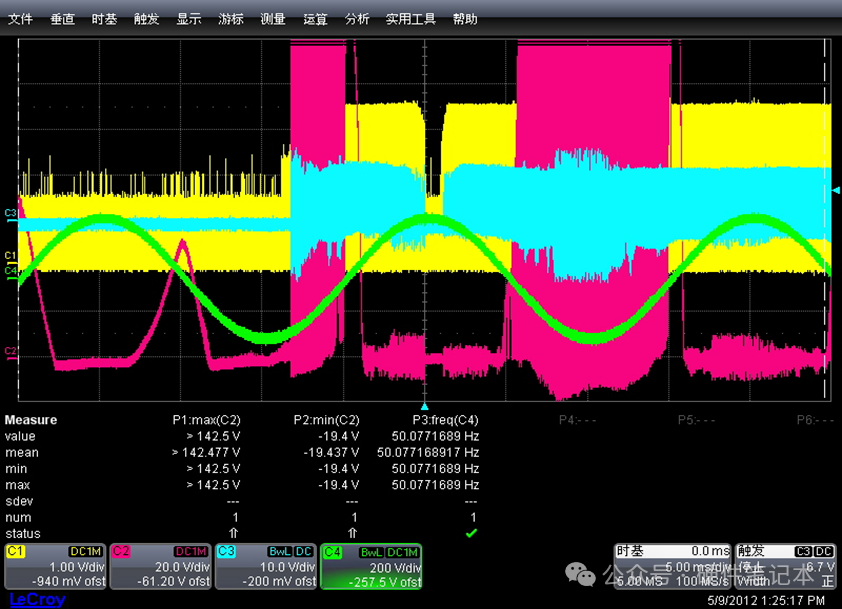

图4 通道1 为驱动芯片输入(PIN2)波形,通道2为VS-COM的电压波形,通道3为驱动芯片输出(PIN7)的电压波形,通道4为输入电压波形。

我们做了以下实验:

这个异常的高电平现象总是出现在交流输入的正半波的最高值,并且只出现一次,起机运行后一直不会出现这个现象。

换成FAN73711后没有出现这个现象。

170V以下空载起机不会出现这个问题,180V以上起机会出现这个现象。(感谢关注公众号:硬件笔记本)

当170V以下空载起机,其占空比相对较大,180V以上起机占空比相对较小。

驱动做RC削波处理后,空载起机一直没有出现这个现象。

驱动做RC削波处理后,其占空比会相对较大。

用二极管钳位或者二极管串联稳压管钳位的方式,可以消除这个现象。

后来跟IR公司的FAE沟通后,他们解释为这种浮驱芯片有最小脉宽的要求,当输入脉宽低到一定程度,会导致芯片内部丢失关断信号,导致一直处于高电平状态,这是由于芯片内部有消隐电路,脉宽太小,会导致上升沿或下降沿信号丢失,IR的FAE推荐最小脉宽最好高于400ns.

因此这颗芯片不适合在我们这种电路上使用。

1.1. 问题2原因分析

问题2:用FAN73711浮驱芯片,在起机时没有发现异常的高电平现象,基本能够正常工作,但是在更加恶劣的工作状态下会发生炸机,比如在源跳变时会发生PFC炸机。

经过与Fairchild公司的FAE沟通,他们认为这个芯片没有窄脉宽的问题。FAN73611也有跟IRS21850的问题,但是FAN73711在窄脉宽的问题上做了改进,因此不会出现跟IRS21850类似的窄脉宽问题。(感谢关注公众号:硬件笔记本)

排除了窄脉宽引起的问题,那么源跳变时为什么PFC电路会发生炸机的问题呢?

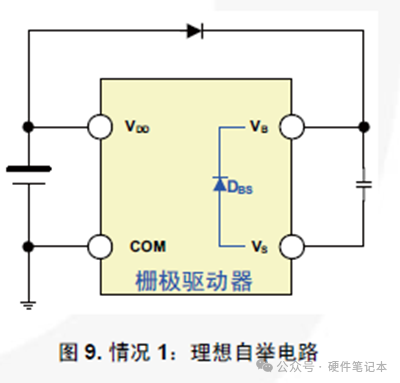

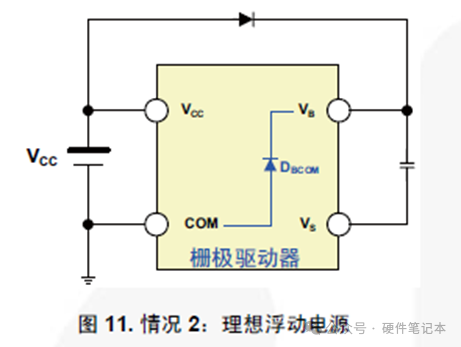

查阅Fairchild公司关于高压浮驱芯片的用户手册,在以下两个情况下,芯片内部寄生二极管D_BS或D_BCOM前向或反向导通,会导致寄生SCR闭锁,造成输出异常。

Fairchild高压浮驱芯片设计和使用准则:

产生PFC炸机的原因很可能是VS-COM出现较高的负压的现象,导致芯片内部寄生二极管导通,芯片出现闭锁效应,出现长时间高电平现象,PFC炸机。

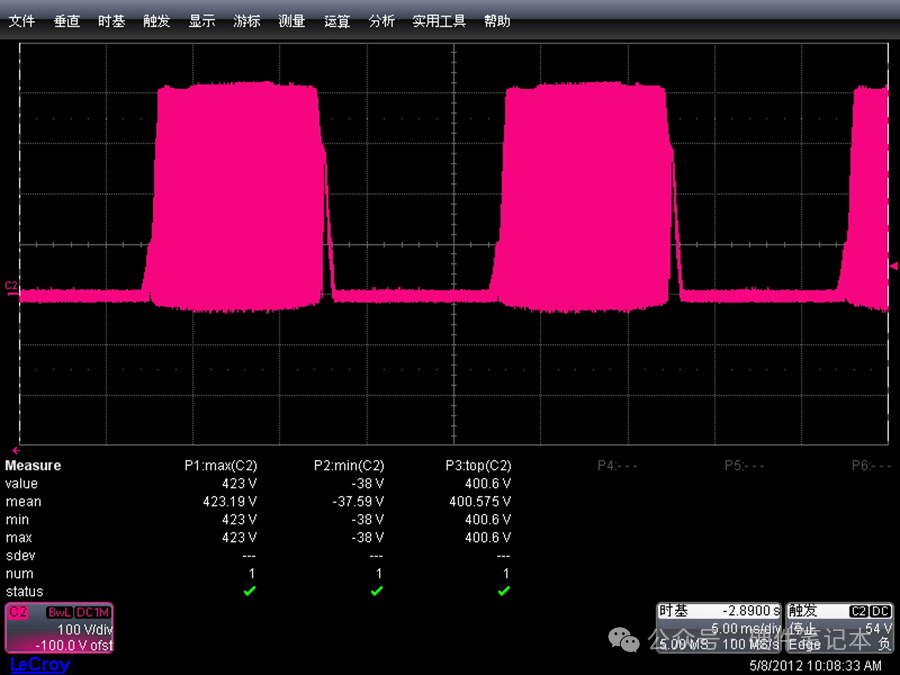

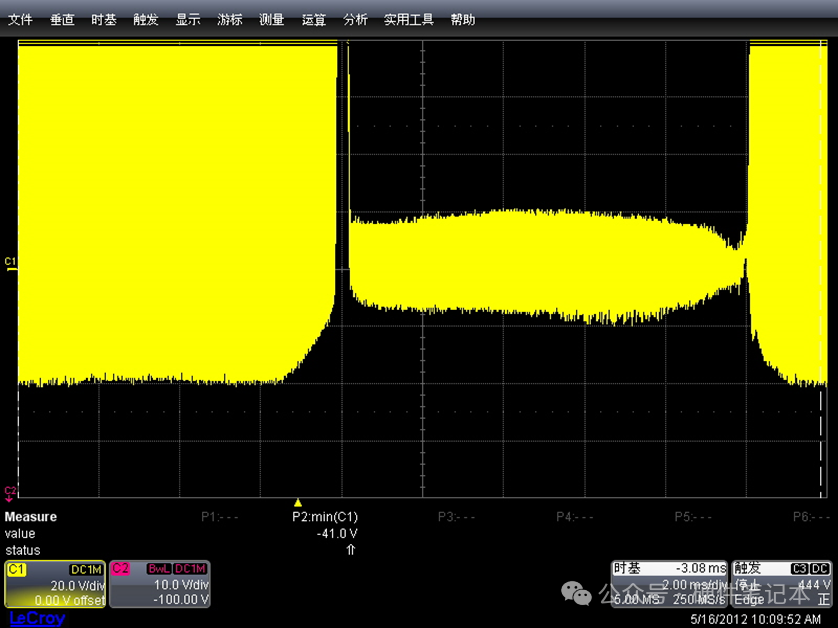

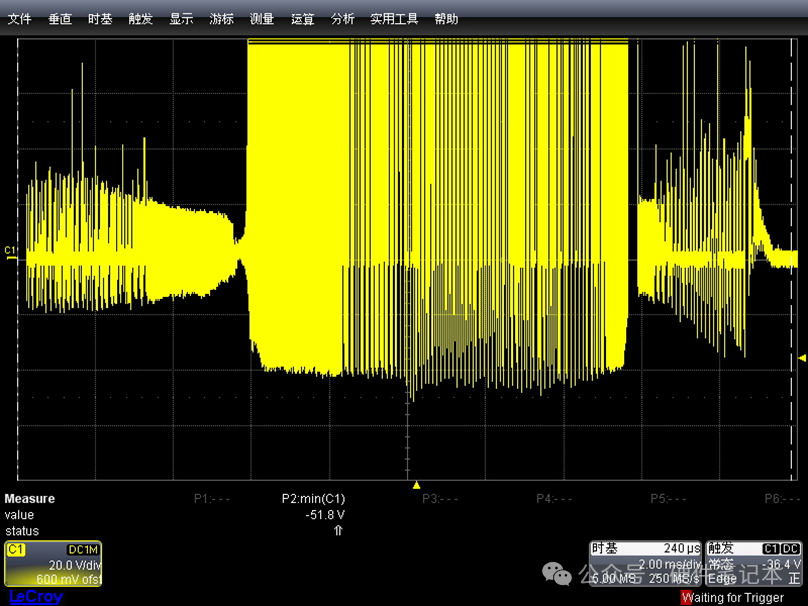

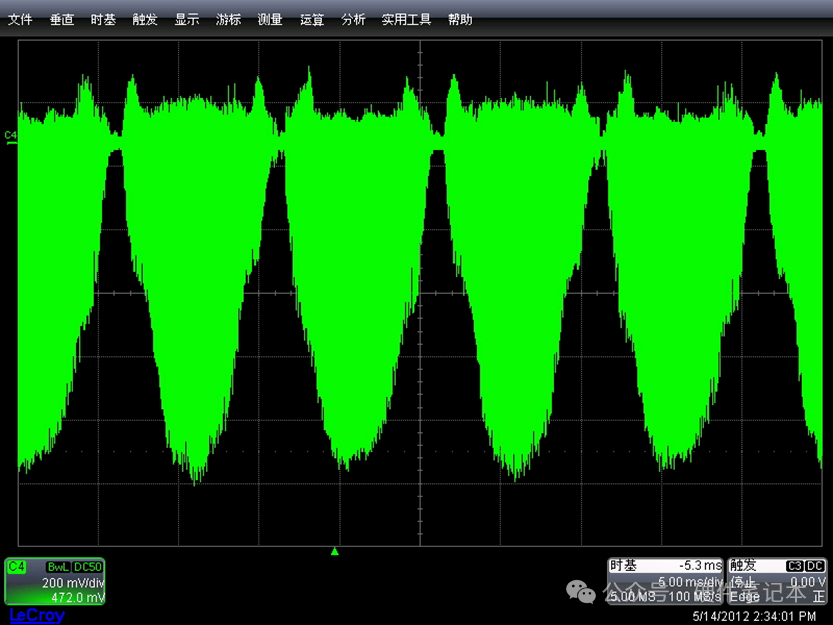

图5 VS-COM的电压波形

交流正半周VS-COM之间的电压不发生抖动,被慢速二极管钳位到母线电容的地。而在交流负半周,VS-COM之间的电压有高频抖动,对应于PFC的驱动。

图6 VS-COM之间的电压波形,展开后的VS-COM之间的电压波形

2. VS-COM之间产生负压的原因

VS-COM之间负压如何产生的?

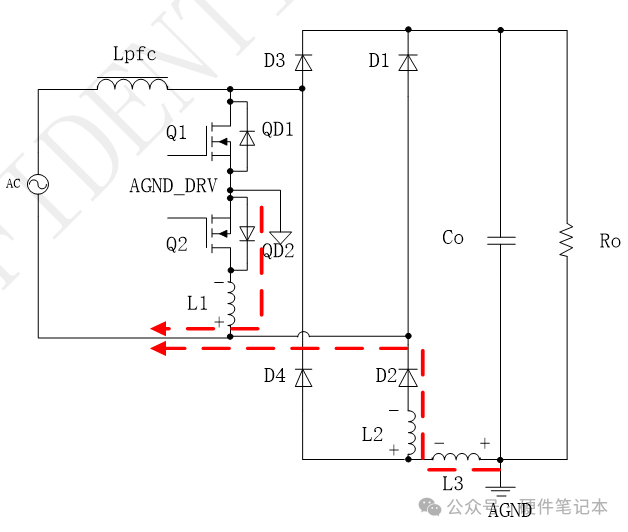

图7 交流输入正半周,MOS管关断换流期间产生负压的机理

AC交流输入正半周,MOS管关断换流期间,AGND_DRV与AGND之间存在负压,这是由于器件的寄生电感和PCB走线的寄生电感,在高di/dt的情况下产生了负压。上面的图示中,L1为Q2的寄生电感,L2为D2的寄生电感,L3为PCB走线的寄生电感,关断时刻产生的电压方向如上图所示。

稳态时:Vvs-com=VQD2 - VD2

换流时:Vvs-com=VQD2 - VD2 - L1*dIL1/dt - (L2+L3)*dil2/dt

图8 交流输入负半周,MOS管关断换流期间产生负压的机理

AC交流输入负半周,MOS管关断换流期间,AGND_DRV与AGND之间存在负压,这是由于器件的寄生电感和PCB走线的寄生电感,在高di/dt的情况下产生了负压。上面的图示中,L1为Q1的寄生电感,L2为D4的寄生电感,L3为PCB走线的寄生电感,关断时刻产生的电压方向如上图所示。

稳态时:Vvs-com=VQD1 - VD4

换流时:Vvs-com=VQD1 - VD4 - L1*dIL1/dt - (L2+L3)*dil2/dt

因此可以归纳总结出在负压产生的时刻是MOS关断换流的时候产生的。

在短路或者动态,较大的电流变化率时,将产生足够大的负压,超过VS-COM之间可以承受的负压范围,此时芯片会发生失效。(感谢关注公众号:硬件笔记本)

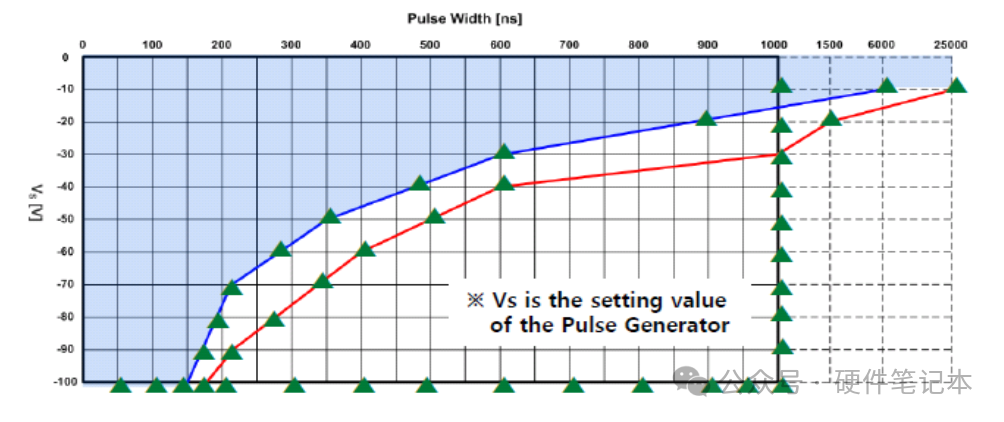

FAN73711芯片正常工作条件下,VS脚可以承受的负压范围如下图。

图9 VS脚的SOA工作区

3. 如何解决VS-COM的负压问题

由于负压的大小比较难以测试准确,因此,我们通过验证的方式,来检验措施的可行性。

1. 增加PFC驱动电路的驱动电阻,降低di/dt,以减小寄生电感产生的负压尖峰。

我们将PFC驱动电阻由原来的3.75ohm改为10ohm,测试85V~290V 1000W源跳变,PFC MOS依然会炸机。

2. 在VS-COM之间加RC吸收,R为3个18ohm电阻,C为1个100pF,发现没有太大效果,源跳变依然会出问题。

3. D101和D102由原来的快恢复二极管改为SIC二极管,没有效果,源跳变依然会炸机。

4. D101-1和D102-2并联10nF金膜电容,没有效果,源跳变依然会炸机。

5. 在VS-COM之间加钳位二极管(编码为15010247),有效果,测试85V~290V 1000W源跳变不会出现炸机的问题。

6. 在VS-COM之间加二极管并联3.3V稳压管,有效果,测试85V~290V 1000W源跳变不会出现炸机的问题。

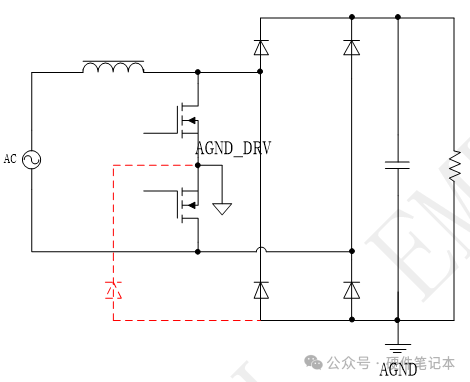

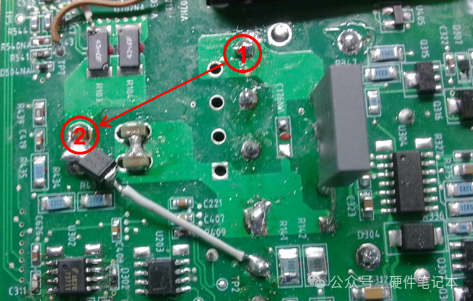

图13 使用二极管钳位的方案

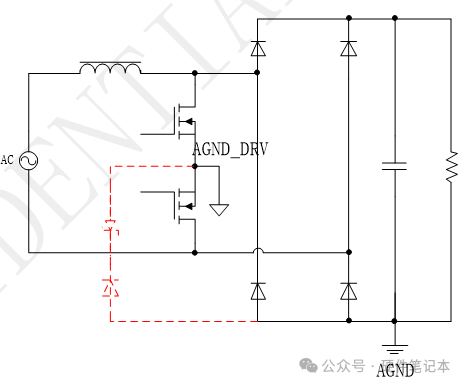

图14 使用二极管串联稳压管钳位方案

值得注意的是:钳位吸收的摆放的位置非常关键,影响到吸收的效果。

图15 钳位二极管的摆放位置

将二极管的阳极放在1的位置时,源跳变还是会炸机,移动到2时就不会出现问题。

虽然位置1和位置2是在同一个PCB网络上,但是位置1~2之间有走主功率电流,如果将吸收电路放在位置1,只能吸收一部分的主功率回路产生的负压尖峰;放在位置2,能够完全吸收整个功率回路产生的负压尖峰。因此应该将吸收的位置放在2的位置。

关于吸收摆放的位置,我们还做了一个实验,就是将吸收电路放在驱动芯片的根部,即驱动芯片VS脚和COM脚,也能达到同样的效果,源跳变不会发生炸机。(感谢关注公众号:硬件笔记本)

另外,由于PCB上的Vb和Vs脚之间的解耦电容放置得很远,较大的扰动下可能导致Vb产生负压,使得芯片失效,因此建议在靠近Vb和Vs脚之间增加一个1uF的解耦电容。

4. 测试芯片VS-COM之间的电压是否超标

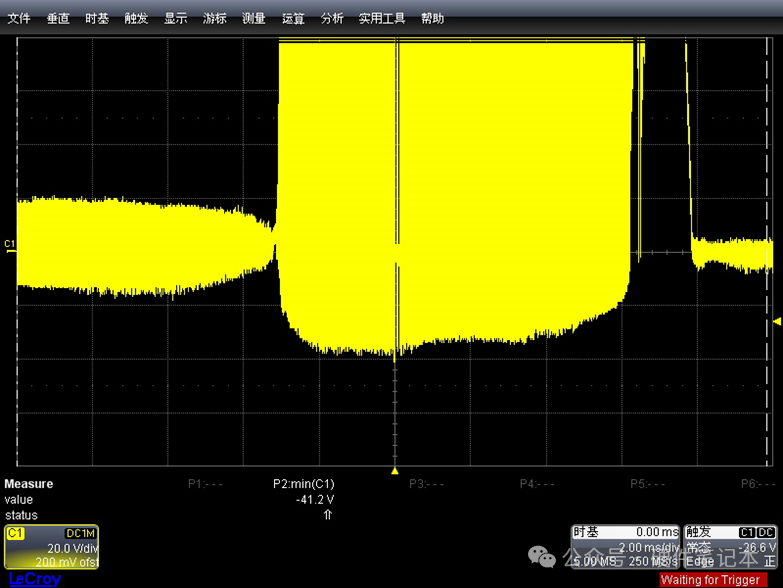

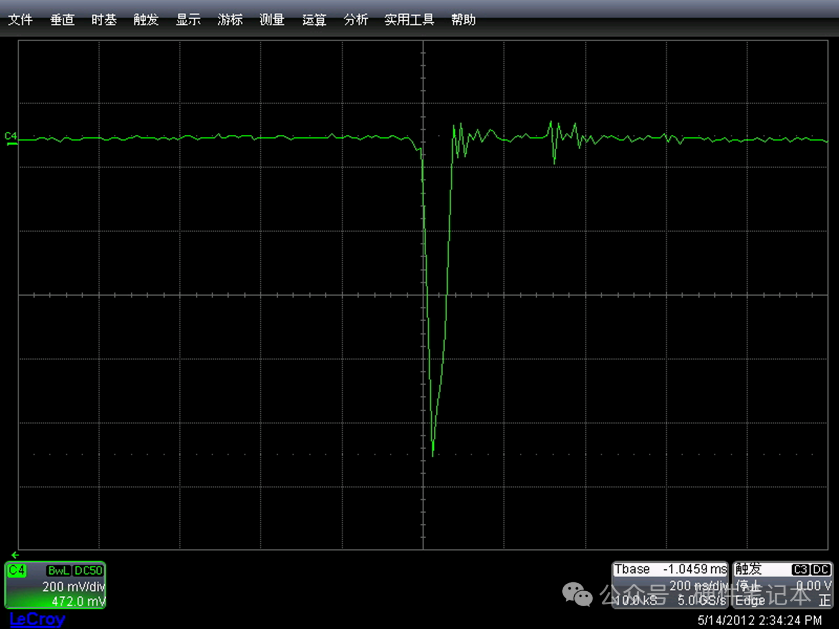

图16 VS-COM的电压波形,53.5V 37.4A,未加钳位二极管吸收

图17 VS-COM电压波形,180V~280V源跳变 1605W,加钳位二极管吸收

图18 VS-COM电压波形,180V~280V源跳变 1605W,未加钳位二极管吸收

从图17和图18可以发现,加了钳位吸收后,源跳变时的负压有所减小。

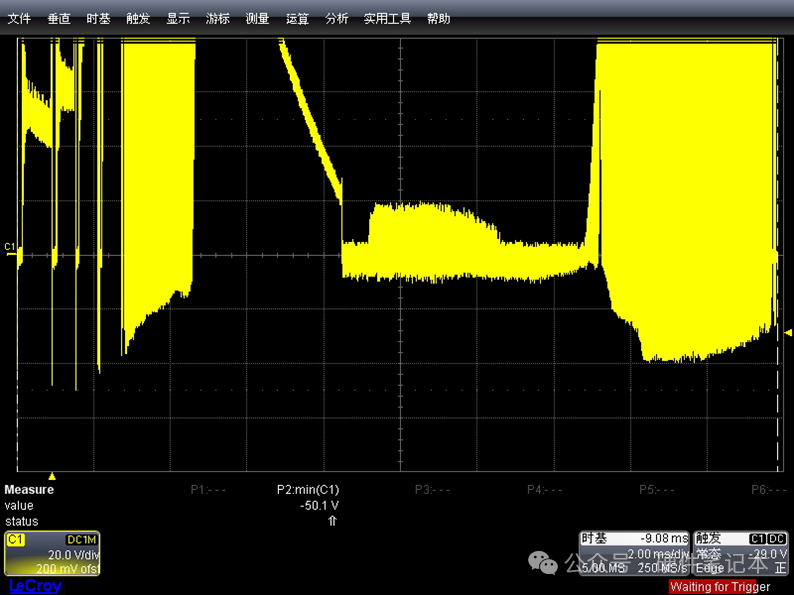

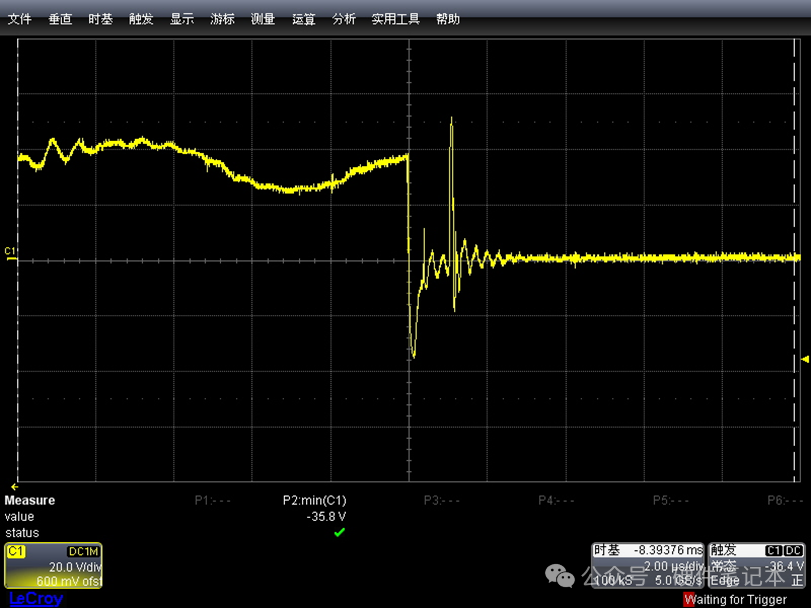

图19 VS-COM电压波形,85Vac~290Vac 1000W源跳变,未加二极管钳位出现炸机

图20 VS-COM电压尖峰,85Vac~290Vac 1000W源跳变,未加二极管钳位出现炸机

未加钳位吸收电路,85Vac~290Vac 1000W源跳变,出现炸机的现象,图19和图20是最后炸机的波形,可以看出正半周时负压已经达到35.8V,这就是导致驱动芯片异常的原因,导致驱动异常,PFC炸机。

5. 钳位二极管电流波形测试

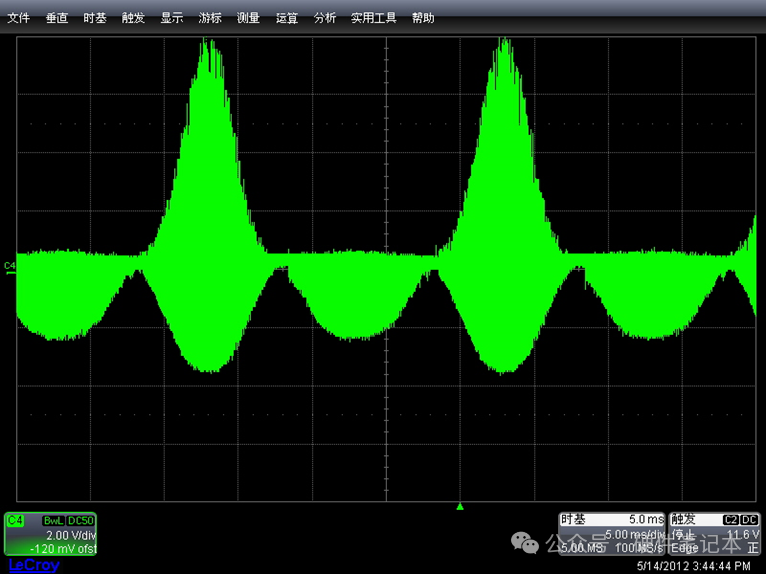

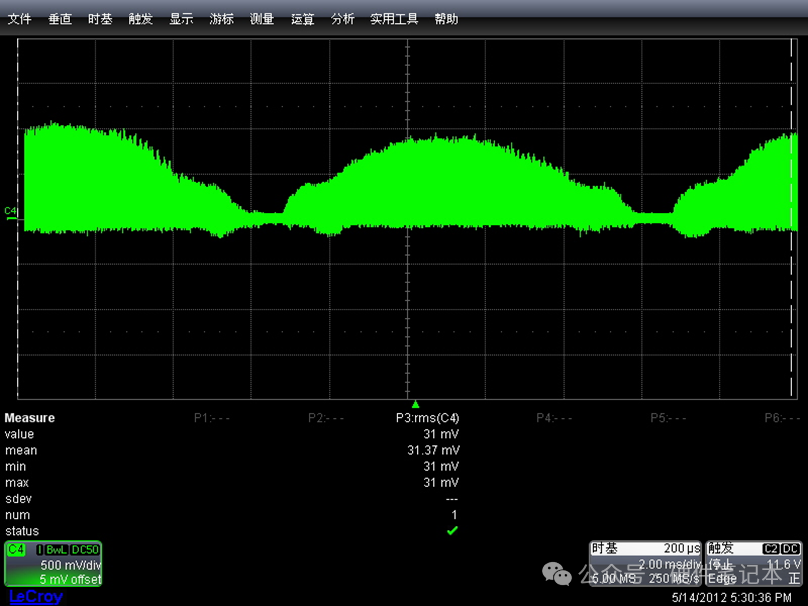

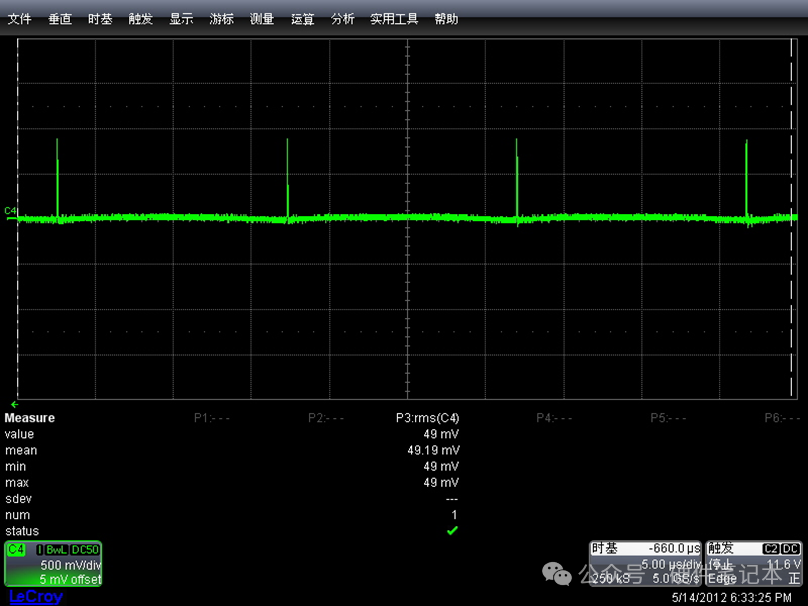

图21 使用二极管钳位,二极管上的电流波形,53.5V 37.4A 2A/div

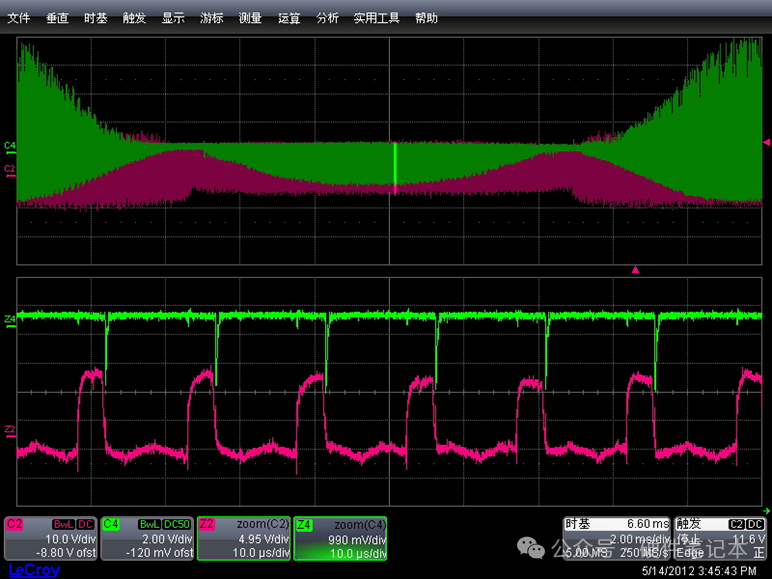

图22 使用二极管钳位,二极管上的电流波形(绿色通道),红色通道为驱动波形,53.5V 37.4A 2A/div

图23 使用二极管钳位,二极管上的电流波形(绿色通道),红色通道为驱动波形,53.5V 37.4A 2A/div

6. 二极管串联稳压管钳位电流波形测试

图24 使用二极管串联稳压管钳位,二极管上的电流波形,53.5V 37.4A 200mA/div

图25使用二极管串联稳压管,二极管上的电流波形,53.5V 37.4A 200mA/div

7. 稳压二极管的选择

图26 满载条件下,用示波器计算稳压管上的平均电流

图27 满载条件下,用示波器计算稳压管上的平均电流

测试时我们用的稳压管为3.3V SOT-23封装的稳压管,稳压管的选择需要满足两个条件,平均功耗和瞬时功耗(瞬时电流)。

看波形,平均功耗大约100mw,瞬时功耗大约3、4W,瞬时电流大约1A。

选SOT-23基本可以满足要求,但1A的瞬时电流比较悬,这种封装的键合线耐受的电流峰值也就在1A到数A,物品部建议选择SOD123封装的器件比较保险,可以满足要求并且有一定裕量。

8. PFC驱动电路可靠性测试

通过二极管串联稳压管钳位吸收后,为了验证其可靠性,我们分别作了高低温源跳变和极限ATE测试。

测试项目包括:环温-20度85V~290V 1000W源跳变 2小时,-20度 176V~290V 2000W源跳变2小时,55度85V~290V 1000W源跳变2小时,55度176V~290V 2000W源跳变2小时,测试均能通过,模块不损坏。

用另一台模块进行极限ATE测试时,驱动芯片发生损坏,经过分析是由于芯片靠近VB和VS脚之间没有加1uF的解耦电容,导致芯片损坏,增加这个解耦电容后,重新进行极限ATE测试,模块没有损坏。

总结

H桥PFC驱动采用FAN73711的方案,由于VS-COM之间主功率走线通过了MOS管和整流桥,走线相对较长,导致寄生电感比较大,MOS管关断时存在负压的尖峰,超过了芯片VS脚的安全工作电压,导致驱动芯片异常。(感谢关注公众号:硬件笔记本)通过在VS-COM之间加钳位二极管或者钳位二极管串联稳压管,具有一定的效果,经过测试,源跳变不会发生炸机。另外,由于PCB的Vb-Vs脚的解耦电容相对较远,对芯片的抗干扰能力也有影响。

审核编辑:黄飞

-

被动PFC恒流LED驱动器电路2009-06-28 1657

-

PFC电路详解2014-10-26 0

-

LED驱动电源PFC电路的设计2018-10-22 0

-

PFC开关管驱动方案2019-03-19 0

-

【专辑精选】PFC电路系列教程与设计资料2019-04-17 0

-

开关电源PFC电路的EMI分析与设计2020-10-21 0

-

常见的无桥Boost PFC电路对比分析2020-10-30 0

-

按下复位键时电机驱动炸了怎么解决?2023-11-10 0

-

无桥Boost PFC电路的EMI实例分析2016-11-30 13530

-

针对无桥Boost PFC电路的验证及EMI实例分析2016-12-08 4790

-

液晶电视电源pfc电路_液晶pfc电路维修技巧2018-01-23 75938

全部0条评论

快来发表一下你的评论吧 !