什么样的信号线需要50欧姆阻抗,85欧姆阻抗?

描述

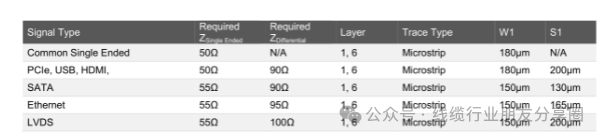

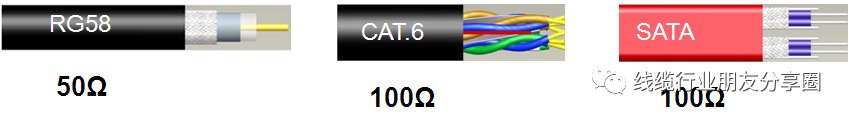

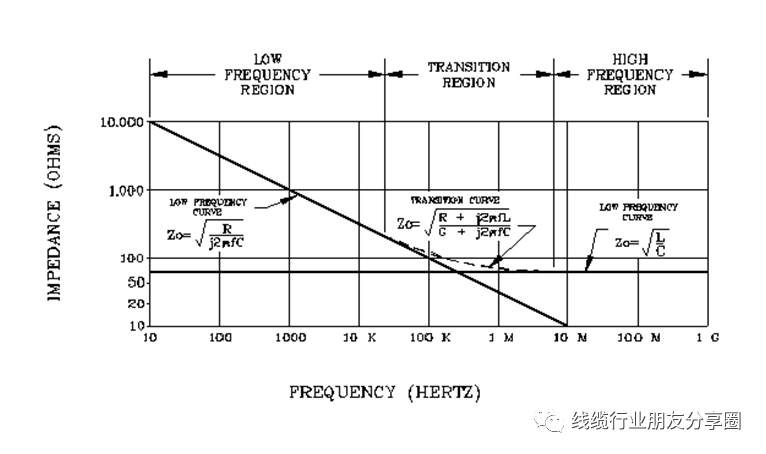

特征阻抗这个名词是对于交流信号(或者说高频信号)来说的;特征阻抗属于长线传输中的一个概念,信号在传输线中传输的过程中,在信号到达的一个点,传输线和参考平面之间会形成电场,由于电场的存在,会产生一个瞬间的小电流,这个小电流在传输线中的每一点都存在。同时信号也存在一定的电压,这样在信号传输过程中,传输线的每一点就会等效成一个电阻,这个电阻就是我们提到的传输线的特征阻抗。如今,高速系统面临着许多必须在同一堆叠中实现的同步阻抗要求 ;如以太网的100欧姆差分阻抗,90欧姆的USB,85欧姆的PCIe以及无数的单端DDR要求。我们希望遵循规范,以正确的阻抗选择组件和布线走线。然而,有时也存在一些障碍——首选元件不是85欧姆,或者上游封装是另一种阻抗。规范怎么说?我上传了如下图片有常用接口的阻抗要求,可以参考一下;

什么样的信号线需要50欧姆阻抗,85欧姆阻抗,90欧姆阻抗,100欧姆阻抗

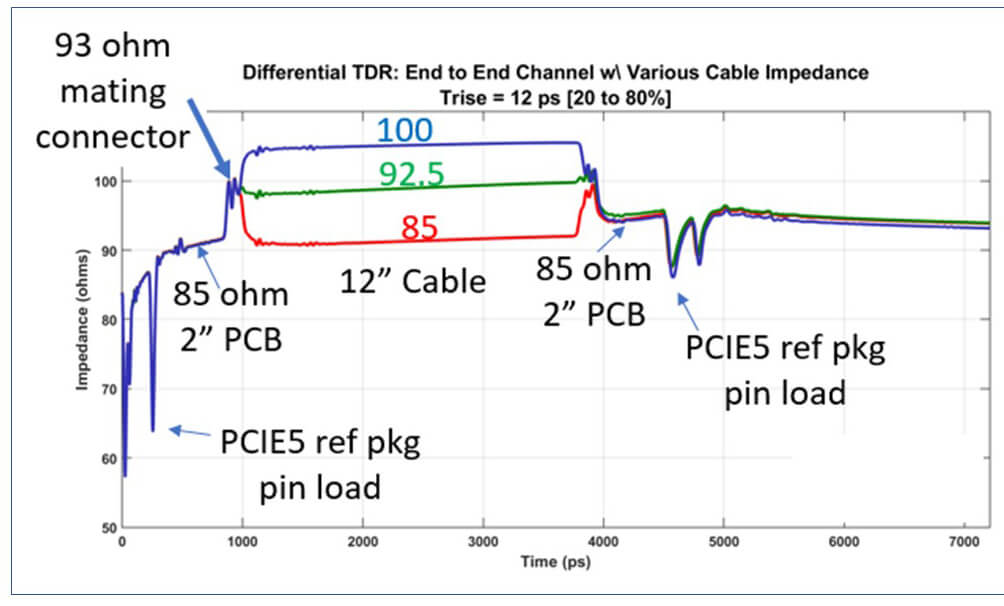

我们知道,较高的阻抗,插入损耗会比较好(衰减会比较小),之前我们做过数据分析,85欧姆和100欧姆阻抗之间的损耗差高达14%。而较高阻抗的PCB确又有具有更大的损耗;也就是说,阻抗和损耗之间的关系与PCB关系又成反比。举例:目前PCIE平行对的线材阻抗有85欧姆和100欧姆两种,看了一个关于PCI Express Layout gudie的文档,其中关于阻抗的要求PCI Express link traces must maintain 100 Ω differential / 60 Ω single-ended impedancefor 4-layer or 6-layer boards; and 85 Ω differential / 55 Ω single-ended impedance for 8-layer or 10-layer boards. 这里就提到PCB板层不一样会有不同的阻抗要求;按照行业数据分析,PCB板子的层数多了,层间距小了,要满足原来的阻抗要求就可能导致走线太细,不能满足工艺要求,所以适当地降低阻抗目标值来保证有足够的走线宽度。这个主要是方便布线;4~6层主力布线层是top/botm,85Ω在表层线宽/间距会很大,100Ω的就会好很多。降低阻抗后,负载变重,抗干扰能力要强一点。4到6层板布线都在外层,需要考虑抗干扰能力;强制叠层和线宽间距的情况下,8层板厚度减少,阻抗就变低.

阻抗的概念和重要性

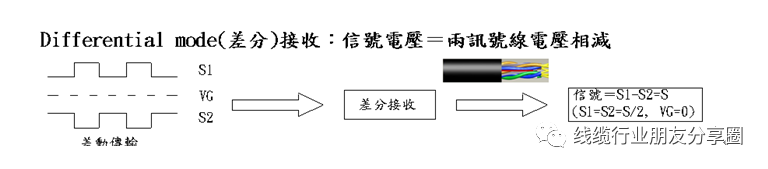

在测同一被测线材时,其阻抗会因在该被测线材上传输的信号型式不同,而分为单端阻抗,同模(共模)阻抗及差分阻抗,其差异主要表现在测试的信号条件上。将传输线始端的输入阻抗简称为阻抗;将信号随时遇到的及时阻抗称为瞬时阻抗如果传输线具有恒定不变的瞬时阻抗,就称之为传输线的特性阻抗;和电阻,电容,电感一样,传输线也是一种理想的电路元件,但是其特性却大不相同,用于仿真效果较好,但电路概念却比较复杂;依传输的讯号型式不同.单端阻抗 Zse (Single Ended):差动阻抗 Zdiff (Differential Mode);同模阻抗 Zcom (Common Mode).

早期的数字总线大部分使用单端信号做信号传输,如TTL/CMOS信号都是单端信号。所谓单端信号,是指用一根信号线的高低电平的变化来进行0、1信息的传输,这个电平的高低变化是相对于其公共的参考地平面的。单端信号由于结构简单,可以用简单的晶体管电路实现,而且集成度高、功耗低,因此在数字电路中得到最广泛的应用。

当信号传输速率更高时,为了减小信号的跳变时间和功耗,信号的幅度一般都会相应减小。比如以前大量使用的5V的TTL信号现在使用越来越少,更多使用的是3.3V/2.5V/1.8V/1.5V/1.2V的LVTTL电平,但是信号幅度减小带来的问题是对噪声的容忍能力会变差一些。进一步的,很多数字总线现在需要传输更长的距离,从原来芯片间的互连变成板卡间的互连甚至设备间的互连,信号穿过不同的设备时会受到更多噪声的干扰。更极端的情况是收发端的参考地平面可能也不是等电位的。

因此,当信号速率变高、传输距离变长后仍然使用单端的方式进行信号传输会带来很大的问题。为了提高信号在高速率、长距离情况下传输的可靠性,大部分高速的数字串行总线都会采用差分信号进行信号传输。差分信号是用一对反相的差分线进行信号传输,发送端采用差分的发送器,接收端相应采用差分的接收器。采用差分传输方式后,由于差分线对里正负信号的走线是紧密耦合在一起的,所以外界噪声对于两根信号线的影响是一样的。而在接收端,由于其接收器是把正负信号相减的结果做为逻辑判决的依据,因此即使信号线上有严重的共模噪声或者地电平的波动,对于最后的逻辑电平判决影响很小。

相对于单端传输方式,差分传输方式的抗干扰、抗共模噪声能力大大提高。采用差分方式进行信号传输会使得收发端的电路变得复杂,系统的功耗也随之上升,但是由于其优异的抗干扰能力以及可靠的传输特性,使得差分传输方式在需要进行高速数字信号的传输或者恶劣工作环境的领域得到了广泛的应用,如LVDS、PCI-E、SATA、USB、1394、CAN、Flexray等总线都是采用差分的信号传输方式。

一般而言仪器的端口是以单端50Ω的阻抗最为常见。如欲以NA量测“差分讯号”时,需经由Bulan转换将NA的“单端讯号”转换成差分讯号。TDR的“单端讯号”转成“差分讯号”或“同模讯号”时,只需设定仪器端口即可。其实,阻抗匹配的概念并不止于此,如果将两段均匀的同轴电缆连接起来,在连接点处如果“加工”工艺视屏高,金属衔接平顺,没有出现微观结构意义上的阻抗突变现象,则我们也把这两段同轴线的连接也称作匹配。

推而广之,凡是阻抗连续的连接点我们都说它们是“匹配”的。按照这个思路,我们就知道通常在双绞线和模块的连接点处,阻抗是很可能有“失配”现象存在的,一条布线链路中的接插件和连接件所在的位置经常也是阻抗不连续的位置(或者说是阻抗失配的位置)。不连续的原因主要是传输线的几何结构或材质(包含绝缘介质的材质)发生了突变。凡是阻抗不连续点,也“一定是”一个信号能量的反射点(回波源)。对于产品设计和生产商来说,就是要制作出连接点阻抗尽量平顺连续的产品 —模块、跳线、各种工业连接器、各种异型非标接插件等等。

-

为什么PCB设计一般为50欧姆阻抗?2023-07-03 1206

-

PCB设计中为什么特性阻抗线只有50欧姆和100欧姆两个值?2011-11-28 0

-

请问该平衡端的走线是否按照差分走线的阻抗来设计?是按照50欧姆还是100欧姆还是其他阻抗值来设计微带线阻抗?2018-06-06 0

-

想知道rf 50ohm阻抗设置的示波器电路是什么样的?2018-08-24 0

-

请问为什么很多PCB传输线的阻抗都是50欧姆?2018-11-27 0

-

请问什么样的信号线需要50欧姆阻抗,90欧姆阻抗,100欧姆阻抗?2019-03-19 0

-

高速信号线的特征阻抗2019-06-14 0

-

你能想象吗,传输线能控到多少阻抗还要看隔壁信号线的脸色?2023-11-02 0

-

AppCAD计算天线信号线特性阻抗2011-12-14 8336

-

射频系统中的50欧姆特性阻抗2018-05-05 17317

-

TE Connectivity的Z-PackTinMan100欧姆和85欧姆连接器,占位阻抗易匹配2018-09-25 6035

-

PCB设计为何控制50欧姆阻抗?2020-01-15 9796

-

射频系统中的50欧姆特性阻抗详细介绍2020-11-23 2548

-

PCB阻抗设计匹配的理想模型及方法2023-02-17 985

-

射频为什么50欧姆 射频阻抗为什么是50欧姆2023-09-02 2103

全部0条评论

快来发表一下你的评论吧 !