如何减少无源晶振在电路中的电磁干扰

描述

无源晶振,作为一种常见的电子元件,广泛应用于各种电子设备中,尤其在通信、计算机、消费电子等领域。然而,无源晶振在工作过程中会产生电磁干扰(EMI),影响电路的稳定性和性能。本文旨在探讨如何减少无源晶振在电路中的电磁干扰。

一、了解无源晶振的工作原理

无源晶振是一种能够产生稳定频率的元件,其工作原理是通过压电效应使晶体片产生振动,从而产生稳定的频率。在工作过程中,晶振会产生电磁场,进而产生电磁干扰。因此,了解无源晶振的工作原理是减少电磁干扰的基础。

二、优化电路设计

合理布局:在电路设计中,应将无源晶振放置在离其他敏感元件较远的位置,以减少电磁干扰的影响。同时,避免将晶振放置在PCB板的边缘,以减少外部电磁干扰。

选择合适的地线:为无源晶振提供独立的低阻抗地线,以降低电磁干扰。确保地线宽度足够,以减少电阻,降低地线电位差。

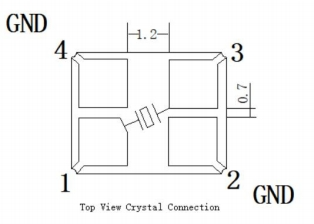

华昕4脚贴片无源晶振引脚说明:脚2与脚4与外壳连接,请接地GND处理,如下图所示:

电路板上GND地线的分类如下:

1. 模拟地线AGND

2. 数字地线DGND

3. 功率地线PGND

4. 电源地线GND

5. 交流地线CGND

6. 大地地线EGND

3.滤波措施:在晶振的电源线上加入滤波器,滤除高频噪声,从而降低电磁干扰。

三、选择合适的晶振型号

不同型号的无源晶振,其电磁干扰程度也有所不同。因此,在选择晶振时,应综合考虑其频率稳定性、温度特性、功耗以及电磁干扰等因素。选择低电磁干扰的晶振型号,有助于降低电路中的电磁干扰。

四、使用屏蔽和接地措施

屏蔽:使用金属屏蔽盒将无源晶振包裹起来,以隔绝外部电磁干扰。同时,确保屏蔽盒与电路板之间的接地良好,以提高屏蔽效果。

接地:确保无源晶振的接地端与电路板上的地线紧密连接,以减少电磁干扰。在实际操作中,可以考虑使用多层地线结构,以提高接地效果。

五、软件优化

在某些情况下,通过软件优化也可以降低无源晶振产生的电磁干扰。例如,通过调整晶振的工作模式、降低其工作频率或改变其驱动方式等,可以在一定程度上减少电磁干扰。

六、测试和验证

在采取了上述措施后,应对电路进行测试和验证,以确保电磁干扰得到了有效降低。测试过程中,可以使用专业的电磁干扰测试设备,对电路中的电磁干扰进行定量评估。同时,根据测试结果,对电路进行进一步优化,以达到更好的电磁干扰抑制效果。

全部0条评论

快来发表一下你的评论吧 !