基于单端10 bit SAR ADC的IP核设计与实现

IP核设计

描述

随着集成电路和数字信号处理技术的快速发展,我们可以在数字域里实现比模拟域里更高精度,更快速度,更低价格的各种信号处理功能,因此,模数转换器作为模拟系统和数字系统的接口就变得非常重要。而在各种类型的模数转换器当中,逐次逼近型的模数转换器(SAR ADC)因为其低功耗,中等精度和中高分辨率而得到了广泛的应用。而SARADC从输入来分,可以分为单端输入和双端(全差分)输入。虽然一个双端SAR ADC电路架构可以获得更好的共模抑制比和和较少的失真,而得到了广泛的应用,但在现实生活中对单端的ADC仍有一定的需求,如光栅尺中绝对码道信号的检测。本文则是在一种常见单端SAR ADC电路架构的基础上,对D/A转换器进行了改进,在不增加电容面积的情况下,减小了D/A转换时电容和开关所消耗的能量,减小了电容阵列转换的建立时间。

1 ADC整体电路设计

本文设计的单端SAR ADC的整体架构如图1所示,主要包括以下4个部分:采样保持电路(Sample and Hold)、比较器(Comp)、10-bit逐次逼近寄存器及控制电路(SARLOGIC)、D/A转换电路(DAC)。

输入电压Vin通过采样保持电路得到采样电压Vsh,Vsh与DAC的输出Vdac通过比较器进行比较,比较结果传递给逐次逼近寄存器,逐次逼近寄存器一方面输出比较结果,另一方面控制DAC的转换开关,以便进行下一位的转换。

1.1 SAR ADC的工作流程

SAR ADC的工作流程如图2所示,它主要可以分为采样、清零阶段和比较阶段。

第一步:采样、清零阶段。采样保持电路中的开关S,闭合,Vin=Vsh,属于跟随阶段;DAC中的电容C1p~C10p和C1n~C10n的下级板全部接GND,开关EN闭合,Vdac接GND,DAC处于清零阶段。

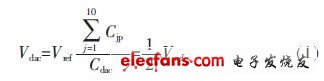

第二步:比较阶段。采样保持电路中的开关Sa断开,Vsh为采样得到的电压;DAC中的电容C1p~C10p的下级板接Vref,其余开关不动,而开关EN断开,此时DAC的输出结果:

Vsh与Vdac进行比较,如果Vsh大于Vdac,则比较器输出为1,即D1=1,而逐次逼近寄存器根据比较结果,将电容C10n(MSB电容)的下级板偏转到Vref;反之D1=0,C10p的下级板偏转到GND。其余电容保持不变。

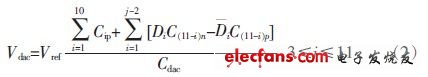

第j步:根据上一步比较的结果,得到DAC的输出如下:

Vsh与Vdac进行比较,如果Vsh大于Vdac,则比较器输出为1,即Dj-1=1,而逐次逼近寄存器根据比较结果,将电容C(11-j)n的下级板偏转到Vref;反之Dj-1=0,C(11-j)p的下级板偏转到GND。其余电容保持不变。直至j=11,比较结束,进入下一个转换周期。

1.2 DAC电路架构

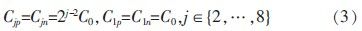

本文采用的DAC架构如图1所示,主要采用分割二进制电容加权结构,由逐次逼近逻辑(SAR)产生的控制信号S0到S11来控制DAC的开关。其中:

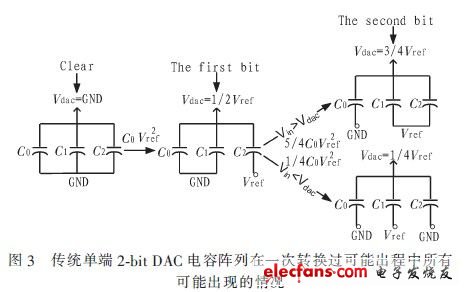

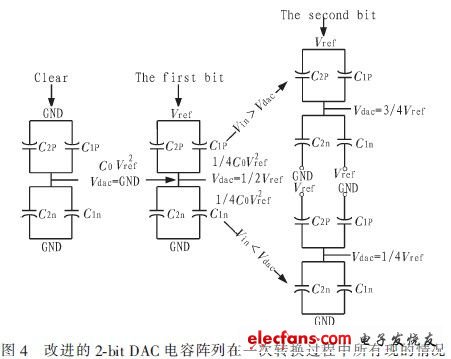

传统的电容阵列在转换过程中效率很低。为了说明这一点,以一个传统的2-bit电容阵列为例,如图3所示,其中C2=2C1=2C0。清零阶段,所有电容全部接GND,没有能量消耗。当清零过后,进行第一位的比较时,MSB电容C2接Vref,而其他电容(C0和C1)仍然接地,因此电容阵列的输出Vdac=1/2Vref,其中Vref是参考电压,此时电容从参考电压吸收的能量。在进行第二位的比较时,DAC进行两种转换:如果Vsh》Vdac,进行“up”转换,即C1接Vref(C1起始接GND),因此Vdac=3/4Vref,则需要从参考电压吸收的能量;相反地,如果Vsh《Vdac则需要进行“down”转换,如图4所示;C1接Vref(C1起始接GND)而C2接GND(C2起始接Vref),因此Vdac=1/4Vref,假设它们在同一时间进行变换,则需要的能量。它所需要的能量是“up”转换时能量的5倍;发生这种情况是因为C2最开始充进去的电荷都必须向地(GND)放走,而C1则必须从参考电压(Vref)上吸收电荷。而分割电容阵列在转换时的能量消耗较少。为了与上述例子进行比较,也拿一个2-bit的分割电容阵列为例,如图4所示,其中C1p=C2p=C1n=C2n=C0。清零阶段,所有电容全部接GND,没有能量消耗。当清零过后,进行第一位的比较时,C1p与C2p的下极板接Vref,DAC的输出Vdac等于1/2Vref,其中Vref是参考电压,此时电容从参考电压吸收的能量。当进行第二位的转换时,DAC进行两种转换;如果Vsh》Vdac,进行“up”转换,即C1n接Vref(C1n起始接GND),需要从参考电压吸收的能量;相反的,如果Vsh《Vdac,则需要进行“down”转换,如图4所示;C1p接GND(C1p起始接Vref),需要从参考电压吸收。

从上述可以看出,传统电容阵列在“up”转换时消耗能量最少,而在“down”转换时消耗能量最大,而分割电容阵列相对来说消耗的能量较少。通过仿真可以得知,本文所用的SAR ADC结构由于电容偏转所消耗的平均能量比传统的SAR ADC要节省30%左右。

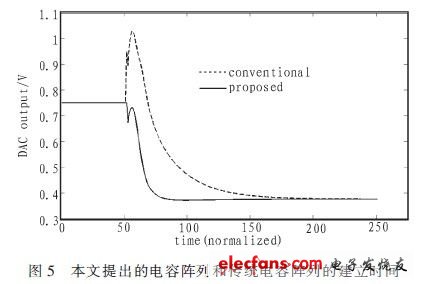

对于高速应用的ADC来说,一个重要的技术指标就是DAC的建立时间。在“down”转换过程中,传统电容阵列中需要有两个电容进行切换,而控制电容转换的开关在转换过程中的任何不匹配,无论是随机的还是确定的,都可以引起电容阵列向错误的方向进行转换,甚至引起前置放大器的过载。而分割电容阵列在每一位的比较过程中,只有一个电容变化时,对开关信号的歪斜有很好的抵制作用。图5是通过仿真对两个电容阵列的建立时间进行了对比。从仿真结果可以看出,当分割电容阵列和传统阵列开关时间的宽度相同时,分割电容阵列的建立时间比传统阵列的建立时间快了8%左右,而且电容值越大,建立时间缩小的越明显。

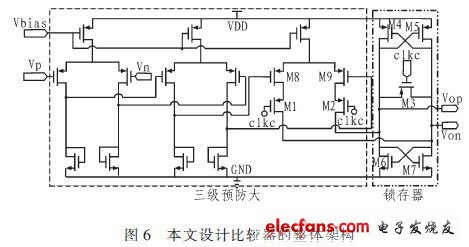

1.3 比较器电路架构

文中采用的比较器结构简化如图6所示,它是由三级预放大和锁存器组成,其中一、二级预放大器结构相同。比较器的失调电压是影响比较器比较精度的一个重要参数,进而影响整个ADC的精度,而失调电压是经过放大器放大之后再存储在电容上的,所以放大级的增益不能太大。过大的增益会使输出饱和,这样存储在电容上的电压就不能反映真实的失调电压的值,所以三级预放大器每一极均有较小的增益,这样做还可以获得较大的带宽,提高比较器整体的响应速度。但是比较器的增益过低,则会影响其精度,而锁存器的使用则是为了提高比较器的增益,同时又降低其功耗,进而提高比较器的有效精度。

2 版图设计与系统仿真

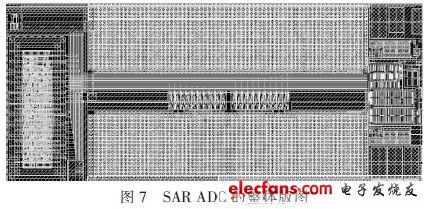

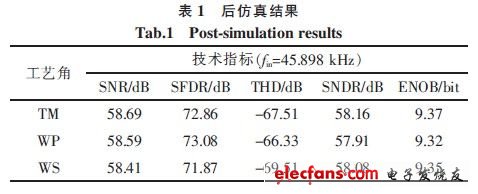

本设计基于Cadence Virtuoso版图编辑工具对SAR ADC进行布局布线和版图绘制。电容阵列采用MIM(metal-insulator-metal)电容,提高了工艺兼容性,减小了成本。在版图布局方面,电容阵列采用对称的布局方式进行布局,有效地减小了电容匹配误差。由于本文的逐次逼近寄存器及控制电路是采用verilog编码,并通过Encounter工具生成的数字电路,因此本文将数字电路和模拟电路分开布局,并用电地环进行隔离,以防止相互干扰。电路版图如图7所示,芯片版图面积约为800μmx340μm。最后利用Assura软件从版图生成了带寄生参数的网表,并进行了后仿真,以验证电容不匹配及寄生参数等对电路的精度、速度的影响。在采样速度为1-MS/s,信号频率为50 kHz的情况下,后仿真的3种工艺角结果如表1所示。从表1中可以看出,ADC的有效位数为9.3 bit左右,基本达到预期目标,可以正常工作。

3 结论

文中设计了一种单端10-bit SAR ADC IP核,分析了整个系统的主框架和数模转换电路(DAC)以及比较器。采用XFAB 0.35μm CMOS工艺,利用Cadence Spectre软件,对系统进行了仿真。仿真结果表明在电源电压3.3 V,输入电压范围0~1.5 V,采样速率为1 MHz,输入信号频率50 kHz的情况下,测得有效位数ENOB为9.37 bit,SNR为58.69 dB,SFDR为72.86 dB,THD为67.51 dB,SNDR为58.16 dB,功耗仅为4 mW。满足设计需求,可以应用于单端输入信号电路中。

-

ADC IP核的选购2015-11-06 0

-

AD7265采用差分和单端配置的12位 3通道SAR ADC2019-06-17 0

-

这个SAR ADC怎么样?2021-06-24 0

-

为什么ADC中单端和差分得到的结果不同?2021-07-18 0

-

±10V真双极SAR ADC2021-04-22 560

-

IP_数据表(A-13):12bit 2MSps SAR ADC(R06PM0013EJ0111)2023-03-14 151

-

IP_数据表(A-12):12bit 2MSps SAR ADC2023-03-16 162

-

IP_数据表(A-13):12bit 2MSps SAR ADC(R06PM0013EJ0110)2023-03-16 159

-

IP_数据表(A-14):12bit 2.5MSps SAR ADC2023-03-16 162

-

IP_数据表(A-15):12bit 2.5MSps SAR ADC2023-03-16 140

全部0条评论

快来发表一下你的评论吧 !