如何实现远程FPGA版本更新和重启?

FPGA/ASIC技术

描述

电子发烧友网核心提示:如今,大多数通讯系统均将FPGA作为其产品解决方案,且已有大量FPGA应用到通讯系统之中。为了达到降低系统维护的成本的目的,我们就需要实现FPGA远程更新重启系统的功能。本文将以Xilinx VIRTEX-6 FPGA开发板为例,给大家介绍FPGA远程更新重启系统的整个配置过程。

FPGA加载主要分为2大类,一类是主动模式(master)另一类是从模式(slave)。在主动模式时FPGA会外挂存储器存储FPGA bit映像,FPGA 会主动提供时钟访问外部存储器。在从模式时,FPGA作为从设备被挂在控制器CPU上由处理器控制对FPGA编程。上述两种模式中,因为从模式FPGA由外部CPU控制编程,可以通过远程更新CPU文件就可以实现对FPGA的版本更新,非常方便。但是当CPU外挂的FPGA较多时会使系统加载时间过长,降低系统启动速度。这里将利用FPGA 多重启(multi-boot)功能实现在主动模式下版本更新。

远程更新流程

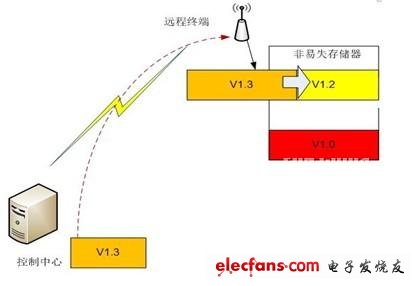

当系统需要升级时,中心控制系统需要将新的FPGA比特映像文件直接发布到远程子系统,由远程 子系统将比特文件更新到非易失存储器。然后由FPGA内部控制逻辑重新启动。比特映像文件更新后,下次上电启动将从新的比特映像文件。如图 1FPGA远程更新系统

图 1 FPGA远程更新系统

多重启动 FPGA 介绍

a)多重启动介绍

VIRTEX6可以支持2套配置文件,第一个版本为安全版本存放在起始位置(spi起始地址为0),第二个版本为最终启动版本。当FPGA启动时,加载控制器会从地址0开始读取加载指令。当读到WBSTAR和IPROG指令时,控制器就跳转到WBSTAR指定的地址读取新的加载指令。在第二个配置文件中不再发IPROG指令,控制其将顺序执行以直到配置文件结束。配置顺序如图 2。

图2 多配置文件加速过程

b)多重启动模块

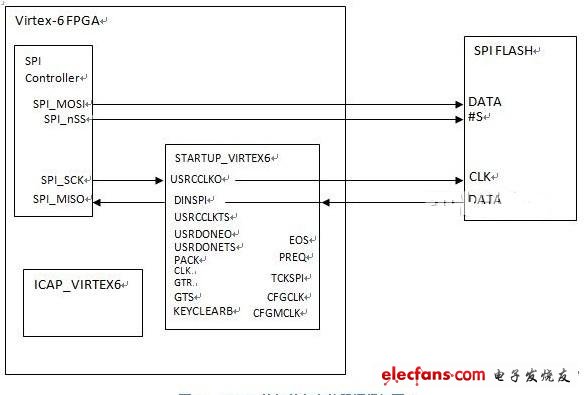

i) 配置存储器访问接口

在FPGA配置过程中,FPGA通过指定的配置管脚访问外部非易失存储器,当配置结束后,部分管脚被释放可以用作普通逻辑管脚,但部分FPGA配置管脚是配置专用,在用户应用中是不可见的,需要例化专用模块STARTUP_VIRTEX6才能允许用户逻辑访问这些专用管脚。

图3 VIRTEX6访问外部存储器逻辑框图

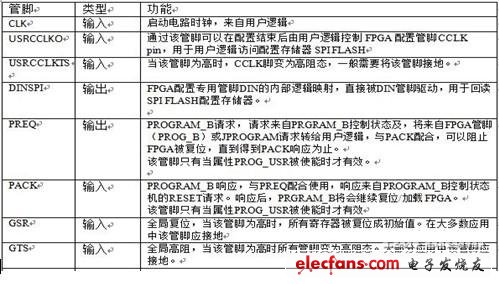

表1 STARTUP_VIRTEX6管脚定义

注意:这里只列出与重启相关的管脚,其他管脚定义请查阅手册UG360.PDF

-

易灵思内部重配置实现远程更新2023-05-30 846

-

图形更新会在重启时导致黑屏2018-11-01 0

-

altera cyclone FPGA远程更新时NIOS无法启动问题2019-02-19 0

-

请问如何通过GPRS实现远程更新2019-03-07 0

-

采用UEFI实现物联网固件更新2019-07-23 0

-

求一种基于EPCS Flash的远程在线更新FPGA程序的方法2021-06-18 0

-

请问stm32如何实现iap远程固件更新?2021-11-26 0

-

远程在线更新FPGA程序的方法2012-02-22 27730

-

基于以太网的DSP系统程序远程更新的研究与实现2017-10-20 608

-

基于XVC网络协议实现了基于JTAG接口的FPGA 的远程更新与调试2017-11-16 12895

-

QuickBoot基础知识与在FPGA逻辑远程更新的应用2017-11-18 7594

-

使用DRaaS测试操作系统更新和新代码版本2018-01-12 5093

-

FPGA远程更新有什么限制条件如何解决?2018-09-15 3596

-

如何实现远程FPGA的更新和重启2020-07-10 1367

-

国行三星A8s更新现bug:手机自动重启2021-02-04 936

全部0条评论

快来发表一下你的评论吧 !