HPM何时现身?台积电28nm制程技术回顾总结

制造新闻

描述

台积电目前最高端的制程平台无疑是其28nm CMOS平台。Chipworks网站的分析师认为,未来几年内,这个平台将是有史以来带给台积电及其客户最丰厚利润的平台。而台积电总裁张仲谋则寄望28nm平台的总产量能超过65nm平台,峰值产量达到每月13万片晶圆。

过去,台积电在对待其FPGA产品客户如Altera,Xilinx的产品制程升级时,升级的步调总是相对缓慢,不过到28nm节点,高通等移动领域的芯片厂商加入了他们的客户阵营,客户的需求发生了变化,台积电的制程转换速度在其带动下,也开始变得步调更快。尽管今年第一季度其28nm制程产品占总销售量的比例仅有5%,但到今年最后第一季度,这个比例数字有望超过20%。

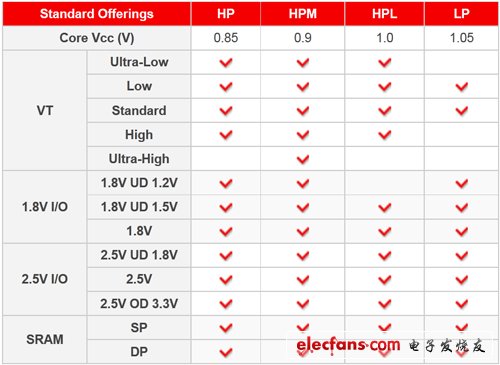

最近SEMATECH组织召开了第9次高级栅堆叠技术会议,会上台积电展示了其28nm平台的产品阵营划分状况。从介绍中可见,其28nm平台目前有四个版本,目前有关的产品已经开始大量销售,销售的对象包括Xilinx, Altera, AMD, 高通等其它厂商。

台积电成立于1987年,目前是世界最大的代工商,2011年的营收额高达145亿美元。据其官网的介绍,其2011年的总产能为1320万片(8英寸),其生产的产品种类从0.5um制程直至28nm制程不等。

台积电的28nm制程产品从2010年开始投产,共分四种类型,代号分别是HP/HPM/HPL/LP。我们过去曾经分析过其HP/HPL/LP三种制程的产品。从28nm节点起,台积电开始正式启用high-k金属栅晶体管技术(HKMG)。其中HP/HPL两种产品使用了HKMG技术,而LP产品则仍采用传统的多晶硅栅极,栅绝缘层采用ONO技术。台积电自称28nm产品2010年便开始投产,然而直到2011年中期,才有实际的产品送到研究分析人员的手上。

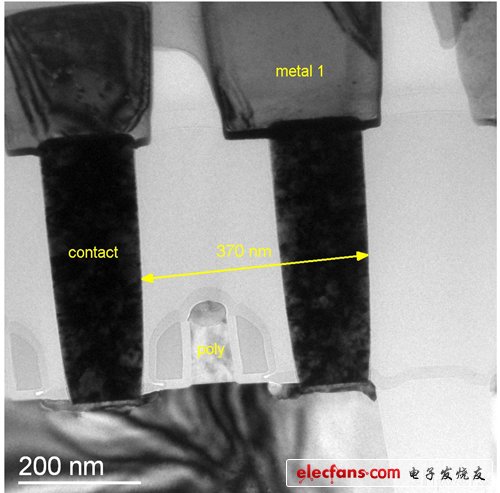

最先采用台积电28nm制程技术的仍然是Xilinx和Altera两家FPGA巨头。这类产品的特点是单价高,但产量需求少,这样对产品良率的要求便不是很高,而新制程技术实施的前期,其良率也正好处在从低到高上升的过程中,这就是为什么这些厂商总是先启用较新制程技术的原因。所以最先到达我们分析室的产品总是来自这类厂商的。比如2002年130nm时代的Altera Stratix,2004年90nm时代的Altera Stratix II,再早的还有栅触点距为530nm的Altera Stratix,采用了多晶硅栅极掺钴技术制作栅极,相比之下Stratix II 的栅触点距则为370nm。

Altera Stratix II 90 nm Transistor - TEM

1- 28nm HPL篇:Xilinx XC7K325T Kintex-7

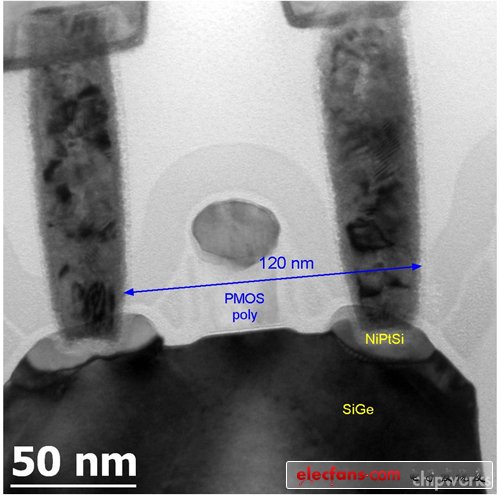

最先到达我们实验室的台积电28nm产品是Xilinx XC7K325T Kintex-7。我们曾在2011年的7月份发布了有关的研究报告。XC7K325T基于台积电28nm HPL技术,金属互联层数为11层。台积电在这种HKMG晶体管的沟道上实施了晶向工程,通过旋转晶圆将沟道的晶向变为《100》,以增加PMOS晶体管的性能,不过在PMOS管的漏源极中并没有使用嵌入Si/Ge技术。其栅极的金相结构非常类似于Intel的32nm产品,其PMOS栅绝缘层上的金属栅极材料同样是TiN,NMOS同样是TiAlN(请参考我们过去的文章 http://www.cnbeta.com/articles/148803.htm)。栅绝缘层中的high-k层部分采用铪基氧化物制造,high-k层下端则铺设硅氧化物层。栅极采用多晶硅栅置换技术制造,即所谓的后栅极技术,与Intel类似。

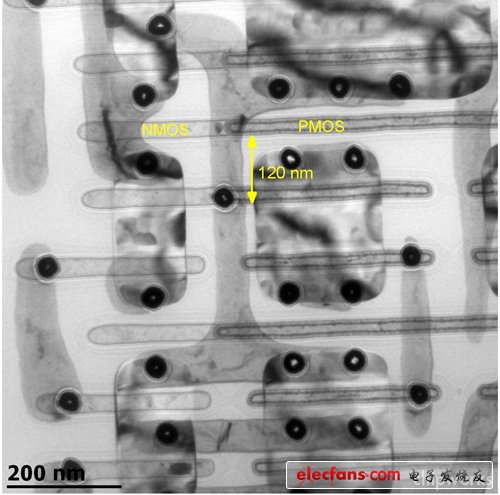

后栅极的制造流程简单说就是先形成多晶硅栅极并完成漏源极退火处理,最后再去掉多晶硅栅,用不同的金属栅极材料先后填充NMOS和PMOS的栅极。XC7K325T的栅触点距为120nm。按照台积电的说法,28nm HPL专门面向高性能,低漏电水平的芯片产品。

Xilinx XC7K325T Kintex-7 TSMC 28 nm HPL - Plan View TEM

2- 28nm HP篇1:Altera 5SGXEA7K2F40C2ES Stratix V

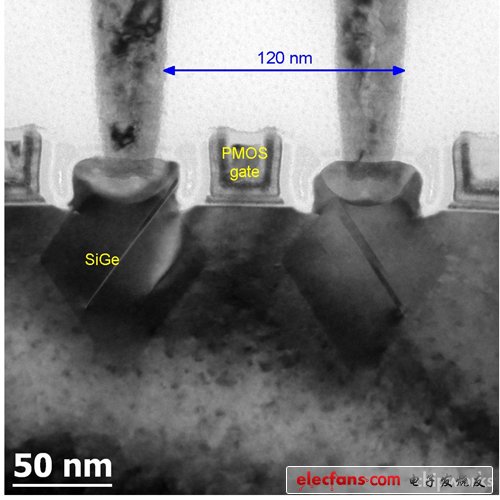

随后我们又分析了另外一款基于台积电28nm制程的产品Altera 5SGXEA7K2F40C2ES Stratix V,我们的报告发布日期是2011年10月份。Altera 5SGXEA7K2F40C2ES Stratix V采用的是台积电的28nm HP制程,这种制程的特点是在PMOS管的漏源极中采用了嵌入式SiGe技术来增加沟道应变,产品的金属互联层数为12层。其栅极结构与28nm HPL制程基本相同,但绝缘层下部的SiO2层厚度相对更薄(1.2nm厚度)以便利于提升性能表现。5SGXEA7K2F40C2ES产品中,晶体管的触点距为120nm。按台积电的说法,28nm HP制程面向的是高速,高性能产品,并宣称该产品比40nm制程产品速度提升45%,而漏电水平则相近。

Altera 5SGXEA7K2F40C2 Stratix V 28 nm HP PMOS - TEM

FPGA产品中的SRAM密度一般不会很高。相比之下AMD和nVidia的图形芯片产品则SRAM密度较高,两家公司也都是台积电28nm制程的先锋人物,他们的图形芯片产品中采用了极大数量的高密度6T-SRAM。我们发现,通常台积电新制程的全部新技术,都是首先完整地应用到AMD/ATI或者nVidia的产品上,当然也包括高密度SRAM。

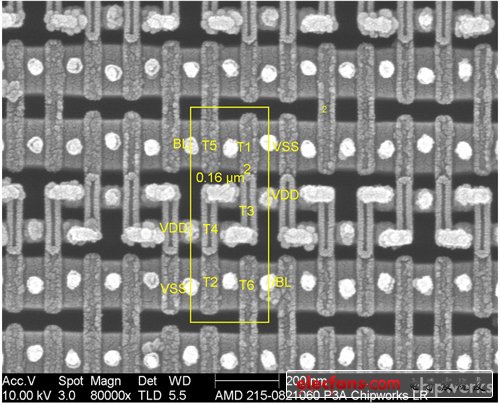

3- 28nm HP篇2:AMD RadeonTM HD 7970

今年早些时候,我们粗略分析了AMD RadeonTM HD 7970 215-0821060图形芯片,这款产品采用的是台积电的28nm HP制程。根据我们的TEM分析结果,215-0821060的晶体管结构与Altera Stratix V 是完全相同的,毕竟两者都基于28nm HP制程。SRAM方面,215-0821060的6T-SRAM单元面积为0.16平方微米,SRAM晶体管采用共轴布置方式。相比之下,90nm制程的ATI 215PADAKA12FG(X1950 Pro)的SRAM单元面积则超过了前者的5倍,为0.86平方微米。

AMD 215-0821060 28 nm HP 6T-SRAM at Poly - Plan View SEM

4- 28nm LP篇:高通MSM8960 Snapdragon S4

2012年早些时候,我们找到了一款使用台积电28nm LP制程技术制造的产品:高通MSM8960 Snapdragon S4,这是一款SOC芯片。28nm LP制程中,采用了多晶硅栅极和漏源极嵌入式SiGe技术(可增加PMOS管的性能)。基于28nm LP制程的产品显然是首款通过台积电所有验证性测试的制程产品。他们宣称28nm LP制程产品成本低,且便于产品快速推出,非常适合需要低待机功耗的产品,如无线基带芯片等。这种制程产品的速度相比40nm制程提升20%,漏电水平则与后者持平。

这款制程产品的栅触点距尺寸为120nm。可以说台积电28nm LP制程基本上是其40nm LP的完全微缩版+嵌入式SiGe漏源极而来。大家都知道台积电40nm LP制程的应用对象之一正是nVidia的Tegra T20-H-A2处理器,其逻辑电路区域的晶体管栅触点距为160nm。

Qualcomm MSM8960 28 nm LP Snapdragon S3 Transistor Gate - TEM

5- 28nm HPM篇:Apple A6+??

第四也就是最后一种台积电推出的28nm制程则是HPM制程。这种制程面向移动应用,因此主要的需求是拥有高性能的同时,功耗表现也要有所改善

。台积电宣称HPM的运行速度要高于HP,而漏电水平则可与LP制程齐平。因此这种制程很适合从网络,平板产品,到移动消费级产品等。目前还没有基于HPM制程的产品面世。不过透露一下,我们很快就会弄到一块这样的样品--这块样品很可能是Apple A6的升级产品

-

[转]台积电借16nm FinFET Plus及InFO WLP 通吃英特尔苹果2014-05-07 0

-

论工艺制程,Intel VS台积电谁会赢?2016-01-25 0

-

台积电5nm架构设计试产2019-04-24 0

-

什么是Altera最新28nm FPGA技术?2019-08-21 0

-

请问C2000系列产品的制程是45nm还是28nm?2020-06-17 0

-

MLCC龙头涨价;车厂砍单芯片;台积电28nm设备订单全部取消!2023-05-10 0

-

Global Foundries公司展示28nm制程芯片硅圆2010-01-13 2039

-

中国28nm制程会被美国卡脖子吗?2021-06-21 6859

-

IP_数据表(I-2):Combo PHY for TSMC 28nm HPM2023-03-16 221

-

IP_数据表(I-1):Combo Serdes PHY for TSMC 28nm HPM2023-03-16 193

-

IP_数据表(Z-1):GPIO for TSMC 28nm HPM/HPC/HPC+2023-03-16 171

全部0条评论

快来发表一下你的评论吧 !