基于FPGA的多普勒测振计信号采集与处理系统设计方案

FPGA/ASIC技术

描述

0 引言

传统的浅海地形测量以船只为平台,采用声纳技术进行,这种测量方法对于一些船只难以驶入的区域便形成了测量盲区,而机载平台与光声浅海测量技术的结合克服了这一缺点,大大提高了测量区域的范围。基于激光多普勒测振技术的声光耦合系统是光声浅海地形遥感系统的重要组成部分,包括激光多普勒测振系统、水面反射光自适应跟踪系统以及可调水平平台三个部分。激光多普勒测振系统能够应用多普勒效应,利用激光的高相干性测量光声浅海地形遥感系统中水表面的振动速度,进而获得水中的声信息。该声信息的采集和进一步处理正是通过基于FPGA 的信号采集与处理系统实现的。

针对遥感系统的工作环境特点、待处理信号的频谱特征以及系统信噪比等要求,综合比较多种信号采集系统方案的优缺点,本文提出了一种基于FPGA的激光多普勒测振计信号采集与处理系统的设计方案,该方案可以实现光声浅海地形遥感探测中的水声信号的实时采集与处理。

1 系统总体结构

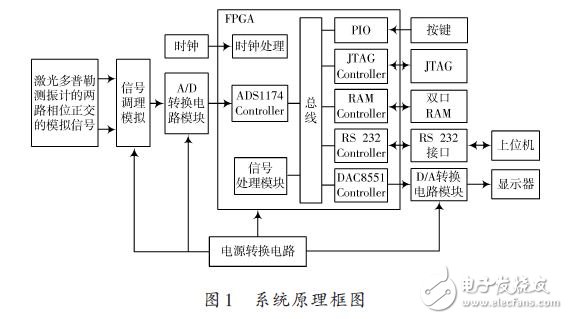

激光多普勒测振计信号采集与处理系统要求既要具有高速实时的采集和处理能力,也要具有丰富的外部接口,同时,考虑到系统稳定性和灵活性的要求,采用核心板和底层板结合的硬件结构。系统原理框图如图1所示,FPGA 芯片采用Atera 公司的Cyclone Ⅱ 系列EP2C5Q208C8N,它采用90 nm 工艺,具有4 608个逻辑单元。此外,系统还包括信号调理模块、A/D转换电路模块、D/A 转换电路模块和外部接口单元等部分组成。

系统采用±15 V 电源供电,选用多块电压转换芯片,提供5 V,1.8 V,3.3 V和1.2 V电压。

2 信号采集和处理系统设计

2.1 硬件电路设计

激光多普勒测振计信号采集与处理系统采用核心板和底层板结合的硬件结构,核心板主要包括FPGA芯片、串行配置芯片(EPCS)、联合测试调试接口(JTAG),其通过108个引脚插针与底层板插座一一对应连接。

底层板电路主要包括电源转换电路、信号调理电路、A/D转换电路、D/A转换电路和串行通信转换电路。

电源转换电路通过7805 稳压芯片、AMS1117 稳压芯片和LM1085稳压芯片实现电源电压的转换,为系统提供5 V,1.8 V,3.3 V 和1.2 V 电压。信号调理电路模块包括两路差分放大电路,每路差分放大电路由一片高性能的全差分音频运算放大器芯片OPA1632 构成。A/D 转换电路模块是在四通道16 位求和型模数转换芯片ADS1174、稳压芯片REF1004 以及集成运放芯片OPA350的基础上实现的,高速状态下,ADS1174芯片速度可以达到52 KSPS,并支持多通道并行处理。采用DAC8551 和REF02 稳压芯片实现D/A 转换,DAC8551是一款16 位电压输出模数转换芯片,REF02 稳压芯片为DA芯片提供2.5 V的参考电压。由于RS 232在通信领域的广泛应用,本文设计系统采用RS 232 串行方式进行通信,考虑到激光多普勒测振计信号采集与处理系统中FPGA 接口电路是TTL 电平,所以需要经过MAX3232芯片实现与RS 232标准电平的转换。硬件电路板如图2所示。

2.2 FPGA逻辑设计

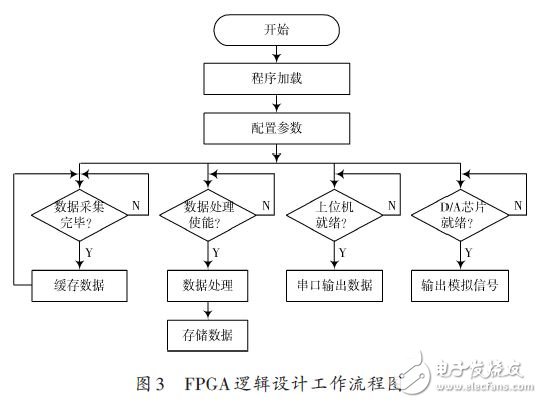

在FPGA逻辑设计中,采用Altera公司的Quartus Ⅱ综合开发环境对FPGA进行设计、仿真和调试,实现信号的采集和处理功能,FPGA逻辑设计工作流程图如图3所示。

在工作过程中,FPGA首先检测是否接收到数据采集完毕的使能信号,如果没有接收到就一直进行检测,如果收到就读取16 位数据并缓存。当FIFO 接近全满状态时启动数据处理逻辑,数据处理逻辑通过一系列乘加运算结合流水线的设计方法实现,并将运算结果适当截位输出给双口RAM.双口RAM 拥有两套完全独立的数据线、地址线和读写控制线,当检测到有数据输入时,读地址开始加1,否则读地址保持不变。上位机准备就绪,即双口RAM 数据准备输出时,双口RAM 写地址开始加1,通过串行接口将数据输出。在输出模拟信号时,只有当DAC8551芯片输入寄存器接收到24位数据,同时同步信号为低电平时,才能启动 D/A转换逻辑。

下面将介绍几个典型数字逻辑模块的关键设计点。

(1)时钟模块

本设计中外部晶振提供给FPGA的时钟为50 MHz,时钟模块的功能就是根据设计要求,利用锁相环以及使能时钟的设计方法为各个模块提供所需的时钟信号。通过锁相环配置工具将50 MHz的系统时钟进行1/2分频,从而产生频率为25 MHz并满足时序约束的主时钟。使能时钟设计,即不增加新的时钟,而只是利用原有主时钟,让分频信号作为使能信号来使用,通过该设计对主时钟进行1/16 分频,为信号处理模块提供工作时钟。

(2)A/D逻辑模块

A/D 逻辑模块的任务是根据ADS1174 的转换时序图,在芯片的引脚发出或接收相应的信号,使得ADS1174完成启动、配置和数据读取操作。其控制操作如下:首先配置ADS1174 的相关参数,包括运行模式、接口类型等,然后通过查询ADS1174的DRDY信号来判定数据转换是否完成,开始读取数据,最后将读得数据进行串并转换,同时完成数据的缓存。A/D逻辑模块每完成一次信号采样,则等待下一次触发脉冲的到来。

(3)数据处理模块

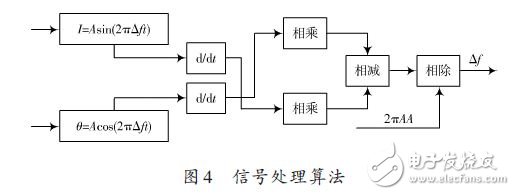

数据处理模块的功能是提取出多普勒测振计信号中的频移信号,本设计采用如图4 所示的信号处理算法,通过微分和乘加运算,同时结合流水线的设计方法来实现。微分运算的处理是将前一个数据延迟一个单位时间,用当前的数据减去前一个数据得到的。通过宏模块构建16 b × 16 b有符号乘法器来实现乘法运算,同时为了避免溢出,对乘法运算结果适当截位。相关除法器操作则与乘法器类似。

(4)双口RAM模块

本文设计中双口RAM 用于存储经过处理的数据,一方面通过RS 232 接口提供给上位机操作,另一方面通过DAC8551转换成模拟信号。双口RAM拥有两套完全独立的数据线、地址线和读写控制线,并允许两个独立的系统或设备同时对其进行随机性访问。该双口RAM 模块是通过调用Quartus Ⅱ自带的参数化模型库实现的,容量为4 KB.

(5)数据通信模块

RS 232采用的是异步通信协议,基本的异步通信只需包括通信发送端和通信接收端两根信号线。该模块由三个子模块组成:波特率发送器模块、数据发送模块、数据接收模块。波特率发生器模块主要用于产生接收模块和发送模块的时钟频率,其实质是一个分频器,数据接收模块的作用就是将接收到的串行数据转换成并行数据并输出,数据发送模块的作用相当于一个移位寄存器,其功能就是按照一定的波特率将移位寄存器中的数据一位一位移出。数据收发过程是通过状态机实现的,设计中波特率发生器模块的输出时钟为实际串口数据波特率的16倍,当输入线路逻辑发生跳变时,开启采样计数器,当计数器计数到起始位数据中间时刻时即可认定接收到的数据是起始位数据,依次类推,只有计数器计数到每个数据的中间位置时才开始采集该数据。

3 仿真验证

激光多普勒测振计信号采集与处理系统采用MentorGraphics公司Modelsim软件进行仿真验证。数据通信模块仿真波形如图5所示。其中,first发生跳变会引起数据发送使能信号的翻转,从而给UART传输系统中数据发送模块一个使能信号。clk16x_rx,clk16x_tx是由波特率发送器产生的16倍于系统时钟的信号,分别作用于数据接收模块和数据发送模块。按照时间顺序由低字节到高字节发送一帧数据0,1,0,0,1,1,1,0,1,1,当数据发送使能信号低电平有效时,被采样的数据经由数据发送模块发送出来。由此证明数据通信模块能够正常工作。

系统仿真波形如图6 所示。dina,dinb 是由计算机随机产生的两路多普勒正交信号,经过ADS1174 模数转换输出给FPGA,经过信号处理模块、双口RAM 模块以及DA控制模块,从dout口输出给DAC8551芯片进行数模转换。

4 结语

本文主要提出了一种基于FPGA的多普勒测振计信号采集与实时处理的信号采集系统的设计方案,采集系统采样精度为16 b,每路采样速率为50 KSPS,两路信号经过FPGA 处理后解调出多普勒频移信息,处理后的数据存储在双口RAM 中,通过RS 232接口快速传输至上位机或者数模转换成模拟信号输出。测试表明该设计方案能够保证设计要求的采样速度和精度,对于信号的实时解调和处理具有实际应用价值。

-

一种脉冲多普勒引信数字化信号处理系统2016-12-23 904

-

采用FPGA实现多普勒测振计信号采集系统设计2019-06-24 0

-

一种基于FPGA的振动信号采集处理系统设计介绍2019-07-01 0

-

一种基于FPGA和DSP的高速数据采集设计方案介绍2019-07-05 0

-

有关彩色多普勒信号处理中的DSP器件如何选型2020-06-15 0

-

求一种多路模拟数字采集与处理系统的设计方案2021-04-28 0

-

基于FPGA 的交流信号采集与处理系统2009-05-16 490

-

基于FPGA的多路模拟量、数字量采集与处理系统2009-06-20 1574

-

基于FPGA的实时信号处理系统设计方案2011-09-14 1217

-

基于FPGA多路机载冗余图像处理系统的设计方案2014-01-07 2907

-

基于FPGA的雷达信号处理系统设计2015-10-30 887

-

地面脉冲多普勒雷达信号处理系统方案2016-12-26 685

-

基于LabVIEW的信号采集处理系统_金爱娟2017-03-18 768

-

基于FPGA的振动信号采集处理系统设计并实际验证2017-11-18 3341

-

FPGA信号处理系统的散热解决方案介绍2019-04-23 3529

全部0条评论

快来发表一下你的评论吧 !