参考时钟对SERDES性能的影响

FPGA/ASIC技术

192人已加入

描述

我们知道,SERDES对参考时钟有严格的相位噪声性能要求。通常,SERDES供应商会根据其SERDES采用的PLL以及CDR架构特点,以及性能数据,提出对参考时钟的相位噪声的具体要求。这个要求,通常是以不降低其SERDES性能为依据的,一般情况下较严。那么,是不是一点也不能违背呢?作为供应商,总是希望有较好的参考时钟,这样系统余量最大。但作为用户,总是希望用便宜的参考时钟,满足需要并有一定余量就行。这就要求在工程实践中作某种平衡,你需要对系统指标要求,SERDES性能有非常清楚的了解。

比如:XILINX 7系列SERDES的CPLL对参考时钟的相位噪声要求如下:

Ref Clock Freq (MHz)

Phase Noise at Offset Frequency ? (dBc/Hz)

10KHz

100KHz

1MHz

100

-126

-132

-136

125

-123

-131

-135

156.25

-121

-129

-133

250

-119

-126

-132

312.5

-116

-124

-131

625

-110

-119

-127

用户设计需要跑XAUI协议,由于XAUI接收机的CDR的抖动容限拐点大约在1.87MHz。因此,参考时钟的1MHz以下的相位噪声可以适当放宽。

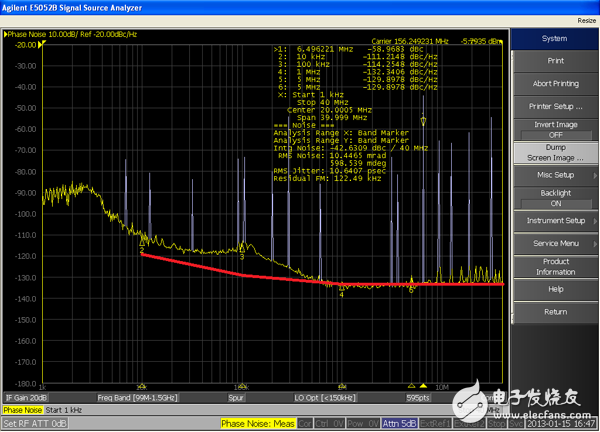

Case 1:

参考时钟的相位噪声在1MHz以下已经不满足模板的要求,但1MHz以上本底噪声有较大余量,很少的杂散有少量超标。这是可以接受的,并且在工程实践上,也是成功的,全面满足了用户的系统要求。

Case 2:

参考时钟的相位噪声在1MHz以下已经不满足模板的要求,且1MHz以上本底噪声也没有余量,杂散严重超标。这是不可以接受的,并且在工程实践上,也造成了收发两个方向上的误码。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

请教关于C6678的serdes模块2018-08-06 0

-

SERDES接口电路设计2019-05-29 0

-

SERDES传输和引脚关联2020-03-17 0

-

Nautilus UDI方案是如何实现高速SerDes测试的?2021-05-10 0

-

SerDes知识详解 精选资料推荐2021-07-28 0

-

SerDes是怎么工作的2021-07-28 0

-

怎样去设计SerDes2021-10-18 0

-

SERDES在数字系统中高效时钟设计方案2012-02-16 5524

-

SERDES数字系统高效时钟设计解析2017-10-26 859

-

基于SERDES时钟的频率跟随的设计2017-11-18 6024

-

为56G/112G SerDes选择XO/VCXO时钟参考时的设计考量2020-11-03 2679

-

单通道56G的SERDES,参考时钟如何选取?2020-11-12 4312

-

SERDES的优势 SERDES演变的看法2021-07-23 3935

-

什么是SerDes?SerDes的应用场景又是什么呢?2023-06-06 6257

-

SerDes是怎么设计的?(一)2023-10-16 766

全部0条评论

快来发表一下你的评论吧 !