时钟采样系统减少抖动性能

模拟技术

描述

很多人都知道,抖动(这是时钟边沿不确定性)是不好的现象,其不仅可导致噪声增加,而且还会降低数据转换器的有效位数 (ENOB)。

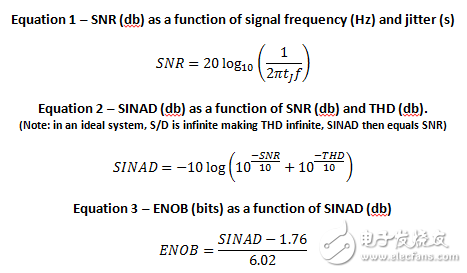

例如,如果系统需要 100MHz 14(最小值)位的 ENOB,我们就需要抖动小于 80 飞秒的时钟!这可通过假设一个无失真的理想系统进行计算,让 SINAD 和 SNR 数值相等(见公式 2)。

接下来,使 ENOB 等于 14,我们可在大约 86db 下计算出最小 SNR。将结果带入公式 1,计算出大约为 80fs 的 tJ 值。

在数字信号处理过程中,采样时钟与处理时钟之间需要有一定关联。也就是说,无论是在十分之一速率下还是在全速率下采样,样片都必须在其速率的倍数下进行处理,而且要相位一致。这就需要一个“主”时钟,其可用来衍生系统中的所有其它时钟。

您可使用温度补偿晶体振荡器 (TCXO) 和低相位噪声 PLL 实现这一点,可将主时钟显著增加至更高的频率。然后,您可对该最新高频率时钟进行下分频,以提供都与主时钟相关联的剩余系统时钟。这样,采样时钟以及各种数字处理时钟都相互具有关联性。

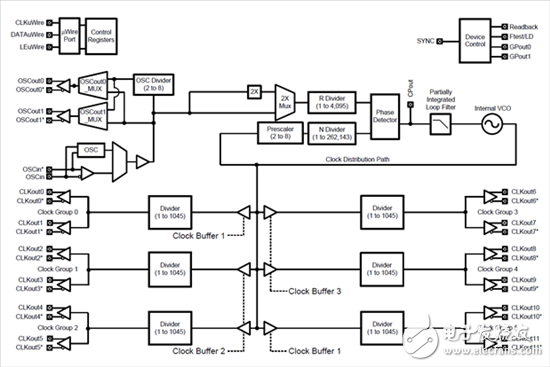

现在有很多时钟解决方案,但很多都需要时钟缓冲器或其它时钟分配方法,其可降低整体抖动性能。您可使用如 LMK03806 等一款器件来克服这个问题,其在同一器件中整合了所有主时钟发生器和时钟分配功能(带驱动器),如图 1 所示。该器件可在 300MHz 下运行的同时,具有不足 50fs 的 RMS 抖动(1.875MHz 至 20MHz)。此外,您还可通过对输出进行编程来支持 LVDS、LVPECL 或 LVCMOS 并对其进行同步,以获得共用上升沿。

图1 —LMK03806(具有时钟发生器、时钟分频器和驱动器)的方框图

因此,您下次设计采样系统时,别忘了考虑时钟抖动性能,因为这会影响整体动态范围。

其它资源:

阅读我们的最新博客系列《定时决定一切》,掌握更多时钟技巧,如如何测量抖动以及如何使用分数 PLL 创建调制波形等;

观看《如何测量扇出缓冲器中的附加抖动》视频;

进一步了解我们面向无线及有线通信、工业以及汽车应用的时钟产品系列。

-

时钟采样系统的抖动性能2018-09-13 0

-

设计时钟采样系统时有没有最大限度减少抖动的办法?2021-04-06 0

-

如何设计并实现一种高性能中频采样系统?2021-04-07 0

-

如何实现低抖动采样时钟电路的设计?2021-04-14 0

-

时钟采样系统如何最大限度减少抖动2022-11-21 0

-

高速ADC的低抖动时钟设计2009-11-27 543

-

AN-756:采样系统以及时钟相位噪声和抖动的影响2010-11-27 742

-

高性能中频采样系统的设计与实现2010-12-07 486

-

采样系统典型结构图2009-01-08 1431

-

如何估算采样时钟抖动2012-04-01 1695

-

时钟抖动和相位噪声对采样系统的影响2012-05-08 1211

-

基于FPGA的高速多通道AD采样系统的设计与实现_徐加彦2017-01-18 647

-

如何去正确理解采样时钟抖动(Jitter)对ADC信噪比SNR的影响2021-04-07 7534

-

时钟采样系统最大限度减少抖动2022-11-04 268

全部0条评论

快来发表一下你的评论吧 !