4 个基本技巧帮助您避免传导 EMI 问题

电源设计应用

描述

以下这4 个基本技巧可帮助您减少涉及EMI 合规性时为您带来的烦恼。当然,EMI 主题非常广泛,会涉及很多其它技巧。

回顾第 1 部分()的讨论内容,在该部分我们重点讨论了当电源中的组件寄生电容直接耦合至电源输入电线时会发生的情况。现在,我们来看看共模 EMI 问题的最常见来源:电源变压器。

该问题由一次绕组和二次绕组间的寄生电容以及一次绕组的高 dV/dt 引起。这个绕组间的电容可起到充电泵的作用,导致杂散电流流到通常连接至接地的二次侧。这里有四个可最大限度减少该问题的常见技巧。

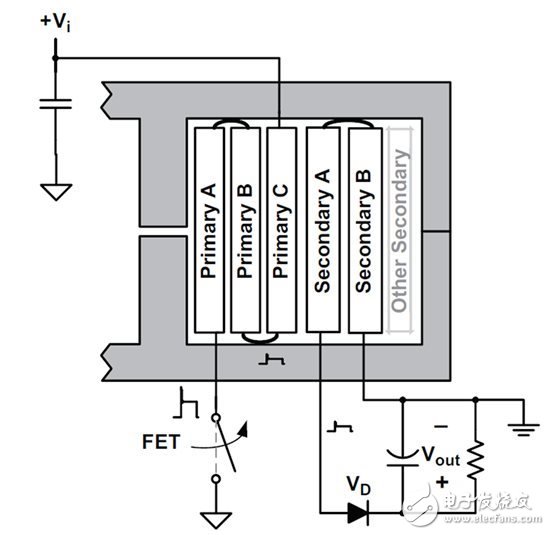

进行一次绕组,使最高dV/dt 出现在外层上。电压电势会随每个匝数变化。例如在反激拓扑中,最大的电压摆幅出现在连接 FET 漏极的一端(见图 1)。让“静音”层临近最近的二次层,可最大限度地降低在整个绕组间电容上出现的 dV/dt。采用这种技术,应该明确外部绕组可能已成了有问题的噪声源,其可能会耦合至变压器附近的其它目标。外部绕组周围可能需要一个屏蔽绕组。

在一次绕组和二次绕组之间使用一个屏蔽绕组。插入一个一端连接至输入或输入返回端的单层绕组,可使杂散电流离开二次绕组并返回至源头。这种技术的代价是略微增加了变压器的设计复杂性,并增加了漏电感。

在一次接地到二次接地之间使用一个“Y 电容器”。该电容器可为杂散电流提供一个回到一次接地的较低阻抗路径。电源中的这条本地路径可防止这些电流找到另外一条通过接地回到源头的路径。但是,对于能使用多大的电容,这里有一定安全限制。

添加一个共模线圈。有时候所提到的其它技术不足以将 EMI 降低到所需水平之下。添加一个共模线圈,不仅可增加共模阻抗,而且还对降低传导噪声非常有效。但这样会产生附加组件成本。在选择共模线圈时,要注意检查相对于频率的阻抗曲线。在某种情况下,所有线圈都会因其自身的绕组间电容问题而转变成电容性。Robert Kollman 有一篇关于该主题的优异文章。

查看这个来自 PowerLab 的设计,了解部分这些技术的实施实例……

PMP9144 — 通用 AC 输入、14V/2.4A 反激方案支持 88% 的效率

图1. 绕组上的电势随每个匝数变化。(本图片来自 2010 年德州仪器电源设计研讨会主题 1《反激 SMPS 设计介绍》,作者 Jean Picard。这是一篇优异的反激设计参考资源文章。)

-

传导式EMI 的测量技术2009-05-15 0

-

EMI干扰 :传导是罪魁祸首2012-11-15 0

-

资深工程师电源设计策略:如何避免传导EMI问题2014-07-30 0

-

如何避免传导EMI问题(资深工程师电源设计资料)2016-01-14 0

-

避免传导EMI问题的4个基本技巧2018-09-14 0

-

如何避免传导EMI问题2018-09-14 0

-

哪里可以做EMI传导测试2020-04-15 0

-

介绍不同类型的传导干扰、EMI 规定和传导 EMI 测量2021-12-28 0

-

传导式EMI的测量技术2009-05-15 860

-

PowerLab 笔记:如何避免传导 EMI 问题2017-04-18 690

-

传导式EMI对PCB有什么影响?如何测量传导式EMI限制规定?2018-09-10 754

-

PowerLab 笔记:如何避免传导EMI的问题2021-11-10 159

-

PowerLab 笔记:如何避免传导 EMI 问题 — 22022-11-04 181

-

PowerLab 笔记:如何避免传导 EMI 问题 — 12022-11-04 181

全部0条评论

快来发表一下你的评论吧 !