资料下载

Taking the Hard Line

Taking the Hard Line

作为一个“海的大门”,FPGAs提供了一个几乎无限的平台,任何数字功能,可以实现使用逻辑表达式实现通过查找表的各种宽度。自成立以来,这提供了一个前所未有的灵活性,而其均匀阵列结构提出了他们的最新的工艺节点的早期采用者。

尽管不断地在半导体技术的领先优势,性能仍然是一个限制因素,在一个架构,依赖于日益复杂的路由模式和时钟结构;正是因为这一原因,厂商第一次实现关键功能使用硬连接块的知识产权(IP)。

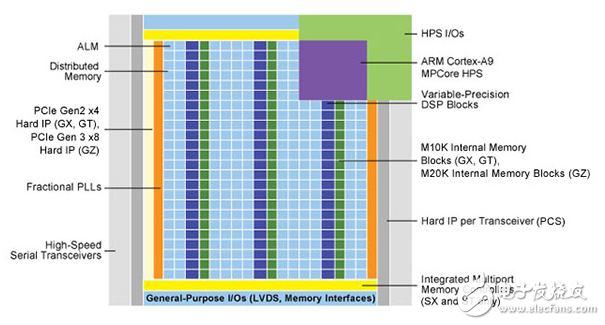

不竭的需求,更高的性能和最佳的功耗,推动FPGA供应商整合越来越多的固定功能IP到他们的产品。而中坚可以看到这是FPGA技术的核心利益的侵蚀,事实上它提供的功能互补,将难以或无法实现的逻辑结构。

One of the core markets for high-end FPGAs has always been telecommunications; here, performance is key and cost can be secondary. To meet this demand, FPGAs now integrate a large amount of IP targeting the data path, such as high-speed Ethernet, as well as other serial transceivers and, most recently, optical interfaces. These sit beside other performance-critical functions such as PLLs and DSP blocks. The ability to add a soft-core processor to handle control path functions means large FPGAs are still very popular in this field, often being preferred over ASICs.

While soft cores can tackle many tasks, particularly in the latest and fastest FPGAs, they remain limited and may not be suitable for other tasks where performance is important. Consequently and somewhat naturally, the extension of IP integration saw the introduction of ‘hard’ processor cores; a concept that has taken several iterations to fully realize but is now making a significant impact in many application areas.

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章