资料下载

单片机STM8S105K6T6C贴片机原理

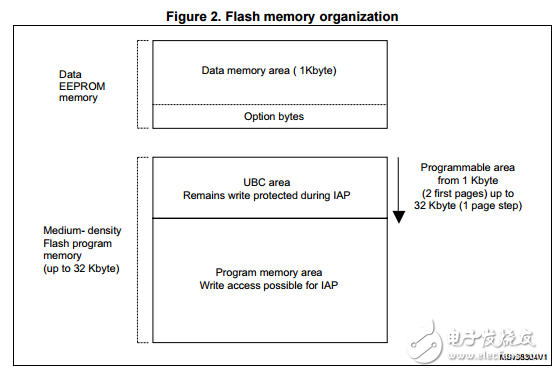

Features Core 16 MHz advanced STM8 core with Harvard architecture and 3-stage pipeline Extended instruction set Memories Program memory: up to 32 Kbyte Flash; data retention 20 years at 55 °C after 10 kcycle Data memory: up to 1 Kbyte true data EEPROM; endurance 300 kcycle RAM: up to 2 Kbyte Clock, reset and supply management 2.95 to 5.5 V operating voltage Flexible clock control, 4 master clock sources – Low power crystal resonator oscillator – External clock input – Internal, user-trimmable 16 MHz RC – Internal low-power 128 kHz RC Clock security system with clock monitor Power management: – Low-power modes (wait, active-halt, halt) – Switch-off peripheral clocks individually Permanently active, low-consumption poweron and power-down reset

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章