什么是上拉电阻和下拉电阻_上拉电阻和下拉电阻的区别_上拉电阻的作用原理

电子常识

描述

所谓上,就是指高电平;所谓下,是指低电平。上拉,就是通过一个电阻将信号接电源,一般用于时钟信号数据信号等。下拉,就是通过一个电阻将信号接地,一般用于保护信号。

这是根据电路需要设计的,主要目的是为了防止干扰,增加电路的稳定性。

假如没有上拉,时钟和数据信号容易出错,毕竟,CPU的功率有限,带很多BUS线的时候,提供高电平信号有些吃力。

而一旦这些信号被负载或者干扰拉下到某个电压下,CPU无法正确地接收信息和发出指令,只能不断地复位重启。

假如没有下拉,保护电路极易受到外界干扰,使CPU误以为被保护对象出问题而采取保护动作,导致误保护。

上拉下拉,要根据电路要求来设置。

上拉电阻一般是一端接电源,一端接芯片管脚的电路中的电阻,下拉电阻一般是指一端接芯片管脚一端接地的电阻。

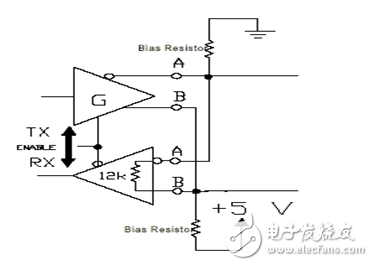

如下图的两个Bias Resaitor 电阻就是上拉电阻和下拉电阻。图中,上部的一个Bias Resaitor 电阻因为是接地,因而叫做下拉电阻,意思是将电路节点A的电平向低方向(地)拉;同样,图中,下部的一个Bias Resaitor 电阻因为是电源(正),因而叫做上拉电阻,意思是将电路节点A的电平向高方向(电源正)拉。当然,许多电路中上拉下拉电阻中间的那个12k电阻是没有的或者看不到的。我找来这个图是RS-485/RS-422总线上的,可以一下子认识上拉下拉的意思。但许多电路只有一个上拉或下拉电阻,而且实际中,还是上拉电阻的为多。

上拉下拉电阻的主要作用是在电路驱动器关闭时给线路(节点)以一个固定的电平。

1 在RS-485总线中,它们的主要作用就是在线路所有驱动器都释放总线时让所有节点的A-B端电压在200mV或200mV以上(不考虑极性)。不然,如果接收器输入端A和B间的电平低于±200mV(绝对值小于200mV),接收器输出的逻辑电平将被当作所传输数据的末位而被接收起来,这样显然是极容易产生通讯错误的。

2 最容易见到的上拉电阻应当是NE555电路7脚作为输出用的时候。实际上,它和一个三极管的C极或MOS管的D极有一个电阻接到电源+上是一样道理的。它的作用就是:当管子(晶体管或MOS管)输入关断电平时,C极或D极有一个高电平(空载时约等于电源电压);当管子(晶体管或MOS管)输入导通电平时,C极或D极将与电源地(-)接通,因而有一个低电平。理想的应为0V,但因为管子有导通电阻,因而有一定的电压,不同的管子可能不一样,相同的管子也可能因参数差异而小有差别,即便是真正的金属接触的电源开关,也是有接触电阻/导通压降(虽然不同电流下压降不同)的;仅仅就导通而言,对于不同系列的集成电路来说,因为应用对象不同,导通后的输出电压有不同的规定,典型是TTL电平和CMOS电平的不同。这方面超过了本问题的内容,将日志里另外处理。

3 建议:自己实验或用仿真软件看看。

上拉电阻和下拉电阻的区别

上拉电阻和下拉电阻2者共同的作用是:避免电压的“悬浮”,造成电路的不稳定;

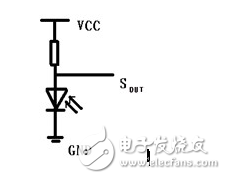

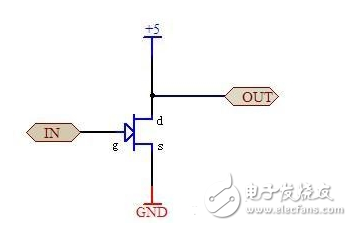

一、上拉电阻如图所示:

1、概念:将一个不确定的信号,通过一个电阻与电源VCC相连,固定在高电平;

2、上拉是对器件注入电流;灌电流;

3、当一个接有上拉电阻的IO端口设置为输入状态时,它的常态为高电平;

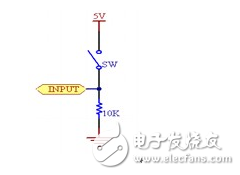

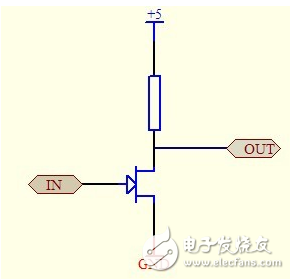

二、下拉电阻如图所示:

1、 概念:将一个不确定的信号,通过一个电阻与地GND相连,固定在低电平;

2、下拉是从器件输出电流;拉电流;

3、当一个接有下拉电阻的IO端口设置为输入状态时,它的常态为低电平;

上拉电阻很大,提供的驱动电流很小,叫弱上拉;反之叫强上拉。

为什么要使用拉电阻:

上拉就是将不确定的信号通过一个电阻嵌位在高电平,电阻同时起限流作用,下拉同理。上拉是对器件注入电流,下拉是输出电流,弱强只是上拉电阻的阻值不同,没有什么严格区分。

对于非OC、OD输出型电路提升电流和电压的能力是有限的,上拉电阻的功能主要是为集电极开路输出型电路输出电流通道。

上拉电阻的主要应用:

1、当TTL电路驱动COMS电路时,如果TTL电路输出的高电平低于COMS电路的最低高电平(一般为3.5V),这时就需要在TTL的输出端接上拉电阻,以提高输出高电平的值。

2、OC门电路要输出“1”时需要加上拉电阻,不加根本就没有高电平。

3、为加大输出引脚的驱动能力,有的单片机管脚上也常使用上拉电阻,但在用OC门作驱动(例如:控制一个 LED)灌电流工作时就可以不加上拉电阻。

4、在COMS芯片上,为了防止静电造成损坏,不用的管脚不能悬空,一般接上拉电阻产生降低输入阻抗,提供泄荷通路。

5、提高总线的抗电磁干扰能力。管脚悬空就比较容易接受外界的电磁干扰。

6、长线传输中电阻不匹配容易引起反射波干扰,加上下拉电阻是电阻匹配,有效的抑制反射波干扰。

上拉电阻阻值的选择原则包括:

1、从节约功耗及芯片的灌电流能力考虑应当足够大;电阻大,电流小。

2、从确保足够的驱动电流考虑应当足够小;电阻小,电流大。

3、对于高速电路,过大的上拉电阻可能边沿变平缓。

综合考虑以上三点,通常在1k到10k之间选取。对下拉电阻也有类似道理。

在很多单片机电路中,其I/O管脚检测信号是以高、低电平来判断是否有信号变化的,比如5V为高电平;0V为低电平。那么这些管脚如果不接上拉电阻的话,其电平信号就可能是随机的了,0V~5V之间不一定是什么状态,这样的话单片机就不能正确地判断是不是有信号电平变化了。因此给I/O管脚上接一个上拉电阻使它的检测信号由不确定电平状态拉到5V电平,单片机就能准确地判断是不是有信号变化了。同理,还有下拉电阻,把不确定电平状态拉到0V,使系统更加稳定。

上拉电阻的作用原理

单片机上拉电阻作用

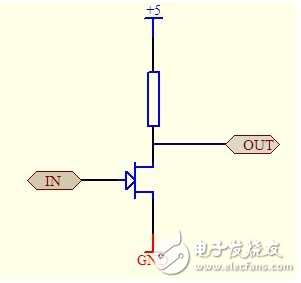

1. 场效应管的漏极开路门电路如下:

图中上拉电阻作用分析如下:

管子导通或截止可以理解为单片机的软件时端口置1或0.

(1)如果没有上拉电阻(10k),将5V电源直接与场效应管相连。

当管子导通时, 管子等效一电阻,大小为1k左右,因此5v电压全部加在此等效电阻上,输出端Vout=5v。

当管子截止时,管子等效电阻很高,可以理解为无穷大,因此5v的电压也全部加在此等效电阻上,Vout=5v。

在这两种情况下,输出都为高电平,没有低电平。

(2)如果有上拉电阻(10k),将5v电源通过此上拉电阻与与场效应管相连。

当管子导通时, 管子等效一电阻,大小为1k左右,与上拉电阻串联,输出端电压为加在此等效电阻上的电压,其大小为Vout = 5v * 管子等效电阻/(上拉电阻+管子等效电阻)=5v * 1/(10+1) = 低电平。

当管子截止时, 管子等效电阻很高,可以理解为无穷大,其与上拉电阻串联,输出端电压为加在此等效电阻上的电压,其大小为Vout = 5v * 管子等效电阻/(上拉电阻+管子等效电阻)=5v * 无穷大 /(无穷大+1) = 高电平。

由(1)和(2),可以分析出等效电阻的作用。

-

110 上拉电阻和下拉电阻车同轨,书同文,行同伦 2022-08-09

-

上拉电阻和#下拉电阻你了解吗jf_97106930 2022-08-27

-

上拉电阻和下拉电阻的作用2008-05-22 0

-

上拉、下拉电阻的作用2012-08-20 0

-

电阻的上拉与下拉作用2018-06-28 0

-

上拉电阻与下拉电阻有什么作用2019-05-20 0

-

上拉电阻和下拉电阻问题2019-06-27 0

-

上拉电阻与下拉电阻的定义及应用2021-10-14 0

-

上拉电阻和下拉电阻是如何确定2021-11-12 0

-

上拉电阻与下拉电阻最基本的作用2021-12-13 0

-

上拉电阻与下拉电阻概述2021-12-13 0

-

上拉电阻和下拉电阻有哪些呢2022-01-14 0

-

理解上拉电阻与下拉电阻的原理与作用2022-01-14 0

-

上拉电阻与下拉电阻怎么接线2022-01-14 0

全部0条评论

快来发表一下你的评论吧 !