资料下载

ADI iCoupler的简介及四通道隔离器ESD测试结果和ESD闩锁考虑因素

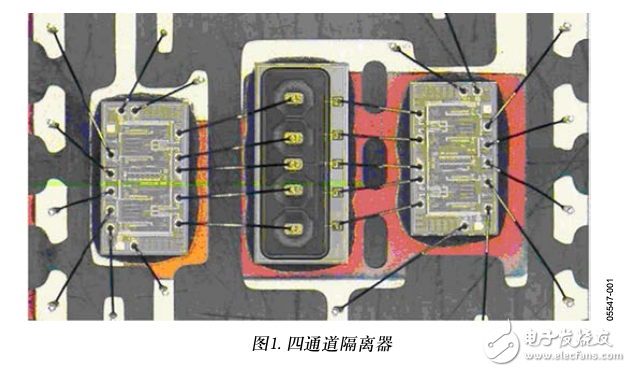

ADI公司的iCoupler®产品提供了一种替代光耦合器的隔离

解决方案,具有出色的集成度、性能和功耗特性。一个

iCoupler隔离通道包括CMOS输入和输出电路与一个芯片级

变压器(见图1)。由于数字隔离器采用CMOS技术,因此在

系统级ESD(静电放电)、电涌电压、快速瞬变或其他过压

条件下,它们容易受到闩锁或ESD的破坏。

本应用笔记提供关于避免这些问题的指南。针对各种系统

级测试配置,本文举例说明了其可能影响性能的机制。针

对每个示例,本文都给出了推荐解决方案。

器件与系统

简单地说,器件是带互连线的单一集成装置,而系统则是

由多个互连器件构建而成的非集成装置。器件与系统几乎

在所有情况下都是泾渭分明。但是,器件测试与系统测试

之间的区别可能并不是那么明显。此外,器件的技术规格

可能并未直接说明它在系统级测试中的表现。ESD测试就

是一个很好的例子。

iCoupler隔离产品的ESD/闩锁考虑因素

ESD、电涌、突波和快速瞬变事件是电气应用中的基本现

实。这些事件一般都含有高压、持续时间很短的尖峰,并

且直接或间接作用于器件。其产生原因是器件与各种实际

现象的交互,如人体接触、交流线路扰动、雷击或系统地

之间的共模电压差等。

为了确定器件在组装成系统之前以及组装过程中被人和自

动化组装设备处理的鲁棒性,器件级ESD测试最为有用。

然而,对于确定器件在系统内遭受系统级ESD事件的鲁棒

性,器件级ESD数据则不太有用。其原因有如下两方面:

• 系统级与器件级ESD测试的目的不同。器件级测试所应

对的情况通常是器件搬运和组装过程中会遇到的情况,

而系统级测试所应对的情况通常是系统运行中会遇到的

情况。

• 器件在系统级测试期间所承受的特定状况可能与它所在

的电路板/模块/系统设计密切相关。例如,系统与器件

地之间的长感性走线对器件造成的电压瞬变,实际上比

它对系统在测试点造成的电压瞬变可能更为严重

CMOS器件中的闩锁

寄生PNP和NPN晶体管是CMOS工艺的固有现象,这些晶

体管会配置为硅控整流器(SCR)。当此寄生SCR被触发时,

就会发生闩锁。该现象会导致VDD与地之间出现低电阻路

径,从而吸取大电流通过器件。这种过大的电流为电气过

应力(EOS)造成破坏提供了可能性。

闩锁可能引起不同程度的破坏,从器件完全损毁到参数性

能下降等。更为有害的是潜在故障,可能影响日后的系统

运行。《模拟对话》杂志刊载了一篇关于闩锁一般问题的

优秀论文,参见Analog Dialogue 35-05 (2001)“打赢对抗CMOS

开关闩锁的战争”。虽然该文主要讨论的是CMOS开关的问

题,但它也普遍适用于所有CMOS器件,包括数字隔离器

产品。

强烈建议所有应用都应使用陶瓷旁路电容,以使VDD与地

之间的电源噪声最小。选择0.01 µF至0.1 µF范围的电容值,

并尽量靠近器件放置。即使有充分的旁路,一些应用可能

仍然会发生闩锁问题。将一个200 Ω电阻与VDD串联也会有所

帮助。在5 V应用中,它可以将电源电流限制在25 mA,低于

闩锁触发电流。不过,根据所吸取电源电流的不同,此串

联电阻可能会将器件引脚的电源电压降至不可接受的水

平。当以高数据速率工作而需要高电源电流时,极有可能

出现这一问题。

导致闩锁的机制通常是过压状况超出器件的绝对最大额定

值(对大多数产品而言是大于7.0 V或小于–0.5 V)。一旦将器

件集成到系统中,过压来源往往不是很清楚。但只要了解

其机制,一般还是能找到解决之道。

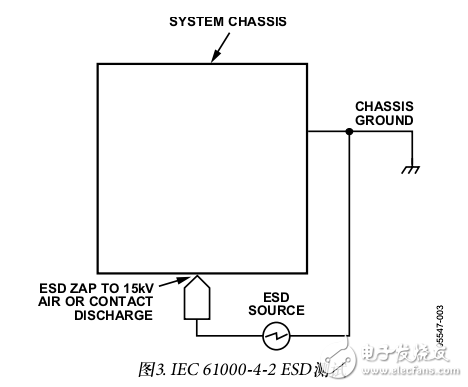

IEC 61000-4-2 ESD测试

IEC 61000-4-2 ESD测试的框图如图3所示。本测试是在系统

机壳上的多个点施加ESD接触或空气放电,因此会有多种

机制可能引起闩锁问题,包括通过地线之一注入电流以及

系统机壳或印刷线路板走线中的ESD电流发生感性耦合

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章