高杂波衰减系统关键性能指标介绍

电子说

描述

作者:Peter Delos和Jarret Liner

1

简介

在雷达应用中,相位噪声是要求高杂波衰减的系统的关键性能指标。相位噪声是所有无线电系统都会关心的问题,但是雷达相比通信系统来说特别要求非常靠近载波频率的频偏位置的相位噪声性能。

这些高性能系统中的系统设计人员将选择超低相位噪声振荡器,并且从噪声角度来讲,信号链的目标就是使振荡器相位噪声曲线的恶化最小。这就要求对信号链上的各种元器件做残余或加性的相位噪声测量。

最近发布的高速数模转换器(DAC)产品对于频率转换阶段需要的任何LO的波形生成和频率创建都非常有吸引力。然而,雷达目标会挑战DAC相位噪声的性能。

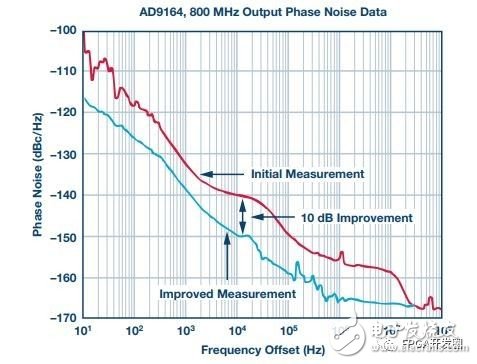

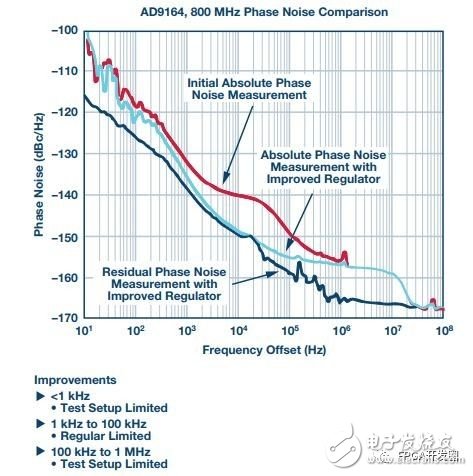

图1. AD9164相位噪声的改进

在本文中,我们将展示AD9164 DAC在10KHz 频偏处超过10dB的改进的测量结果。改进如图1所示,并且我们将会讨论如何通过结合电源稳压器选择和测试设置改进来达到这一结果。

2

相位噪声定义

相位噪声是周期信号过零点偏差的测量。考虑有相位波动的余弦波

相位噪声可以通过相位变化的功率谱密度来确定

就线性而言,单边相位噪声定义为

相位噪声 通常以10log(L(f))的dBc/Hz为单位来表示。然后可以将相位噪声数据绘制到相对RF载波的偏移频率中。

图2. 相位噪声绘图方法

相位噪声进一步的重要定义就是绝对相位噪声和残余相位噪声。绝对相位噪声是系统中测量的总相位噪声。残余相位噪声是测试设备的加性相位噪声。这种区别在测试设置和确定系统中元件级别相位噪声贡献的过程中至关重要。

3

DAC/DDS相位噪声测量方法

本部分图表显示DDS相位噪声测试设置。对于DAC相位噪声测量,可以设想将DAC作为直接数字频率合成器(DDS)子系统的一部分。DDS是通过将与DAC通信的单片IC或FPGA或ASIC中的数字正弦波模式送给DAC来实现。在现代DDS设计中,数字相位误差可以远低于DAC误差,而且DDS相位噪声测量通常受限于DAC的性能。

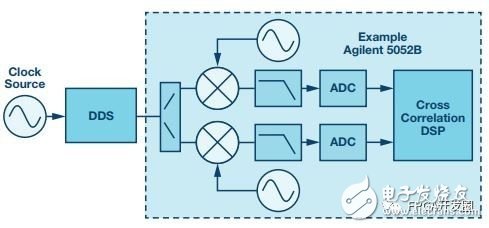

最简单和最常见的测试设置如图3所示。一个时钟源用于DDS并且DDS的输出馈入到一个互相关类型的相位噪声分析仪 。由于只需要一个DDS,所以很容易实现。然而,在这样的测试设置下,没有办法提取振荡器的贡献以便仅仅显示DDS的相位噪声。

图3. 绝对相位噪声DDS测试设置包含DAC和振荡器噪声

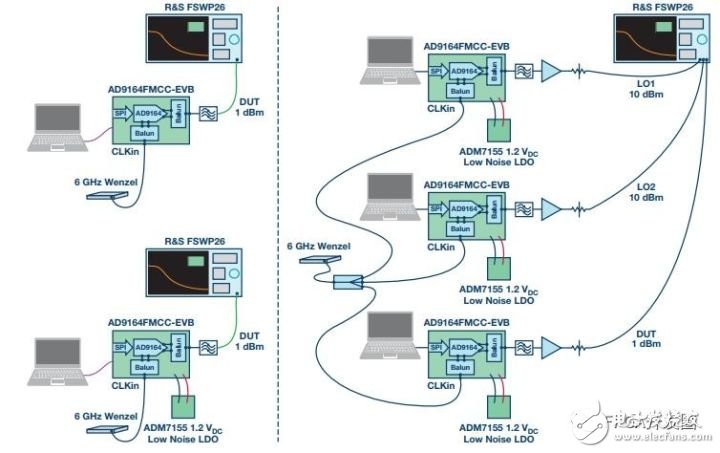

图4显示了两种常用的方法用来从测量中去除振荡器的相位噪声,提供残余噪声测量。这些测量方法的缺点在于,在测试设置中需要额外的DAC。但是,优点是可以应用于系统级分析预算,作为DAC相位噪声贡献的一种非常好的指标。

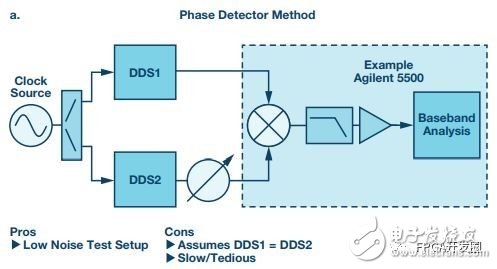

图4a. 使用鉴相器方法的DDS残余相位噪声测量

图4a显示的是鉴相器方法。这种情况下,使用两个DAC,将两个DUT都下变频至DC,可以减去振荡器的贡献。

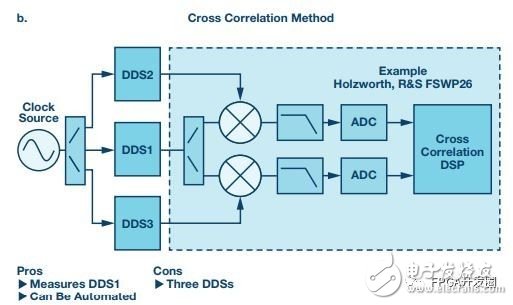

图4b. 使用互相关方法测量DDS残余相位噪声

图4b显示的是使用互相关相位噪声分析的方法。这种情况下,DDS2和DDS3可以用于将时钟贡献转换到测量的LO端口,在互相关算法中去除它们的贡献,并在测量中获取DDS1残余相位噪声。

4

电源噪声贡献

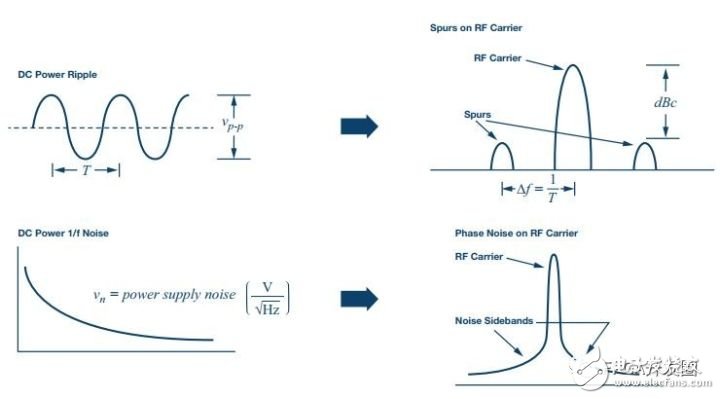

在低噪声模拟和RF设计中,电源噪声是公认需要考虑的因素。电源纹波会周期性的调制到RF载波并在RF载波的频偏等于纹波频率的地方产生杂散。稳压器1/f噪声也会调制到RF载波中,并体现在相位噪声曲线中。图5显示了这些原理。

图5. 电源缺陷调制到RF载波上。

5

测量结果

在研究DAC真正的相位噪声性能的过程中,需要同时考虑测试设置和稳压器的噪声性能。

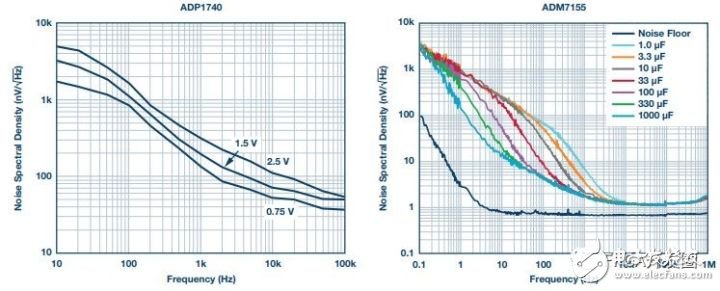

DAC初始评估板包含ADP7140稳压器用于给模拟和时钟提供电压。将噪声谱密度与最近发布的超低噪声稳压器和所选的ADM7155进行对比。图6如产品数据手册所示显示了这些噪声密度的对比情况。电源修改仅将ADM7155用于AD9164时钟(数据手册引脚VDD12_CLK)和模拟电压(数据手册引脚VDD12A)。

接下来,考虑残余相位噪声的测试设置选项。由于实用性和方便性,自带互相关方法的Rohde and Schwarz FSWP成为首选。使用的测试设置如图7所示。

图6. 稳压器噪声密度比较。注意Y轴单位——ADM7155提高了一个数量级

图7. AD9164相位噪声测量的测试设置

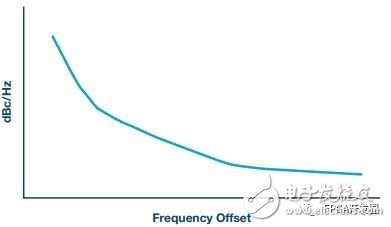

图8. AD9164 800 MHz输出相位噪声比较

图8显示了三种情况的测量结果。红色曲线显示了初始评估板的绝对相位噪声测量结果。浅蓝色曲线也是一种绝对测量结果,但提升了稳压器性能。深蓝色曲线是残余相位噪声测量结果,也提升了稳压器性能。

测量结果指出了在初始研究中并不明显的三种常规的限制区间。低于1 kHz的频率受限于时钟源近载波噪声。1 kHz至100 kHz的频率受限于稳压器选择。高于100 kHz的频率受限于时钟源。由于使用的时钟是用晶体振荡器倍频产生的6GHz,滚降来自于倍频电路中的RF滤波器,因此高于10 MHz的急剧下降来自于时钟源。

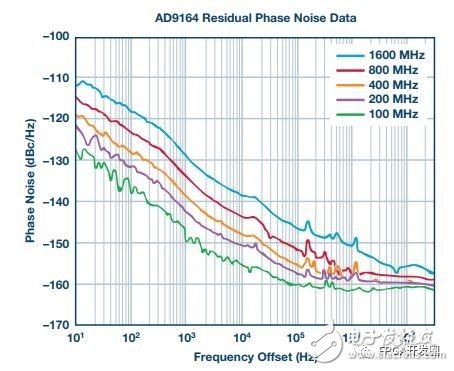

其他的一些DAC频率也使用了提升稳压器性能的残余相位噪声方法进行了测量,图9中概述了部分。这些改进在几个评估板上都做了复现,所有的情况都显示了同样的改进后的结果。

图9. 改进了低噪声稳压器性能的AD9164残余相位噪声测量

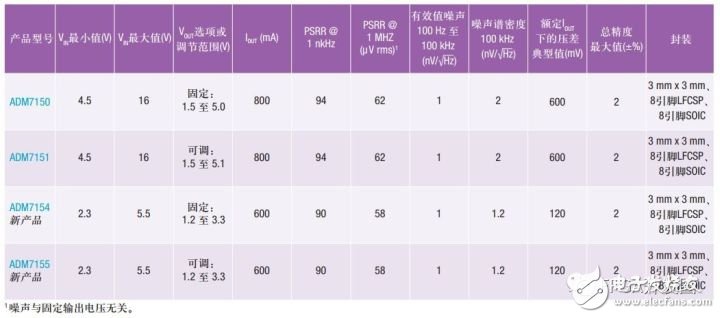

表1. 包含一流的噪声密度性能的稳压器系列

超低噪声稳压器系列的噪声密度相似,如表1所示。正如本文所展示的,稳压器对DAC的相位噪声影响是值得注意的,超低噪声稳压器系列推荐用于任何要求最佳的相位噪声性能的RF系统中。

6

结语

相位噪声基础定义的复习、绝对和残余相位噪声、DAC相位噪声测量测试设置以及稳压器噪声贡献。

本文演示的DAC相位噪声性能改进包含残余相位噪声测量方法和最佳稳压器选择。最终结果是,通过ADI公司的低噪声稳压器系列对模拟电压和时钟电压供电时,AD9164现在可支持超低相位噪声、基于DDS的应用。

-

电性能指标测试2012-08-17 0

-

系统时间响应的性能指标2017-10-12 0

-

TD-SCDMA无线网络关键性能指标测试2019-06-05 0

-

薄膜开关基本类型及性能指标介绍2021-04-15 0

-

频率响应法-- 频域性能指标和时域性能指标的关系2009-07-27 10761

-

检测系统的性能指标2011-03-13 892

-

硬盘性能指标概述2012-05-03 5037

-

选择GPS模块要关注哪些关键性能指标2017-09-04 1088

-

JESD204B发射器的PHY性能的三个关键性能指标详解2017-11-17 5703

-

电缆性能指标测试方法2021-06-22 704

-

通信系统的主要性能指标2023-05-08 5515

-

选择BGA维修设备时,应该关注哪些关键性能指标?2023-06-16 307

-

UPS性能指标介绍2023-12-25 495

全部0条评论

快来发表一下你的评论吧 !