资料下载

×

多核处理器的多路同步时钟信号设计

消耗积分:0 |

格式:rar |

大小:0.2 MB |

2017-10-18

多核处理器是最近快速发展的电子器件,单个芯片内集成了多个同构或者异构的处理器,使得其计算处理能力得到较大幅度的提高。DSP 处理器由于其具有较高的数字处理能力,得到较广泛的应用。多;核DSP芯片以目前性能较高的TMS320C66 系列为例,其中也可以并行TMS320C6678( 以下简称C6678)含有8 个处理器。这些丝处理器可以独立工作,联合工作。当它们联合工作时,相互之间通信和握手就非常重要,尤其是在对时间要求较高的场合,时钟的稳定和同步就非常关键。时钟的稳定和同步对系统设计、时钟源、时钟分配、电路布线、时钟线屏蔽等都提出较高的要求。

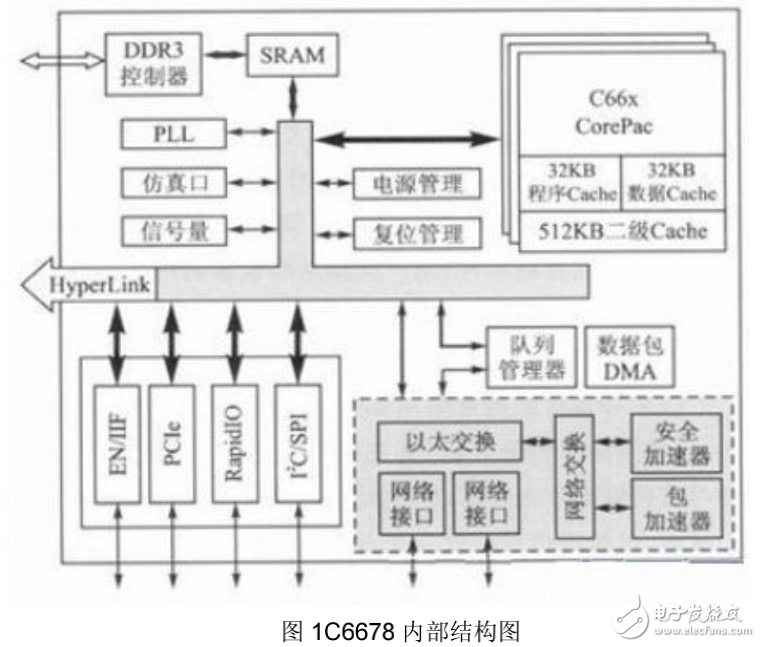

本文利用CDCM6208 时钟分配芯片,以此输出多路时钟,提供到8 核DSP芯片C6678,提供出DSP 核工作时钟、DDR3 数据读时钟、RapidIO 和PCle 数据传输时钟、千兆网络加速器等时钟信号。文中介绍了详细的电路设计、时钟芯片配置以及多核DSP 的配置,相关片内设备的初始化等。1C6678 及其结构C6678 是TI 公司多核处理器中的一款8 核浮点型DSP,最高。工作频率达到1.25GHz,单核可以提供40GMAC 定点计算或者20GFLOP 浮点计算能力,单个芯片可以提供320GMAC 或者160GFLOP 计算能力。C6678 的片内结构如图1所示。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章