资料下载

DSP最小系统设计及基本算法的实现

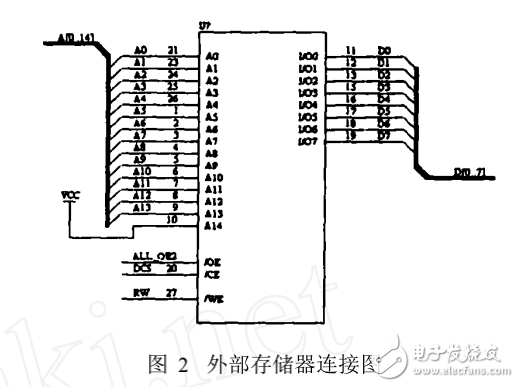

采用先进的修正哈佛结构 , 片内共有 8条总线 (1条程序存储器总线、3条数据存储器总线和 4条地址总线 )、CPU、在片存储器和在片外围电路等硬件 , 使 TMS320VC5402具有功耗小、速度快 (最高可达 100 MHz)、高度并行等优点 , 同时该芯片具有较高的性价比 , 是为实现低功耗高性能专门设计的定点 DSP芯片。对于 DSP芯片外围器件的选择 ,主要包括 A /D、D /A、存储器、接口芯片等。选择A /D采样芯片根据的是 DSP系统处理的模拟带宽 ,A /D采样频率必须服从奈奎斯特采样定理 , 因此A /D、D /A子系统模块选用了 TLC320AC01芯片。为了充分发挥 DSP的高速处理能力 , 应选择存取速率与 DSP相仿的外部存储器 , 因此存储器子系统模块选用 CY7c1021 ( SARAM )芯片和 29EE010(EPROM)芯片以及地址译码用的 xc9536 (CPLD)芯片。UART子系统模块选用 TL16c550c控制芯片和MAX3238电平转换芯片 , 电源和时钟子系统模块选用 73HD318电源转换芯片和 10 MHz晶振。图 1为 VC5402的时钟配置模式表 , 在上电初期 , 可以通过对 VC5402上 3个引脚的不同设置 , 让 DSP工作在不同的时钟频率上 , 也可以在上电后用软件对这 3个引脚对应的位修改配置 , 达到修改 DSP工作频率的目

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章