资料下载

×

关于DSP的高速串行外设接口设计方案分析

消耗积分:1 |

格式:rar |

大小:0.3 MB |

2017-10-24

1 引言

DSP(数字信号处理)的优势除了处理复杂的运算,特别适用于数字滤波、语音、视频、图象处理、通信以及高速实时测控系统中已成为现代信息处理技术的重要器件,极大地促进了信号处理和测控各个领域的学术研究、产品开发及应用。TI公司TMS320LF2407是一种专用定点DSP芯片,与以往的产品相比.最大不同就是有丰富的外设.像SCI、SPI、EV等等.在处理数据优势上添加了事务管理能力。

其中串行外设接口(Serial Peripheral Interface)是Motorola公司提出的一种同步串行外围接口协议.主要应用在EEPROM、FLASH、实时时钟、AD转换器.还有数字处理和数字解码器之间。包括主/从2种模式,具有I/O资源占用少、协议实现简单、传输速度快、能够同时收发信息、支持绝大部分处理器芯片等优点,是一种高速的全双工、同步的通信总线,并且在芯片的管脚上只占用四根线,节约了芯片的管脚.同时为PCB的布局上节约了空间,提供了方便,正是出于这种简单易用的特性,TMS320LF2407芯片也集成了这种通信协议。

2 SPI接口结构和设计原理

2.1 SPI接口结构

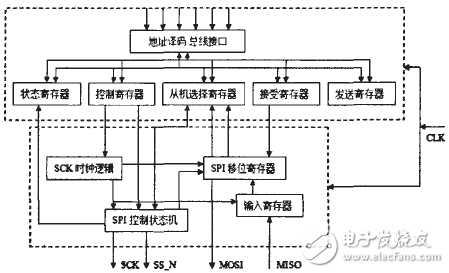

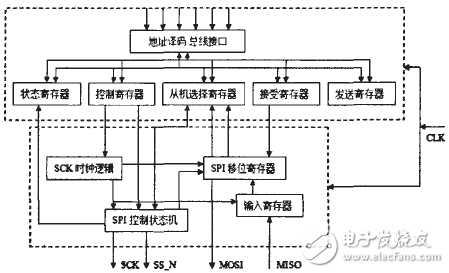

该SPI设计主要有两大部分组成:微控制器接口和SPI控制接口。通过控制线、数据线、和地址线三大总线把微控制接口与SPI控制接口连接在一起,如果外部有更多的SPI接口模块。可以由SPI控制接口运用软件编程与设置,实现扩展具有SPI接口的外部设备。

TMS320LF2407中采用的主从控制器连接通信。主控制器通过输出SPICLK信号来启动数据传送。对主控制器和从控制器.数据都是在SPICLK的一个边沿移出移位寄存器,并在相对的另一个边沿锁存到移位寄存器。如果CLOCK PHASE位是1.数据的发送和传输就要在SPICLK跳变之前的半个周期发生。主控制器可以在任一时刻启动数据发送.因为它控制着SPICLK信号。由软件决定了主控制器如何检测从控制器何时准备发送数据,以启动SPI传送数据。

图1 SPI内部结构

2.2 SPI设计原理

SPI接口是同步串行总线的一种,在同步时钟信号SCK下,能够高速、可靠的传送数据。它分为主从(MASTER/SLAVER)两种传输模式。主模式下的发送总线即是从模式的接收总线:与之对应的是从模式下的发送总线即是主模式的接收总线。它们可以同时接收和发送数据.而且发送和接收操作可以通过中断或者查询方法来完成。

2.2.1工作时钟

时钟极性CPOL和时钟相位CPHA控制着时钟信号引脚上4中不同的时钟方式。在设备被使能激活后.还未进行数据传输时或两个字节数据间歇期间,SCK处于空闲电平,通过时钟极性控制位可以选择此空闲电平的电平时0还是1:时钟相位控制位用来选择数据接收端设备的采样时刻。在该采样时刻,线上数据必须同时满足建立时间和保持时间两个参数,因此数据发送端设备应提前将数据移出到数据线上。

4种不同的时钟方式能根据外设需要,能够提供相对应的传输协议来完成数据的传输工作。它们之间没有优先级.SPI线上的主从设备必须根据具体情况设置匹配的传输时序模式.时序只有匹配擞据传输才能正常进行。如果设置的不匹配.可能导致数据接收方和发送方在同一个时钟沿作用.导致数据输出失败。

图2是CPHA=0时的数据传输时序.它同时包含了CPOL=0和CPOL=1的情况,当CPOL=O时,要传输的数据在时钟信号没有延时且上升沿出发送,在时钟信号下降沿处接收数据。当CPOL=1时,同样在没有延时的情况下传输,不同的是下降沿发送数据,上升沿接收。图3是CPHA=1时数据传输时序。与图2相似,但采样时刻延迟了半个周期。

DSP(数字信号处理)的优势除了处理复杂的运算,特别适用于数字滤波、语音、视频、图象处理、通信以及高速实时测控系统中已成为现代信息处理技术的重要器件,极大地促进了信号处理和测控各个领域的学术研究、产品开发及应用。TI公司TMS320LF2407是一种专用定点DSP芯片,与以往的产品相比.最大不同就是有丰富的外设.像SCI、SPI、EV等等.在处理数据优势上添加了事务管理能力。

其中串行外设接口(Serial Peripheral Interface)是Motorola公司提出的一种同步串行外围接口协议.主要应用在EEPROM、FLASH、实时时钟、AD转换器.还有数字处理和数字解码器之间。包括主/从2种模式,具有I/O资源占用少、协议实现简单、传输速度快、能够同时收发信息、支持绝大部分处理器芯片等优点,是一种高速的全双工、同步的通信总线,并且在芯片的管脚上只占用四根线,节约了芯片的管脚.同时为PCB的布局上节约了空间,提供了方便,正是出于这种简单易用的特性,TMS320LF2407芯片也集成了这种通信协议。

2 SPI接口结构和设计原理

2.1 SPI接口结构

该SPI设计主要有两大部分组成:微控制器接口和SPI控制接口。通过控制线、数据线、和地址线三大总线把微控制接口与SPI控制接口连接在一起,如果外部有更多的SPI接口模块。可以由SPI控制接口运用软件编程与设置,实现扩展具有SPI接口的外部设备。

TMS320LF2407中采用的主从控制器连接通信。主控制器通过输出SPICLK信号来启动数据传送。对主控制器和从控制器.数据都是在SPICLK的一个边沿移出移位寄存器,并在相对的另一个边沿锁存到移位寄存器。如果CLOCK PHASE位是1.数据的发送和传输就要在SPICLK跳变之前的半个周期发生。主控制器可以在任一时刻启动数据发送.因为它控制着SPICLK信号。由软件决定了主控制器如何检测从控制器何时准备发送数据,以启动SPI传送数据。

图1 SPI内部结构

2.2 SPI设计原理

SPI接口是同步串行总线的一种,在同步时钟信号SCK下,能够高速、可靠的传送数据。它分为主从(MASTER/SLAVER)两种传输模式。主模式下的发送总线即是从模式的接收总线:与之对应的是从模式下的发送总线即是主模式的接收总线。它们可以同时接收和发送数据.而且发送和接收操作可以通过中断或者查询方法来完成。

2.2.1工作时钟

时钟极性CPOL和时钟相位CPHA控制着时钟信号引脚上4中不同的时钟方式。在设备被使能激活后.还未进行数据传输时或两个字节数据间歇期间,SCK处于空闲电平,通过时钟极性控制位可以选择此空闲电平的电平时0还是1:时钟相位控制位用来选择数据接收端设备的采样时刻。在该采样时刻,线上数据必须同时满足建立时间和保持时间两个参数,因此数据发送端设备应提前将数据移出到数据线上。

4种不同的时钟方式能根据外设需要,能够提供相对应的传输协议来完成数据的传输工作。它们之间没有优先级.SPI线上的主从设备必须根据具体情况设置匹配的传输时序模式.时序只有匹配擞据传输才能正常进行。如果设置的不匹配.可能导致数据接收方和发送方在同一个时钟沿作用.导致数据输出失败。

图2是CPHA=0时的数据传输时序.它同时包含了CPOL=0和CPOL=1的情况,当CPOL=O时,要传输的数据在时钟信号没有延时且上升沿出发送,在时钟信号下降沿处接收数据。当CPOL=1时,同样在没有延时的情况下传输,不同的是下降沿发送数据,上升沿接收。图3是CPHA=1时数据传输时序。与图2相似,但采样时刻延迟了半个周期。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章